#### **Vertical Nanowire High-Frequency Transistors**

Johansson, Sofia

2014

#### Link to publication

Citation for published version (APA): Johansson, S. (2014). Vertical Nanowire High-Frequency Transistors. [Doctoral Thesis (compilation), Department of Electrical and Information Technology].

Total number of authors:

#### General rights

Unless other specific re-use rights are stated the following general rights apply:

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

• Users may download and print one copy of any publication from the public portal for the purpose of private study

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal

Read more about Creative commons licenses: https://creativecommons.org/licenses/

#### Take down policy

If you believe that this document breaches copyright please contact us providing details, and we will remove access to the work immediately and investigate your claim.

## Vertical Nanowire High-Frequency Transistors

Doctoral Thesis Sofia Johansson

Department of Electrical and Information Technology Faculty of Engineering, Lund University Lund, Sweden 2014

Department of Electrical and Information Technology Lund University P.O. Box 118 SE-221 00 Lund, Sweden

#### © Sofia Johansson

ISSN: 1654-790X, No. 61

ISBN: 978-91-7623-034-3 (printed version) ISBN: 978-91-7623-035-0 (pdf version)

Printed in Lund, Sweden, by Tryckeriet I E-huset

September 2014

## **Abstract**

This thesis explores a novel transistor technology based on vertical InAs nanowires, which could be considered both for low-power high-frequency analog applications and for replacing Si CMOS in the continued scaling of digital electronics. The potential of this device - the vertical InAs nanowire MOSFET – lies in the combination of the outstanding transport properties of InAs and the improved electrostatic control of the gate-all-around geometry.

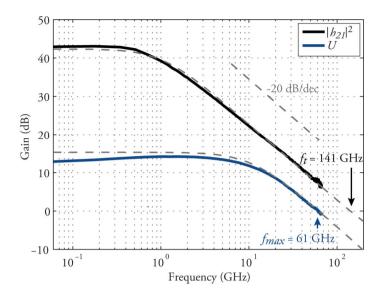

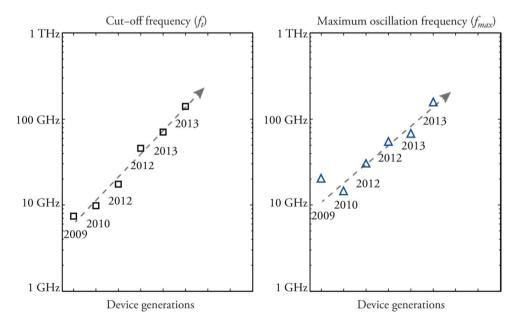

Three generations of the vertical InAs nanowire MOSFET are presented in this thesis; the first generation, integrated on semi-insulating InP substrate, provided the first RF measurements on vertical nanowire transistors with extrinsic  $f_{\parallel}/f_{max} > 7/20$  GHz. Utilizing the resilience towards dislocations inherent to the vertical nanowire growth, the second generation is integrated on highly resistive Si substrates by a thin InAs buffer layer. The RF performance is comparable to the first generation, indicating sustained crystal quality of the nanowires. In the third generation, however, a great boost in the RF performance is achieved by removing excess metal overlap and, hence, reducing the parasitic gate capacitance, which resulted in extrinsic  $f_{\parallel}/f_{max} = 141/155$  GHz at  $L_g \approx 150$  nm.

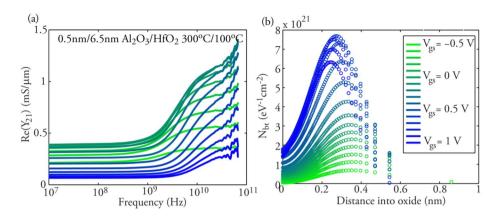

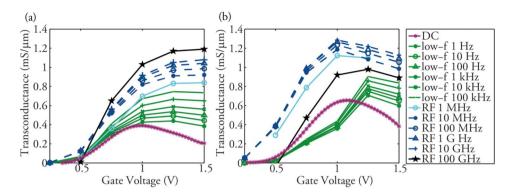

The main challenge for III-V MOSFETs is the high- $\kappa$  integration as high densities of charge traps deteriorate the device performance. Focusing on the border traps, a method based on frequency dispersion in  $g_m$  (1 Hz-100 GHz) is developed for direct measurement of the trap density as a function of distance from the oxide-semiconductor interface. The method is demonstrated for vertical InAs nanowire MOSFETs and surface-channel InGaAs MOSFETs.

# Contents

| Pop  | ulärvete | nskaplig Sammanfattning                                                                                                                                       | 1                    |  |

|------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|--|

| Pref | face and | List of Papers                                                                                                                                                | 5                    |  |

| 1.   | Back     | Background                                                                                                                                                    |                      |  |

|      | 1.1      | The Metal-Oxide-Semiconductor Field-Effect Transistor 1.1.1 Basic transistor operation 1.1.2 Output and transfer characteristics 1.1.3 High-frequency metrics | 10<br>10<br>12<br>14 |  |

|      | 1.2      | III-V Semiconductors                                                                                                                                          | 16                   |  |

|      | 1.3      | Non-Planar Transistor Geometries                                                                                                                              | 18                   |  |

|      | 1.4      | Applications of Vertical InAs Nanowire MOSFETs                                                                                                                | 20                   |  |

|      | 1.5      | High- $\kappa$ Dielectrics on III-Vs<br>1.5.1 High- $\kappa$ versus native oxide<br>1.5.2 Interface traps and border traps                                    | 21<br>21<br>22       |  |

| 2.   | Devi     | ce Fabrication                                                                                                                                                | 25                   |  |

|      | 2.1      | Nanowire Growth                                                                                                                                               |                      |  |

|      | 2.2      | Gate-All-Around                                                                                                                                               |                      |  |

|      | 2.3      | RF Compatible Design                                                                                                                                          |                      |  |

|       | 2.4                    | Three (                                             | Generations of Vertical InAs Nanowire MOSFETs                                                                                                                                                                    | 28                               |

|-------|------------------------|-----------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

|       |                        | 2.4.1                                               | Generation 1 - on semi-insulating InP substrate                                                                                                                                                                  | 30                               |

|       |                        | 2.4.2                                               | Generation 2 - on highly resistive Si substrates                                                                                                                                                                 | 31                               |

|       |                        | 2.4.3                                               | Generation 3 - with reduced metal overlap                                                                                                                                                                        | 33                               |

| 3.    | Electrical Performance |                                                     |                                                                                                                                                                                                                  |                                  |

|       | 3.1                    | DC Ch                                               | naracterization                                                                                                                                                                                                  | 39                               |

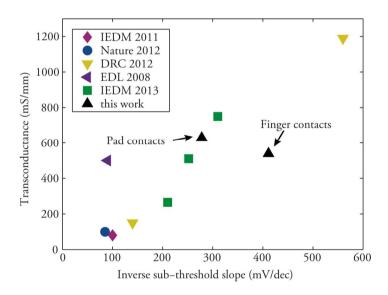

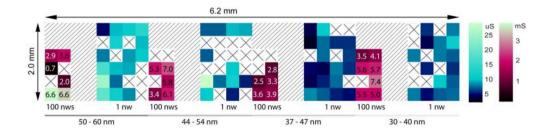

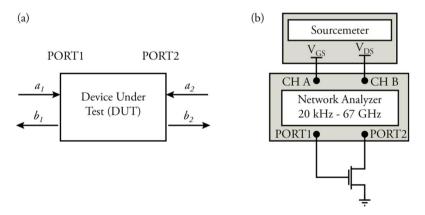

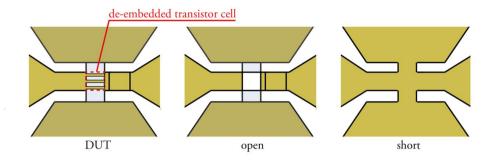

|       | 3.2                    | High-F<br>3.2.1<br>3.2.2<br>3.2.3<br>3.2.4<br>3.2.5 | Frequency Characterization Scattering parameter measurements Cut-off frequency and maximum oscillation frequency Small-signal modelling Reduced parasitic capacitance Benchmarking of RF performance             | 42<br>42<br>44<br>45<br>51<br>53 |

|       | 3.3                    | Tempe                                               | rature and Annealing Effects                                                                                                                                                                                     | 55                               |

| 4.    | Chara                  | octerizatio                                         | on of Border Traps                                                                                                                                                                                               | 57                               |

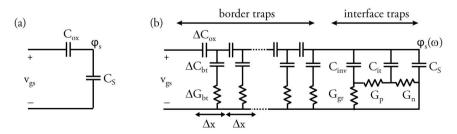

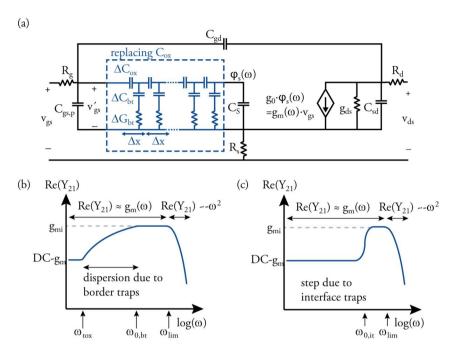

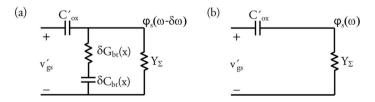

|       | 4.1                    | Traps a                                             | as an <i>RC</i> Network                                                                                                                                                                                          | 57                               |

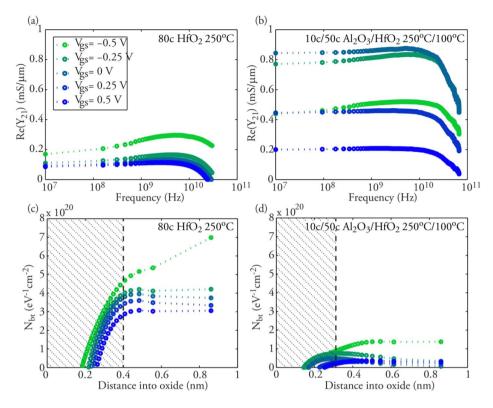

|       | 4.2                    | The A0<br>4.2.1<br>4.2.2<br>4.2.3<br>4.2.4          | Transconductance Method Analytical expression for $N_{bl}(x)$ $N_{bl}(x)$ in InAs nanowire MOSFETs with different high- $\kappa$ Border traps in surface-channel InGaAs MOSFETs Effects of InP interfacial layer | 59<br>61<br>64<br>65<br>66       |

| 5.    | Conc                   | lusion an                                           | nd Outlook                                                                                                                                                                                                       | 69                               |

| Appe  | endix - I              | Processin                                           | ng Recipes                                                                                                                                                                                                       | 71                               |

| Ackn  | owledg                 | ements                                              |                                                                                                                                                                                                                  | 79                               |

| Refer | ences                  |                                                     |                                                                                                                                                                                                                  | 81                               |

# Populärvetenskaplig Sammanfattning

Minns du din första dator? Kanske köpte familjen den på avbetalning genom jobbet för 20 000 kr och kanske kan du såhär i efterhand tycka att effektförbrukningen var lite väl hög i relation till datorns prestanda. Den gick t.ex. inte att köra på batteri. Detta är ganska långt ifrån dagens datorer, smart-TV, smarta telefoner och surfplattor där vi kan streama filmer och musik. Den förhöjda datorkraften har givetvis haft en enorm påverkan på samhället och hur man arbetar. Forskningen är inget undantag. Nu är vi på väg in i nästa era som brukar benämnas *Sakernas internet* eller *Molnet*. Karakteristiskt för denna era är att en uppsjö av prylar kopplas till trådlösa nätverk: skidglasögon, husväggar, din puls... Bara fantasin sätter gränserna. Detta ställer grundläggande elektroniska komponenten – transistorn.

För varje generation av transistorer finns det tre kriterier som måste uppfyllas. De måste vara snabbare, ta upp mindre yta på chipet och förbruka mindre effekt. Från 1970 till ungefär 2003 skedde denna utveckling exponentiellt. Antalet komponenter per chip dubblades ungefär vartannat år. Men idag verkar det som att kiselteknologin som dominerat marknaden ända sedan 70-talet inte längre kan leverera snabbare och strömsnålare transistorer i den takt marknaden vant sig vid. Samtidigt är kraven som ställs på transistorerna från *Sakernas internet* mycket mer diversifierade än tidigare då transistorns användningsområde var mer begränsat. Behovet av att undersöka alternativa teknologier är därför större än någonsin och det är här min forskning kommer in.

I denna avhandling beskrivs en teknologi skiljer sig från kiselteknologin huvudsakligen i två avseenden. För det första är transistorerna inte gjorda i kisel (Si) utan i indiumarsenid (InAs). Valet grundar sig i hur elektronerna rör sig i de olika

materialen. I indiumarsenid är elektronerna mer rörliga och kan nå högre hastigheter än i kisel vilket i slutändan leder till snabbare transistorer.

Den andra stora skillnaden är geometrin. Kiselteknologin baserar sig traditionellt på en plan yta där en transistor skapas då man lägger tre kontakter på denna yta. Strömmen mellan två av kontakterna (source och drain) kontrolleras med hjälp av den tredje kontakten (gate). Mer specifikt styrs styrkan på det elektriska fältet under gaten genom att en spänning läggs på och därigenom förändras potentialen för laddningar som rör sig mellan source och drain. För att det inte ska gå för stora strömmar genom gaten brukar man isolera denna med ett tunt oxidskikt. Jag tillverkar samma typ av transistor men utgår ifrån vertikala nanotrådar istället för en plan yta. På de avlånga nanotrådarna med en diameter på ca 40 nm och en längd på ca 500 nm placeras de tre kontakterna vertikalt ovanpå varandra.

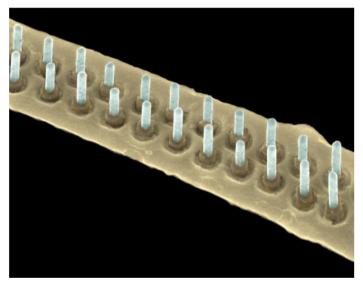

Nanotrådstransistorerna kontrolleras flera gånger under tillverkningsprocessen. Denna bild visar gatekontakten (i gult) som omsluter nanotrådarna. Bilden är färglagd i efterhand och tagen snett uppifrån med ett elektronmikroskop.

Eftersom gaten kopplar hela vägen runt nanotråden kan laddningarna inne i den styras på ett effektivare sätt än i en plan transistor vilket förbättrar möjligheterna att skala ner transistor-storleken. Detta har länge varit känt men många har tyckt att det är ett för stor förändring att byta geometri eftersom man redan investerat väldigt mycket pengar i den befintliga tillverkningsmetoden. Det var därför en sensationell nyhet när det ledande företaget inom transistortillverkning, Intel, år 2011 offentliggjorde att de frångått plana transistorer till förmån för en slags liggande kiselnanotrådar med gate-kontakter som påverkar kanalen både uppifrån och från sidorna. Vertikala nanotrådarstransistorer skiljer sig ännu mer från de plana

transistorerna, men en sådan transistor kräver teoretiskt sett inte lika stor yta. Dessutom kan kristalltillväxten av vertikala nanotrådar vara väldigt förlåtande och ge ett högkvalitativt material även om man till exempel ändrar sammansättningen eller låter indiumarsenid-nanotrådar växa på kiselplattor.

År 2009, när arbetet i detta avhandlingsarbete påbörjades, fanns det väldigt få rapporter om hur snabba nanotrådstransistorer egentligen är. För att kunna mäta detta på ett trovärdigt och lättolkat sätt utvecklades en tillverkningsprocess där varje transistor, bestående av i storleksordningen 100 nanotrådar, isolerades från de övriga transistorerna. Det visade sig att strömmar kunde förstärkas upp till 7 GHz. För högre frekvenser hängde transistorn inte med. Efter ytterligare processutveckling kunde en enklare form av nanotrådstransistor på kiselsubstrat presenteras med en brytfrekvens på 9 GHz. Även om båda dessa rapporter var världsrekord för vertikala nanotrådarstransistorer kunde vi inte vara helt nöjda. Det var nämligen tydligt från transistormodelleringen att det var kontakterna, och inte nanotrådarna, som begränsade prestandan. I den nyaste versionen av nanotrådstransistorn är kontakterna omdesignade och brytfrekvensen har ökat till 140 GHz. I och med detta resultat har vi visat att den vertikala nanotrådstransistorn är en kandidat att räkna med för applikationer som kräver höga frekvenser.

Den största utmaningen för den här typen av transistorer som baseras på andra halvledarmaterial än kisel är det stora antalet defekter i oxidskiktet under gatekontakten. Dessa defekter kan hålla fast laddningar som egentligen skulle ha rört sig mellan source och drain, och därigenom ökar transistorns effektförbrukning. De elektriska följdverkningarna har varit synliga i de högfrekvens-mätningar som gjorts på nanotråds-transistorerna och plana transistorer av liknande material och från detta har vi utvecklat en metod där oxidens defekt-densitet kan bestämmas direkt från transistormätningar. Speciellt för metoden är också att mätningar gjorts i ett väldigt stort frekvensintervall – från 1 Hz till 100 GHz (= 100 000 000 000 Hz).

Under min tid som doktorand har jag bytt institution från Fysik till Elektro- och Informationsteknik och man skulle kunna säga att nanotråds-transistorn har gjort detsamma: att den nu är ett steg närmare tillämpad användning.

## Preface and List of Papers

This thesis summarizes my academic work for a Doctoral degree in Electrical Engineering. The work has been done within the Nanoelectronics group at the division of Solid State Physics (FTF), Lund University, and at the department of Electrical and Information Technology (EIT), Lund University.

My work includes device fabrication, electrical characterization and modeling. However, the epitaxial growth in the papers was performed by Sepideh Gorji Ghalamestani, Mattias Borg, Johannes Svensson, Jun Wu, and Elvedin Memisevic and the device processing of planar InGaAs transistors was performed by Jiongjiong Mo, and Erik Lind. This experimental work is, hence, not included in the thesis.

The first part of this thesis serves as an introduction to the work for a reader with some knowledge in semiconductor and device physics. In the second part, the included papers, which are listed in the following section, are appended.

### List of Included Papers

I. Vertical InAs nanowire wrap gate transistors with  $f_t > 7$  GHz and  $f_{max} > 20$  GHz

M. Egard, <u>S. Johansson</u>, A.-C. Johansson, K.-M. Persson, A. W. Dey, B. M. Borg, C. Thelander, L.-E. Wernersson, and E. Lind, Nano Letters, vol. 10, no. 3, pp. 809-812, 2010.

I developed the process scheme and fabricated the devices together with A.-C. J., I did the RF characterization together with M. E., I did the DC characterization, and wrote parts of the paper.

- II. RF characterization of vertical InAs nanowire wrap-gate transistors integrated on Si substrates

- <u>S. Johansson</u>, M. Egard, S. G. Ghalamestani, B. M. Borg, M. Berg, L.-E. Wernersson, and E. Lind, IEEE Transactions on Microwave Theory and Techniques, vol. 59, no. 10, pp. 2733-2738, 2011.

- I fabricated the device and did the DC characterization. I did the RF characterization together with M. E., and I was the main author of the paper.

- III. Uniform and position-controlled InAs nanowires on 2" Si substrates for transistor applications

- S. Gorji Ghalamestani, <u>S. Johansson</u>, M. B. Borg, E. Lind, K. A. Dick, and L.-E. Wernersson, Nanotechnology, vol. 23, no. 1, p. 015302 (7pp), 2011.

- I did the pre-growth processing of the 2" substrate and participated in the analysis of the growth. I fabricated the transistors, did the DC and RF characterization and wrote parts of the paper.

- IV. Temperature and annealing effects on InAs nanowire MOSFETs

- S. Johansson, S. Gorji Ghalamestani, M. Borg, E. Lind, and L.-E. Wernersson, Microelectronic Engineering, vol. 88, no. 7, pp. 1105-1108, 2011.

- I fabricated the devices, did the measurements, data analysis, and wrote the paper.

- V. A high-frequency transconductance method for characterization of high- $\kappa$  border traps in III-V MOSFETs

- <u>S. Johansson</u>, M. Berg, K.-M. Persson, and E. Lind, IEEE Transactions on Electron Devices, vol. 60, no. 2, pp. 776-781, 2013.

- I developed the method and did the data analysis together with E. L., I did the measurements and wrote the paper.

- VI. Characterization of border traps in III-V MOSFETs using an RF transconductance method

- S. Johansson, J. Mo, and E. Lind, 2013 Proceedings of the European Solid-State Device Research Conference (ESSDERC), pp. 53-56, 2013.

- I developed the method and did the data analysis together with E. L., I did the measurements and wrote the paper.

- VII. High-frequency gate-all-around vertical InAs nanowire MOSFETs on Si substrates

- S. Johansson, E. Memisevic, L.-E. Wernersson, and E. Lind, IEEE Electron Device Letters, vol. 35, no. 5, pp 518-520, 2014.

I developed the process, fabricated the device, did the DC and RF characterization, and, wrote the paper.

### List of Related Papers

During my PhD studies I have also contributed to the papers listed below. These papers are not included in this thesis either due to overlapping content or because the content is beyond the scope of this thesis.

- viii. High frequency performance of vertical InAs nanowire MOSFET

- E. Lind, M. Egard, <u>S. Johansson</u>, A.-C. Johansson, B. M. Borg, C. Thelander, K.-M. Persson, A. W. Dey, and L.-E. Wernersson, in Proceeding of the International Conference on Indium Phosphide & Related Materials (IPRM), 2010.

- ix. Highly controlled InAs nanowires on Si(111) wafers by MOVPE

- S. G. Ghalamestani, <u>S. Johansson</u>, B. M. Borg, K. A. Dick, and L.-E. Wernersson, Physica Status Solidi (c), vol. 9, no. 2, pp. 206-209, 2012.

- x. High frequency vertical InAs nanowire MOSFETs integrated on Si substrates

- <u>S. Johansson</u>, S. G. Ghalamestani, M. Egard, M. Borg, M. Berg, L.-E. Wernersson, and E. Lind, Physica Status Solidi (c), vol. 9, no. 2, pp. 350-353, 2012.

- xi. (Invited) Extraction of oxide traps in III-V MOSFETs using RF transconductance measurements

- E. Lind, and <u>S. Johansson</u>, ECS transactions, vol. 52, no. 1, pp. 415-419, 2013.

- xii. Extrinsic and intrinsic performance of vertical InAs nanowire MOSFETs on Si substrates

- K.-M. Persson, M. Berg, M. B. Borg, W. Jun, <u>S. Johansson</u>, J. Svensson, K. Jansson, E. Lind, and L.-E. Wernersson, IEEE Transactions on Electron Devices, vol. 60, no. 9, pp. 2761-2767, 2013.

- xiii. RF and defect analysis of stressed III-V MOSFET G. Roll, E. Lind, M. Egard, <u>S. Johansson</u>, L. Ohlsson, and L.-E.Wernersson, IEEE Electron Device Letters, vol. 35, no. 2, pp. 181-183, 2014.

- xiv. RF reliability of gate last InGaAs nMOSFETs with high- $\kappa$  dielectric

- G. Roll, M. Egard, <u>S. Johansson</u>, L. Ohlsson, L.-E. Wernersson, and E. Lind, IEEE International Integrated Reliability Workshop Final Report (IRW), pp. 38-41, 2013.

- xv. RF characterization of vertical InAs nanowire MOSFETs with  $f_t$  and  $f_{max}$  above 140 GHz

- <u>S. Johansson</u>, E. Memisevic, L.-E. Wernersson, E. Lind, Proceeding of the International Conference on Indium Phosphide & Related Materials (IPRM), 2014.

## 1. Background

In 1947, the revolution of electronics began when the first transistor was invented by John Bardeen and Walter Brattain at Bell Labs [1, 2]. The overwhelming progress seen during the last 50 years, especially in Si complementary metal-oxidesemiconductor (CMOS) technology, is driven by Gordon Moore's prediction from 1965 that the number of components on integrated circuits would double roughly every two years [3]. An exponential increase in the number of transistors is accomplished to a large extent by geometrical down-scaling. In addition to a reduced cost per transistor, this has led to exponential increase in clock-frequency and an exponential decrease in the power consumed by each transistor. At least this was true until about 2003 when CMOS entered an era of power-constrained scaling as the power dissipation reached 100 W/cm<sup>2</sup> and the transistor speed had to be compromised to avoid overheating [4]. It is evident that scaling of CMOS becomes more and more difficult. Some major changes have already been introduced to the Si CMOS technology, for example the SiO<sub>2</sub>/polysilicon gate has been replaced by a high- $\kappa$  dielectric/metal gate and the planar geometry has been abandoned in favor of tri-gate geometry.

Simultaneously, a diverse future is anticipated as an era referred to as the Internet of Things (IoT) is entered [5]. Here, computing devices find new applications in all parts of our society. The use will mainly be in wireless communication between objects and collection of data rather than human-to-human communication. The number of computing devices per capita is expected to increase exponentially and the specifications that need to be met by different transistor technologies will become much more diversified. On the wish list are for instance disposable sensors and energy-harvesting devices with short or long range wireless communication. Hence, the need for research on new transistor technologies is greater than ever before.

This chapter provides an introduction to the field by first presenting some aspects of the metal-oxide-semiconductor field-effect transistor (MOSFET). This is followed by

a background to the choice of material and geometry in the vertical InAs nanowire transistor and a discussion on possible applications for this device. Finally, one of the main challenges for III-V MOSFETs, *i.e.* traps in the gate oxide, is introduced.

# 1.1 The Metal-Oxide-Semiconductor Field-Effect Transistor

The following text introduces the basic operation of a metal-oxide-semiconductor field-effect transistor (MOSFET) and some important metrics used to characterize its electrical performance. The metrics are later used for benchmarking, but needs to be considered already when designing the transistor. For a more thorough description of the physics behind conventional MOSFET operation, the reader is referred to one of the excellent books on the topic [6, 7].

#### 1.1.1 Basic transistor operation

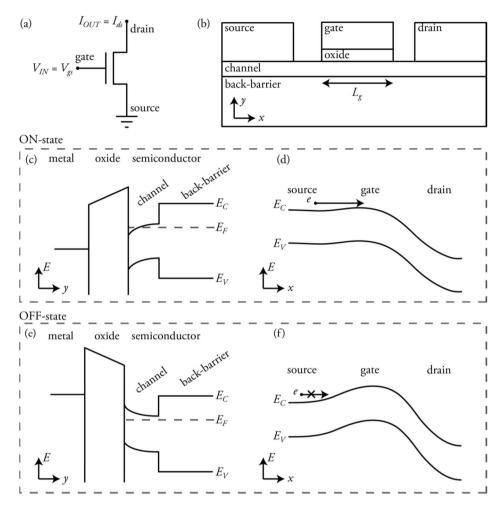

Transistors are three terminal devices used either for on/off switching, in *e.g.* logic applications, or signal amplification. Figure 1.1a presents a MOSFET in commonsource configuration where an input signal,  $V_{IN}=V_{gs}$ , is applied to the gate terminal and an output signal,  $I_{OUT}=I_{ds}$ , is received at the drain terminal. The specific case treated in this thesis is a junction-less MOSFET with n-type doping in the semiconductor channel. A schematic structure is presented in figure 1.1b. If a negative gate voltage,  $V_{gs}$ , is applied to the gate, the current from drain-to-source,  $I_{ds}$ , is turned off since the electric field created underneath the gate repels electrons and deplete the channel.

Characteristic for the MOSET is the metal-oxide-semiconductor (MOS) structure of the gate where an oxide or dielectric material is inserted between the gate metal and the semiconductor channel. The reduction of the gate-to-source leakage current,  $I_{gs}$ , accomplished by the insertion of the oxide is one important reason why the MOSFET is suitable for low-power applications.

The ON-state and OFF-state of an n-type transistor are illustrated by band diagrams in figure 1.1c-f. When a voltage is applied to the gate, the bands of the semiconductor bend and electrons are either accumulated or depleted underneath the gate depending on the bias. For the junction-less channel, accumulation turns the transistor on and depletion turns the transistor off, see figure 1.1c and e. This is opposite to the operation of an inversion mode transistor, exemplified by the ordinary Si MOSFET, which has the opposite doping type in the channel underneath the gate as compared to the source and drain regions of the transistor. Here, the charge in the channel is

**Figure 1.1:** A junction-less n-type MOSET illustrated by (a) its circuit representation in commonsource configuration, (b) a schematic cross-section where  $L_g$  is the gate length, and (c-f) band diagrams perpendicular to the channel and along the channel in the ON and OFF state where  $E_C$  is the conduction band edge and  $E_V$  is the valence band edge.

inverted to turn the transistor to the ON-state, *i.e.* the bands are bent beyond depletion until the majority charge carriers switch type from electrons to holes or vice versa.

The band diagrams along the channel are illustrated in figure 1.1 d and f. By applying a voltage between drain and source,  $V_{ds_i}$  electrons move from source to drain in the ON-state. In the OFF-state the electrons are hindered by the energy barrier of the gate and  $I_{ds}$  is limited to thermal emission over the barrier.

#### 1.1.2 Output and transfer characteristics

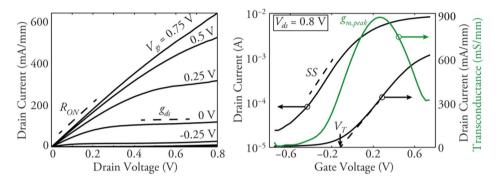

The DC characteristics of a transistor is obtained by either sweeping the gate voltage,  $V_{gs_1}$  at a constant drain voltage,  $V_{ds_1}$  which gives the transfer characteristics or sweeping  $V_{ds}$  at a constant  $V_{gs_1}$  which gives the output characteristics. For benchmarking of DC performance, a number of metrics that describe the shape of the curves in the output and transfer characteristic are defined. Experimental output and transfer characteristics from a vertical InAs nanowire MOSFET is used to illustrate the typical appearance of the two plots in figure 1.2.

**Figure 1.2:** Electrical data of a vertical InAs nanowire MOSFET in terms of (a) output characteristic at  $V_{as}$  from -0.75 V to 0.75 V in steps of 0.25 V and (b) transfer characteristics at  $V_{as}$  = 0.8 V.

Output characteristics: The output characteristics measure the  $V_{ds}$  dependence on  $I_{ds}$ . At low  $V_{ds}$ , the channel functions as a resistor with a linear dependence of  $I_{ds}$  on  $V_{ds}$  and with a resistance controlled by  $V_{gs}$ . When  $V_{ds}$  is increased  $I_{ds}$  saturates as the current becomes limited by the amount of available electrons and their maximum velocity, i.e. the saturation velocity,  $V_{sat}$ , for short channel devices limited by scattering, and the injection velocity,  $V_{inj}$ , in ballistic regime. The amount of available electrons is controlled by  $V_{gs}$ .

Drive current: A high  $I_{ds}$  in the ON-state, *i.e.* a high normalized drive current, is desirable as this relates to the speed at which the transistor can be operated.  $I_{ds}$  is usually normalized to the width of the gate,  $W_i$  and is expressed in mA/mm.

On-resistance: In the linear region of the output characteristics,  $I_{ds}$  is limited by the on-resistance,  $R_{ON}$ , which is obtained by the inverse slope  $dV_{ds}/dI_{ds}$  in the output characteristics at low  $V_{ds}$ , see figure 1.2a.  $R_{ON}$  is comprised of resistances in the source and drain,  $R_s$  and  $R_{ds}$ , and the resistance in the channel,  $R_{ds}$  as

$$R_{ON} = R_s + R_d + R_{ch} \approx R_s + R_d$$

. (1.1)

It should be noted that  $R_{ch}$  is small for short channel devices at high  $V_{gn}$  and can in this case be omitted in equation 1.1.

Output conductance: The output conductance,  $g_{ds_i}$  measures how well  $I_{ds}$  saturates. Its value is deduced as the slope in the saturation region, *i.e.*  $dI_{ds}/dV_{ds}$  at medium or high  $V_{ds_i}$  see figure 1.2a. A small  $g_{ds}$  is desired as this is related to a high voltage gain,  $A_V$ . In turn,  $A_V$  could be expressed either in terms of differential voltage or conductance as

$$A_{V} = \delta V_{ds} / \delta V_{as} = g_{m} / g_{ds}$$

(1.2)

where  $g_m$  is the transconductance which will be defined below when considering the transfer characteristics.

Transfer characteristics: The transfer characteristics measure the  $V_{gs}$  dependence of  $I_{ds}$ . In figure 1.2b,  $I_{ds}$  is plotted both on a linear and a logarithmic scale to illustrate different aspects of the switching from the OFF-state at low  $V_{gs}$  to the ON-state at high  $V_{gs}$ . Alternatively, the transfer characteristics shows the  $V_{gs}$  dependence of the transconductance,  $q_{gs}$ .

Transconductance: The definition of the transconductance is  $g_m = dI_{ds}/dV_{g_{S_1}}$  which means that it is a measure of how well the gate is able to control the current in the channel. Furthermore,  $g_m$  is an important metric for the speed of the transistor and is often represented by its peak value  $g_{m,peak}$ .

Threshold voltage: The threshold voltage,  $V_T$ , is in this thesis defined as the gate voltage at which the transistor switches between the ON-state and OFF-state. To extract  $V_T$  from experimental data, a support line may be drawn which is the tangent of  $I_{ds}$  at the  $V_{gs}$  corresponding to  $g_{m,peak}$ .  $V_T$  is the voltage where support line intersects with the x-axis, see figure 1.2b. Alternatively,  $V_T$  could be defined as the voltage at which  $I_{ON} = 100 \text{ nA/}\mu\text{m}$ .

Sub-threshold slope: In the sub-threshold region, *i.e.* below  $V_T$ ,  $I_{ds}$  increase exponentially with  $V_{gs}$  due to the energetic distribution of electrons in the conduction band of the semiconductor. Here,  $I_{ds}$  is limited by thermionic emission above the energy barrier induced by the gate voltage. The exponential increase is described by the inverse sub-threshold slope, SS. SS is deduced from the transfer characteristics in the region with the highest slope on the logarithmic scale, see figure 1.2b. For MOSFETs the lowest possible value is SS = 60 mV/decade at room temperature. This constrain on the sub-threshold slope for MOSFETs limits the theoretical minimum power consumptions since the power supply voltage cannot be further reduced without deteriorating the ON/OFF ratio. Therefore, alternative devices relying on other physical principles, such as tunnel FETs [8], are being investigated.

Moreover, two other phenomena that are sometimes visible in the output characteristics are impact ionization and band-to-band tunneling. The two can be difficult to distinguish from each other as both are characterized by a rapid increase in  $I_{ds}$  at high  $V_{ds}$ . In short, impact ionization occurs when the kinetic energy of the electrons is larger than the bandgap. Hence, the kinetic energy of one electron may generate an electron-hole pair. If the charge carriers continue to accelerate they may, in turn, generate even more electrons and holes and start an avalanche of charge carrier that increase  $I_{ds}$ . Typically, this occurs between gate and drain in figure 1.1d where the lateral electric field is strongest.

Band-to-band tunneling refers to electrons that tunnel from the valence band underneath the gate to the conduction band at the drain. The probability of tunneling increases exponentially when the voltage difference between gate and drain increases. Both phenomena are especially strong in small bandgap materials, such as InAs and InSb.

#### 1.1.3 High-frequency metrics

For benchmarking of the high-frequency performance, which also called radio frequency (RF) performance, two figures of merits are common: the unity current gain cut-off frequency,  $f_{t}$ , and the maximum oscillation frequency,  $f_{max}$ . These frequencies represent the highest frequencies at which the transistor can operate without attenuating the signal between input and output with respect to the current and power, respectively. More specifically,  $f_t$  is deduced as the frequency at which the current gain,  $h_{21}$ , equals unity. It should be noted that the decrease in current and power gain with frequency is related to increasing currents through the capacitive elements of the transistor with frequency. For an intrinsic transistor, *i.e.* a transistor without any parasitic resistances or parasitic capacitances and with  $g_{ds} = 0$ ,  $f_t$  can be calculated by

$$f_t = \frac{g_{mi}}{2\pi \cdot C_{qq\,i}} \tag{1.3}$$

where  $C_{gg,i}$  is the intrinsic gate capacitance and  $g_{mi}$  the intrinsic transconductance.

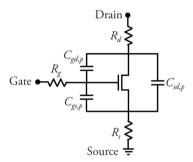

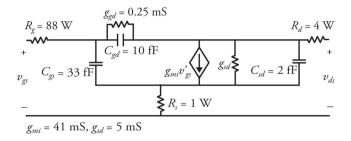

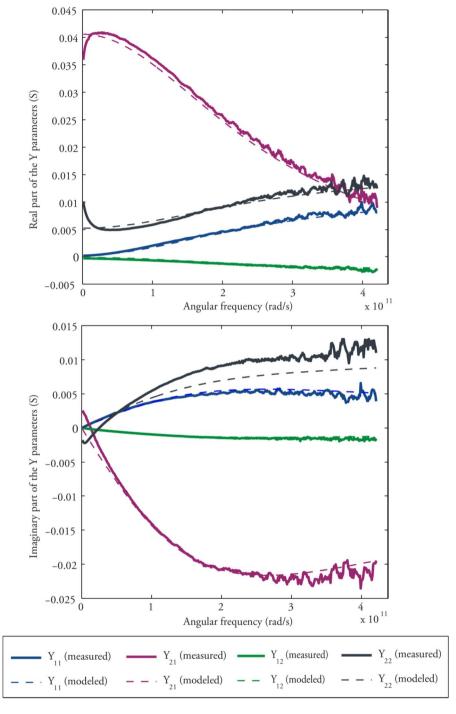

However, extrinsic performance that includes the parasitic impedances, originating from e.g. the contacts, gives a better representation of the real device performance. The addition of parasitic impedances to the intrinsic transistor is illustrated in figure 1.3. For an extrinsic transistor  $f_i$  is calculated by

$$\frac{1}{2\pi f_{t}} = \frac{C_{gg}}{g_{mi}} + \frac{C_{gg}}{g_{mi}} (R_{s} + R_{d}) g_{ds} + (R_{s} + R_{d}) \cdot C_{gd}$$

(1.4)

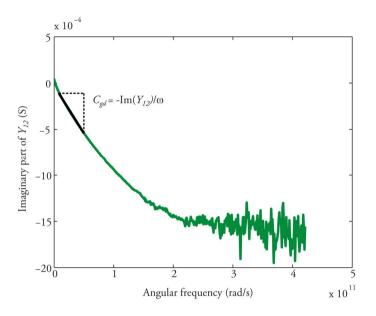

where  $C_{qq}$  is the total gate capacitance and  $C_{qd}$  is the total gate-drain capacitance.

**Figure 1.3:** An extrinsic MOSFET including the intrinsic device and the parasitic capacitances and resistances.  $R_{s_i}$   $R_{d_i}$  and  $R_{g}$  are the source, gate and, drain resistances, while  $C_{gs,p_i}$   $C_{gd,p_i}$  and  $C_{sd,p}$  are the parasitic gate-source, gate-drain, and source-drain capacitances.

For clarity, the following relationships are established where  $C_{gd,p}$  is the parasitic gatedrain capacitance,  $C_{gs,p_i}$  is the parasitic gate-source capacitance, and  $C_{gs}$  is the total gate-source capacitance:

$$C_{gg} = C_{gg,i} + C_{gd,p} + C_{gs,p}$$

(1.5)

$$C_{gg} = C_{gd} + C_{gs} \tag{1.6}$$

Furthermore,  $f_{max}$  is the frequency at which the Mason's unilateral power gain, U, equals unity. Here, U represents the power gain if a lossless passive feed-back network is added that gives complete reverse isolation. This means that any possible feed-back from the drain terminal to the gate terminal is not included when extracting U. The amount of feed-back sets the stability of the transistor and an alternative way to deduce  $f_{max}$  is to study the maximal stable gain (MSG) and maximal available power gain (MAG). In this case, MSG is used for frequencies where the device is potentially unstable and MAG for frequencies where the device is unconditionally stable. Both U and MSG/MAG give the same  $f_{max}$ . If  $f_{max}$  is instead calculated from simulated or extracted parameters, the following equation is used

$$f_{\text{max}} = \sqrt{\frac{f_t}{8\pi \cdot R_g C_{gd} \left[ 1 + \left( \frac{2\pi f_t}{C_{gd}} \right) \Psi \right]}}$$

(1.7a)

where

$$\Psi = (R_s + R_d) \frac{C_{gg}^2 g_{ds}^2}{g_m^2} + (R_s + R_d) \frac{C_{gg} C_{gd} g_{ds}}{g_m} + \frac{C_{gg}^2 g_{ds}}{g_m^2}$$

(1.7b)

and where  $R_g$  is the gate resistance. The second term in the square parenthesis in equation 1.7a is often small, provided that  $g_{ds}$  is small, and neglecting this term gives a simplified equation for  $f_{max_0}$

$$f_{\text{max}} \approx \sqrt{\frac{f_t}{8\pi \cdot R_g C_{gd}}}$$

(1.8)

More details on measurements and modeling of the high-frequency performance are presented in chapter 3.2.

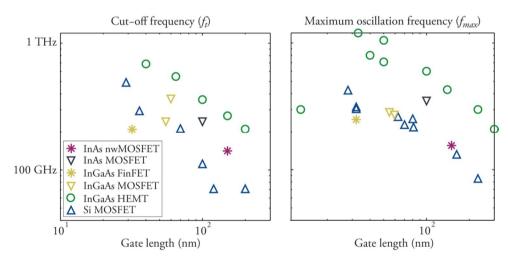

#### 1.2 III-V Semiconductors

III-V semiconductors (III-Vs) are compounds of elements in what was previously known as group III and V, and what is today known as group 13 and 15, of the periodic table. These materials have caught a lot of attention throughout the history of transistors due to their, in many cases, advantageous transport properties compared to Si. Today, III-V transistors such as GaAs and InGaAs metal-semiconductor field-effect transistors (MESFETs), hetero-junction bipolar transistors (HBT), and high electron mobility transistors (HEMTs) are widely used in RF systems and for wireless communication. Furthermore, III-V transistors demonstrate impressive RF performance; the record for  $f_t$  is held by a InP/InGaAs HBT with  $f_t$  = 765 GHz [9] and the record for  $f_{max}$  by a InGaAs/InP HEMTs with  $f_{max}$  above 1 THz [10].

One important parameter, when it comes to the transport properties, is the mobility,  $\mu$ . In table 1.1, the electron mobility,  $\mu_{e_i}$  and hole mobility,  $\mu_{h_i}$  are displayed for a few semiconductors. The highest  $\mu_e$  is found for InSb, InAs and InGaAs, which makes these materials suitable for n-type MOSFETs. The strongest candidates for p-type MOSFETs, with respect to  $\mu_{h_i}$  are Ge and GaSb. The general trend is that a high

mobility is associated with a narrow bandgap due to the small effective mass of the carriers.

In addition to the traditional semiconductors, two-dimensional materials, such as graphene, have received tremendous interest recent years. Graphene has very competitive mobilities in the order of about 70 000 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup> for both electrons and holes [11], but is inherently different in many ways compared to traditional semiconductors. For instance, graphene has the disadvantage that it lacks a bandgap,  $E_{g_t}$  which leads to a high  $g_{ds}$  and, hence, a low  $f_{max}$  as compared to  $f_t$  [12]. Why  $f_{max}$  is reduced by a high  $g_{ds}$  can be understood by revisiting equation 1.7.

|                        | $E_g$ (eV) | $\mu_e$ (cm <sup>2</sup> V <sup>-1</sup> s <sup>-1</sup> ) | $\mu_{\rho}$ (cm <sup>2</sup> V <sup>-1</sup> s <sup>-1</sup> ) | m <sub>e</sub> /m <sub>0</sub> | <i>a</i> <sub>0</sub> (Å) |

|------------------------|------------|------------------------------------------------------------|-----------------------------------------------------------------|--------------------------------|---------------------------|

| Si                     | 1.12       | 1 400                                                      | 450                                                             | 0.36                           | 5.43                      |

| Ge                     | 0.66       | 3 900                                                      | 1 900                                                           | 0.22                           | 5.66                      |

| GaAs                   | 1.42       | 8 500                                                      | 400                                                             | 0.063                          | 5.65                      |

| $In_{0.53}Ga_{0.47}As$ | 0.74       | 12 000                                                     | 300                                                             | 0.041                          | 5.87                      |

| InAs                   | 0.35       | 40 000                                                     | 500                                                             | 0.023                          | 6.06                      |

| InP                    | 1.34       | 5 400                                                      | 200                                                             | 0.08                           | 5.87                      |

| InSb                   | 0.17       | 77 000                                                     | 850                                                             | 0.014                          | 6.48                      |

| GaSb                   | 0.73       | 3 000                                                      | 1 000                                                           | 0.041                          | 6.10                      |

**Table 1.1:** Selected IV and III-V semiconductor material parameters, including the bandgap,  $E_{g_i}$ , the mobilities  $\mu_e$  and  $\mu_h$ , the lattice constant,  $a_0$ , and the effective mass used for calculations of density of states,  $m_{e_1}$  [13].  $m_e$  is normalized to the electron rest mass,  $m_0 = 9.11 \cdot 10^{-30}$  kg.

The choice of InAs, in this thesis, is a trade-off between high  $\mu_e$  and sufficient  $E_g$ . Furthermore, ohmic contacts are easily realized on InAs due to pinning of the Fermi-level in the conduction band.

Another important transport parameter is the injection velocity,  $v_{inj}$ , which is the carrier velocity at the virtual source, *i.e.* at the highest point of the conduction band for electrons as shown in figure 1.1d and f. As the gate length is scaled down, the transistors are gradually entering the ballistic regime where the length of the channel is shorter than the mean free path of the charge carriers and no scattering events occur under the gate. In this regime,  $I_{ON}$  is independent of the gate length and proportional to  $v_{inj}$ . Measurements on InAs and InGaAs HEMTs, has demonstrated  $v_{inj}$  of about  $2.8 \cdot 10^7 \text{ cm}^2 \text{s}^{-1}$  and  $2.3 \cdot 10^7 \text{ cm}^2 \text{s}^{-1}$ , respectively, at  $V_{ds} = 0.5 \text{ V}$  and  $L_g = 100 \text{ nm}$ . For Si MOSFETs, the values are substantially lower with  $v_{inj} \approx 0.9 \cdot 10^7 \text{ cm}^2 \text{s}^{-1}$  at  $L_g = 100 \text{ nm}$

and  $V_{ds}$  = 1.1-1.3 V [14]. It should be noted that  $V_{ds}$  is more than twice as high for the Si MOSFET in this case.

As the drive current,  $I_{ON}$ , is ideally proportional to  $v_{inj}$  at a certain drive voltage,  $V_{DD}$ , an improved  $v_{inj}$  could either give a higher  $I_{ON}$  at a constant  $V_{DD}$ , which increase the transistor speed, or  $V_{DD}$  could be reduced while the same  $I_{ON}$  is maintained. For logic applications, the latter means that the power consumption can be lowered without compromising the transistor speed. This is the main reason why III-V MOSFETs are considered for digital applications. However, there are many challenges associated with III-V CMOS including the lack of a high performance p-type MOSFET, the difficulties to integrate the technology on Si substrates and the difficulty to achieve high quality integration of gate dielectric on III-Vs.

Ultimately, there is a window of opportunity for III-V MOSFETs in logic applications. In the ballistic regime, the  $I_{ON}$  could still be improved by scaling of e.g. the gate oxide thickness, which increases the oxide capacitance,  $C_{ox}$ , and hence improves the control of charge in the channel,  $Q_i$  according to

$$Q = C_{ox} (\nu_{gs} - \varphi_S) \tag{1.9}$$

where  $\nu_{gr}\varphi_s$  is the voltage drop over  $C_{ox}$ . However, when the quantum capacitance limit is reached, scaling of the gate oxide thickness can no longer be utilized since the oxide capacitance,  $C_{ox}$ , becomes much larger than the semiconductor capacitance,  $C_{S}$  and, hence, only a small fraction of the gate voltage drops over  $C_{ox}$ . The quantum capacitance limit is material dependent as the size of  $C_S$  is set by the density of states for given geometry, which is in turn set by the effective mass. As shown in table 1.1, the effective electron mass is much larger for Si than for InAs and InGaAs. This means that Si could become advantages again for the extremely scaled MOSFETs. Ultimately,  $I_{ON}$  becomes a trade-off between  $V_{inj}$  and the density of states.

### 1.3 Non-Planar Transistor Geometries

Historically, scaling of MOSFETs followed the principle of keeping the electrical fields in the device constant and certain scaling rules were stipulated on how to shrink the dimensions, reduce the drive voltage, and modify the doping [15]. The driving force was the same as today; to improve the performance, reduce the cost per device and increase the packing density. The single most important enabler was the continually improved resolution of lithographic tools.

As the dimensions are scaled down, undesirable short channel effects (SCE), such as drain induced barrier lowering (DIBL) and poor subthreshold slope, have become an increasingly concern. The SCE reflects the difficulty to retain electrostatic control of

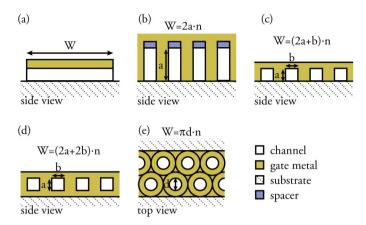

**Figure 1.4:** Different gate geometries seen from the cross-section of the channel. The gate width is indicated. (a) planar, (b) double-gate, (c) tri-gate, (d) lateral gate-all-around, and (e) vertical gate-all-around. In this schematic, the gate oxide between the channel and the gate metal is omitted.

the channel as the gate length,  $L_g$ , is reduced. SCE can, however, be suppressed by implementing non-planar transistor geometries where the transistor channel is gated from more than one direction.

Among the suggested geometries are double-gate (DG) [16], tri-gate and gate-all-around (GAA), illustrated in figure 1.4. Out of these, GAA gives the best electrostatic control as the ratio between gate width, W, and cross-sectional channel area is higher. In a comparison between DG and GAA, it is concluded that the minimum  $L_g$  compared to the thickness of the channel is 40% smaller for GAA than for DG [17]. This also means that at a given  $L_g$ , the channel diameter and oxide thickness can be larger in GAA geometries for the same transistor characteristics.

Using the definition that nanowires are rod-shaped crystals, which could be several micrometers long but must have a diameter below 100 nm, implies that nanowires are already used in commercial CMOS circuits as the tri-gate geometry is already employed by Intel in the 22 nm node [18]. Furthermore, InGaAs and InAs MOSFETs with tri-gate geometry have recently demonstrated excellent performance [19]. By removing the substrate under the tri-gate, as shown in figure 1.4d, it can be converted into the lateral GAA geometry. Also for this geometry, promising results have been reported [20, 21].

The vertical GAA geometry requires a vertical nanowire or pillar. These could either be epitaxially grown, as in this thesis, or etched from a bulk material. Also for this geometry, promising MOSFET data has been published both for Si [22] and III-Vs [23-25]. The main advantages with the vertical nanowire transistors compared to lateral nanowires are the potential for smaller device footprint, due to the vertical alignment of the contacts on top of each other, and the improved conditions for heteroepitaxy in the case of epitaxially grown nanowires. Due to the small nanowire

diameter, strain caused by lattice mismatch is easier released without causing defects. Heteroepitaxy could include both the integration of high quality III-V material on Si substrates [26, 27], and radial or axial heterostructures in the nanowire [28-30].

# 1.4 Applications of Vertical InAs Nanowire MOSFETs

The vertical InAs nanowire MOSFET combines the advantages transport properties of InAs and the improved electrostatic control of GAA geometries, which makes it suitable for high-frequency low-power applications. These applications could be either analog or digital.

For digital applications Si CMOS have dominated the market for several decades due to the excellent scalability and low power consumption. III-V CMOS, or CMOS with a III-V n-type MOSFET and a Ge p-type MOSFET, could potentially replace Si CMOS for logic applications. It is speculated that III-V CMOS might be used already at the ~10 nm node with the first products anticipated in 2018-2020 [31]. However, the requirements are very high; it has to outperform Si CMOS with a performance improvement of at least 30-50% and it has to be scalable for at least one more technology node. Furthermore, the manufacturing must be cost effective and reliable to a degree that has not yet been presented [32]. It is likely that a tri-gate or lateral GAA geometry would be used if III-Vs are used in future CMOS since the trigate geometry is implemented in the 22 nm Si CMOS node.

To accomplish III-V CMOS in vertical nanowires would require even more technology development. Recently, the first III-V CMOS inverter in a single nanowire was demonstrated [33], but with much room for improvement both in performance and design. Still, digital applications should not be excluded for the vertical InAs nanowire MOSFETs. The vertical geometry could potentially give a smaller footprint as the contacts are aligned on top of each other, which is attractive for extreme scaling. The vertical nanowires are also advantageous in the heterogeneous integration of III-Vs on Si substrates.

Closer at hand are the use of vertical InAs nanowire MOSFETs in analog applications. This market is more diverse and III-V technologies, such as HEMTs, MESFETs and HBTs, are important due to the excellent high frequency performance. The InAs nanowire MOSFET could find a niche by targeting low-power analog application.

### 1.5 High- $\kappa$ Dielectrics on III-Vs

#### 1.5.1 High- $\kappa$ versus native oxide

A high quality gate dielectric is a key to good device performance. It is even so that the high quality native oxide of Si was one of the main reasons why Si MOSFETs became successful in the first place. However, as the oxide thickness is scaled down below a few nanometers, tunneling currents through the oxide becomes an increasing problem. This leakage current leads to an increased power consumption of the device.

A possibility to overcome this has been provided by the development of atomic layer deposition (ALD) where high-permittivity (high- $\kappa$ ) gate dielectric of high quality can be deposited. Compared to SiO<sub>2</sub>, the high- $\kappa$  dielectric has a larger physical thickness for the same oxide capacitance, which is expressed by

$$C_{ox} = \frac{\kappa \varepsilon_0 W L_g}{t_{ox}} \tag{1.10}$$

where  $\kappa$  is the relative permittivity,  $\varepsilon_{\theta}$  is the permittivity in vacuum, W is the gate width, and  $t_{ox}$  is the physical oxide thickness. For comparison,  $\kappa$  values of a few commonly used dielectrics are listed in table 1.2 together with the bandgap and the conduction band offset to InAs,  $\Delta E_{\varepsilon,lpAs}$ .

The electrical thickness is commonly characterized by the equivalent oxide thickness (EOT), which is the corresponding thickness of a  $SiO_2$  film giving the same  $C_{ox}$ . This measure, which has become a standard, is used also for III-V semiconductors even though  $SiO_2$  is not a natural choice for these materials. Furthermore, the quality of native oxides on III-Vs is poor and cannot be used. Hence, high- $\kappa$  is widely used in III-V MOSFETs and EOT down to 1 nm with low gate leakage currents has been demonstrated on InAs using HfO<sub>2</sub> [34].

|                                | κ   | $E_g$ (eV) | $\Delta E_{c,InAs}$ (eV) |

|--------------------------------|-----|------------|--------------------------|

| SiO <sub>2</sub>               | 3.9 | 9          | 4.1                      |

| $Si_3N_4$                      | 7   | 5.3        | 2.7                      |

| Al <sub>2</sub> O <sub>3</sub> | 9   | 8.8        | 3.6                      |

| HfO <sub>2</sub>               | 25  | 5.8        | 2.5                      |

**Table 1.2:** Material properties of a few selected dielectric materials [35, 36].

#### 1.5.2 Interface traps and border traps

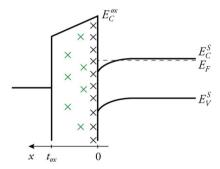

Interface traps and border traps are defect-induced states in the gate dielectric of a MOS structure that may trap charge carriers. The interface traps are located at the dielectric-semiconductor interface, while the border traps are distributed inside the dielectric. Their distribution in space and energy is schematically illustrated for an n-type MOSFET in figure 1.5. A third kind of charge traps are defects in the oxide that might be charged but cannot trap/de-trap charge carriers under normal operation. These are referred to as fixed oxide charge. The fixed oxide charge may shift the threshold voltage of the MOSFET and increase the scattering, but have little effect on the characteristics apart for that.

**Figure 1.5:** Schematic of the MOS structure including border traps (green crosses) and interface traps (gray crosses).

On the other hand, mainly interface traps, but also border traps, have a profound effect on the characteristics of the MOSFET including the subthreshold slope and the extrinsic transconductance. This is especially true for III-V MOSFETs since they typically suffer from very high densities of interface traps,  $D_{tt}$ , and border traps,  $N_{bt}$ , typically in the order of  $10^{12}$ - $10^{13}$  eV<sup>-1</sup>cm<sup>-2</sup> and  $10^{18}$ - $10^{19}$  eV<sup>-1</sup>cm<sup>-3</sup>, respectively [37-40].

In the literature, there is some confusion on the nomenclature that should be used to describe these defect-induced states, leading to that both interface traps and border traps may be reported in term of  $D_{tt}$  [41]. Even though the two types of traps might sometimes be difficult to distinguish in measurements, their differences should be considered in the theoretical description

Some examples of defects are dangling bonds, semiconductor dimer pairs, oxygen interstitials, and oxygen vacancies [42]. In the interface region, which is in the order of 1 Å, defects are related both to atoms in the semiconductor and atoms in the dielectric, while, further into the dielectric, defects are related only to atoms in the dielectric. One reason to why high- $\kappa$  integration on III-Vs is challenging is the higher complexity of an III-V-high- $\kappa$  interface compared to a Si-SiO<sub>2</sub> interface. For example,

an  $InGaAs-HfO_2$  interface has five different elements (In, Ga, As, Hf, and O) while a  $Si-SiO_2$  interface has two (Si, and O). Further details on the modeling of traps are presented in chapter 4 together with a method to characterize traps with a focus on border traps.

## 2. Device Fabrication

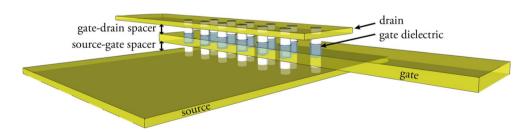

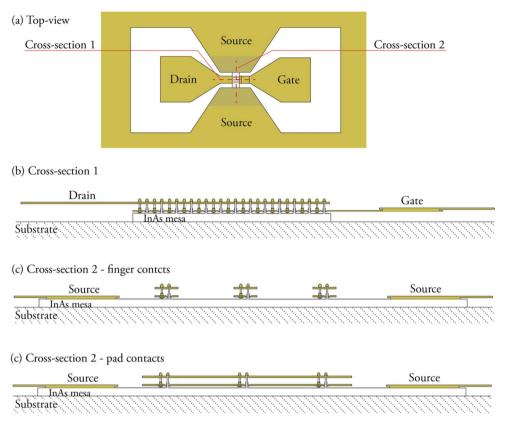

Device fabrication based on vertical nanowires is a novel field with plenty of opportunities for innovation and often with a substantial need of process optimization. The general layout of a vertical nanowire MOSFET is illustrated in figure 2.1. In addition to the three contacts placed along the nanowires, it also constitutes of spacers to avoid short circuiting and control the parasitic capacitances.

Early work on vertical nanowire MOSFETs, *i.e.* before 2010, has mainly focused on process development and DC performance and did not include any reports on high-frequency performance [24, 43-47]. In this thesis the high-frequency performance has been the main design target. However, DC performance, reproducibility, yield, and scalability have also been important in the design.

In this chapter, the key enablers of our process, *i.e.* nanowire growth, gate-all-around contacts, and an RF compatible design are described. This is followed by a discussion on the development of the process scheme over time, where three generations of the vertical InAs nanowire MOSFET are presented. Furthermore, a detailed process step recipe can be found in Appendix.

Figure 2.1: Schematic layout of a vertical nanowire MOSFET.

#### 2.1 Nanowire Growth

The nanowires in this thesis are grown from gold particles on a semiconductor surface by the vapor-liquid-solid (VLS) growth mechanism [48, 49]. This is achieved by tuning the growth conditions so that epitaxial growth aided by the gold particle is favorable while other types of growth are suppressed. In the process, the sample is exposed to precursors in the gas phase which contains the group III and V elements of the desired compound; if a precursor is adsorbed at the surface of the sample it will move around diffusively after which it will either incorporate in one of the gold particles or desorb and return to the gas phase. The supply of material to the gold particle leads to a high super-saturation compared to the crystal resulting in crystal nucleation at the gold-semiconductor interface. After nucleation, the nanowire will grow by lifting the Au particle from the surface and continuously adding material underneath.

The technique that is used is metal-organic vapor-phase-epitaxy (MOVPE) which is also referred to as metal-organic chemical-vapor-deposition (MOCVD). The precursors used for InAs nanowires are trimethylindium (TMIn) and arsine (AsH<sub>3</sub>). In addition, the nanowires are n-type doped by adding tetraethyltin (TESn).

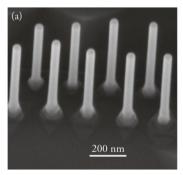

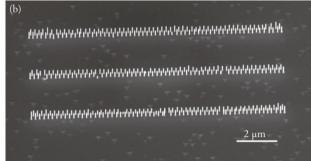

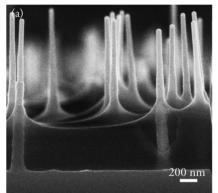

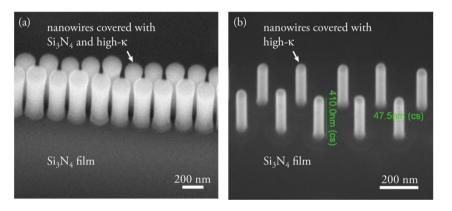

To achieve ordered arrays the catalyst gold particles are defined by electron beam lithography (EBL). The exposed pattern is transferred from the e-beam resist to a thin gold film by evaporation and lift-off. The dot exposure dose and the Au film thickness sets the diameter of the nanowire, which typically ranges from 20 to 65 nm. Typical nanowire arrays fabricated by this method are depicted in figure 2.2.

**Figure 2.2:** 30° tilted SEM image of nanowire arrays covered with high- $\kappa$  dielectric film.

#### 2.2 Gate-All-Around

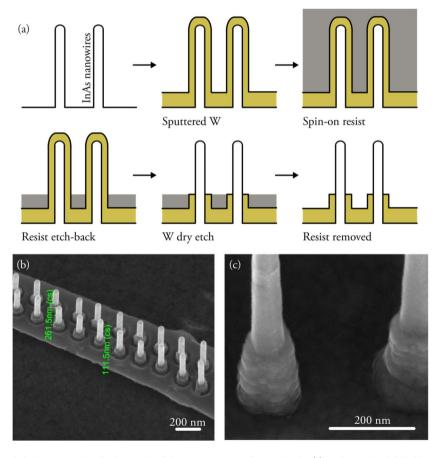

In the vertical geometry, the gate length,  $L_g$ , is not set by lithography. Instead  $L_g$  is set by the film thickness of an anisotropically deposited film or by partial sidewall etching of a conformal film. The gate-all-around contacts, or wrap-gates, used in this thesis are fabricated by sputtering of a W film resulting in a film thickness on the nanowire which is about 1/3 of the thickness on the planar surface.  $L_g$  is set by spinning of a resist film and thinning it down to the desired thickness. The metal on the upper part of the nanowires that are not protected by the resist is subsequently etched by dry etching. The process is illustrated in figure 2.3 and is preferred over evaporated gates due to the higher yield and reproducibility. The main drawback is that scaling of  $L_g$  is limited by the conformity of the resist layer. For very short electrodes, such as gate length below 20 nm, the process needs to be modified or replaced.

**Figure 2.3:** Cross-sectional schematic of the wrap-contact formation in (a) and 30° tilted SEM image of wrap-contacts represented by a W gate-all-around finger contact in (b) and an Al/W wrap-source contact covered with a high- $\kappa$  dielectric in (c).

### 2.3 RF Compatible Design

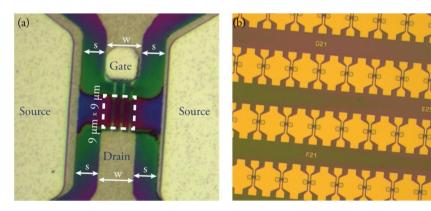

Reliable RF characterization requires good impedance matching to the measurement equipment, which is normally calibrated to 50  $\Omega$ . A transistor based on a single nanowire has impedance in the order of  $k\Omega$ , which is too high. Hence, the impedance is lowered using arrays with 20-600 nanowires in parallel in a single device.

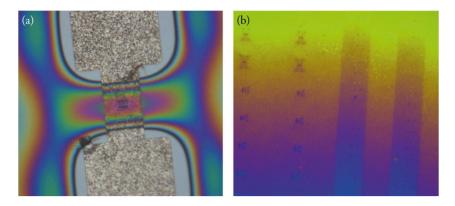

To minimize losses in the contact pads at high frequency, a coplanar waveguide (CPW) layout is used where the width, w, of the gate and drain pads are separated from the ground plane, *i.e.* the source pads, by the distance s. A ratio of w/s = 1.5 is used. Micrographs of the completed transistors illustrate the layout of the probing pads in figure 2.4.

Furthermore, device isolation is a key for reliable RF measurements. Hence, the transistors are preferably placed on semi-insulating (S.I.) or highly resistive substrates. If a conductive substrate is used the  $50-\Omega$ -impedance matching will deteriorate at high frequencies due to the capacitive load between the probing pads and the substrate. This would also complicate the de-embedding of the transistor cell, which is described further in chapter 3.

**Figure 2.4:** Micrographs of completed transistors using a  $50-\Omega$  coplanar waveguide with a close-up showing a  $9 \mu m \cdot 9 \mu m$  transistor cell in (a) and an overview with in total 27 transistors in (b).

# 2.4 Three Generations of Vertical InAs Nanowire MOSFETs

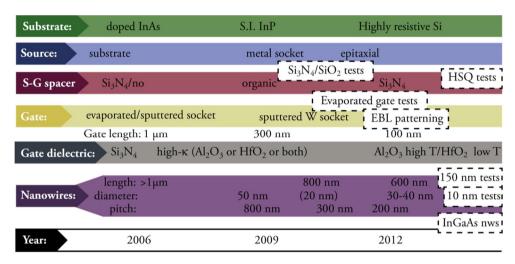

Since the first vertical nanowire MOSFET was reported from Lund University in 2006, new materials and geometries have been tested for almost every part of the device. The process development over time is summarized in figure 2.5.

One of the largest changes is the replacement of the conductive InAs substrate to semi-insulating (S.I. InP) substrate and later to highly resistive Si substrate, which also required new source contacts to be developed. The epitaxial structures formed on the three substrates are schematically illustrated in figure 2.6. How the vertical InAs nanowire MOSFETs were realized on the new substrates and how a vertical structure with low parasitic capacitance was implemented is presented below in terms of three generations of the vertical InAs nanowire MOSFET.

Figure 2.5: Timeline showing the development of the process scheme. White boxes indicate tests.

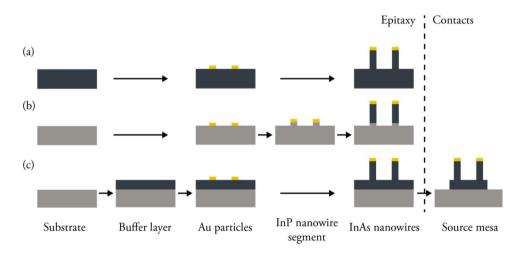

**Figure 2.6:** Schematic of the processing of three different epitaxial structures used for vertical InAs nanowire MOSFETs with (a) conducting InAs substrate, (b) semi-insulating InP substrate and, (c) highly resistive Si substrate.

#### 2.4.1 Generation 1 - on semi-insulating InP substrate

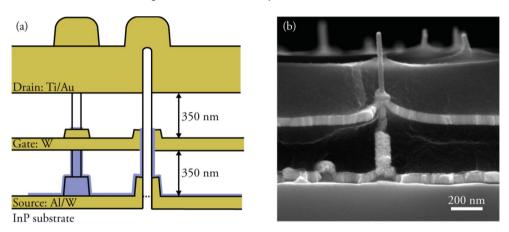

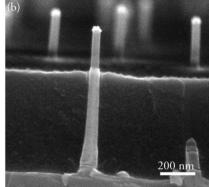

In the first generation of high-frequency InAs nanowire MOSFETs, *i.e.* Paper I, the nanowires were integrated on S.I. InP (111). To achieve homogenous nanowire nucleation, a short InP nanowire segment was first grown, on top of which the InAs nanowire were heterogeneously integrated [49]. The resulting epitaxial structure is schematically illustrated in figure 2.6b. The transistors fabricated with these nanowires are presented in figure 2.7 by a schematic cross-section of a device and a cross-sectional SEM image of a reference sample.

**Figure 2.7:** (a) Schematics of the transistor cross-section on InP substrate with metal source socket and resist spacers, and (b) cross-sectional SEM micrograph of the same structure on a reference sample with randomly distributed nanowires. The drain metal is not deposited in (b).

Previously, the InAs substrate was used as a source contact, but the use of a S.I. InP substrate requires a source contact formation at the lower part of the nanowires. A sputtered metal wrap-contact was formed as described in Ch. 2.2. The contact length had to be sufficient to achieve a good contact to the InAs part of the nanowire. For a 50-100 nm InP segment, a wrap-contact length of about 200 nm was used. A 10/60 nm Al/W metal film was used where the thin Al film was added to protect the nanowires from potential surface damage caused by the impingement of ions during the W dry-etch. Preserving a good surface was especially important as the  $Al_2O_3$  gate dielectric was deposited after source formation.

To avoid leakage between source and gate, an organic spacer, which covered the source metal socket completely, was formed in etched-back S1818. When using etched-back resists, height differences occur on the sample both locally around structures and globally across the sample. Figure 2.8 exemplifies the color variations of the resist, which can be a good measure of the surface topology.

**Figure 2.8:** Color variations of etched-back S1800 series resist due to height differences. In (a) the resist is used as source-gate spacer and the openings are source vias. In (b) the resist is used for etch-back of a  $Si_3N_4$  source-gate spacer on a sample with source pad pattern in the high- $\kappa$  only. The height variations are approximately in the order of 200 nm in (a) and 50 nm in (b).

The device was completed by an Al/W wrap-gate, an organic gate-drain spacer and sputtered Ti/Au drain contact.

In conclusion, the use of S.I. InP substrates made the design RF compatible; however, the wafers are expensive, brittle and the size is limited to 4 inch. And, from a device fabrication point of view, this approach has an increased complexity as it requires a wrap-contact at the source.

#### 2.4.2 Generation 2 - on highly resistive Si substrates

In the second generation of high-frequency InAs nanowire MOSFETs, *i.e.* Paper II-IV, InAs nanowires were instead integrated on highly resistive Si (111) substrates, which improves the potential of the technology in terms of large scale applications. The heterogeneous integration was realized by a buffer layer technique where a thin film of InAs with a lattice mismatch of about 11% to Si was first grown [50]. Sufficient crystal quality was achieved by cycling growth of nucleation layers at low temperature with annealing at high temperature during the individual steps of the growth. On top of the InAs buffer layer, InAs nanowires were grown as schematically illustrated in figure 2.6. Here, device isolation was achieved in a later process step by etching mesa structures the InAs film. The InAs mesas also constitute the source contacts in these devices. The complete device is presented in figure 2.9 by a schematic cross-section and cross-sectional SEM image of a reference sample.

**Figure 2.9:** (a) Schematics of the transistor cross-section on Si substrate using the InAs buffer layer as a source contact and with resist spacers, and (b) cross-sectional SEM micrograph of the same structure on a reference sample with randomly distributed nanowires.

In paper III, the diameter and position control of the nanowires was targeted and the possibility of growing InAs nanowire arrays on 2 inch Si wafers in a controlled fashion was demonstrated. SEM inspection of the wafer revealed a nanowire growth yield of 100%. However, a diameter variation of 15 nm was observed, although having the same nominal dose, when comparing the first and the last nanowires according to the order of exposure in the EBL. This was most likely due to drift in the beam current of the EBL during the 10 h exposure time. For a single array the diameter variation around the nominal nanowire diameter was 6 nm.

The vertical process requires the high- $\kappa$  gate dielectric to be deposited quite early in the process. In the first generation, high- $\kappa$  was deposited after socket formation while, in the second generation, the high- $\kappa$  was deposited right after growth and exposure time in air was kept as short as possible. Furthermore, post deposition annealing (PDA) in forming gas was employed in the second generation of transistors to improve the quality of the high- $\kappa$  integration. The high- $\kappa$  dielectrics that have been used are Al<sub>2</sub>O<sub>3</sub> and HfO<sub>2</sub> deposited by atomic layer deposition (ALD). Al<sub>2</sub>O<sub>3</sub> is etched faster and believed to give a better interface to the semiconductor, while HfO<sub>2</sub> has a higher permittivity, *i.e.* higher  $\kappa$  value.

**Figure 2.10:** S1800 series resist profiles on nanowire reference samples (a) if permanently baked at 200°C after thinning down the resist thickness, and (b) ) if permanently baked at 200°C before thinning down the resist thickness. In (b) the high- $\kappa$  dielectric is removed from the top of the nanowire using the resist as an etch mask.

The source-gate spacer, gate, and gate-drain spacer are formed as in the previous generation; however, it was noted that permanent baking of the resist before defining the thickness is preferable as this gives a more planar profile compared to etching back first and baking afterwards. This is seen in the cross-sectional SEM images in 2.10 as well as in figure 2.7b and 2.9b.

In the first generation, the aggressive Au wet etch when patterning the drain contact was problematic since InAs nanowire close to the edge of the drain pad were also etched. To avoid this W was inserted in the metal stack giving a Ti/W/Au top metal layer. The W film protected the nanowires during Au etch and was removed by subsequent dry etching.

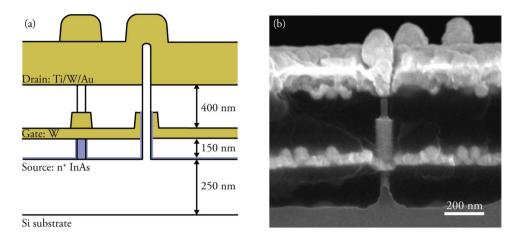

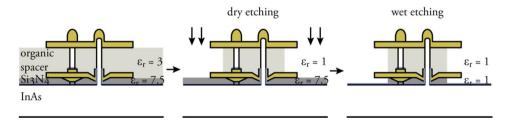

#### 2.4.3 Generation 3 - with reduced metal overlap

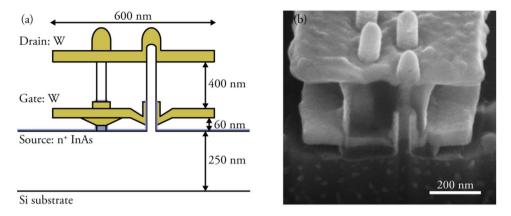

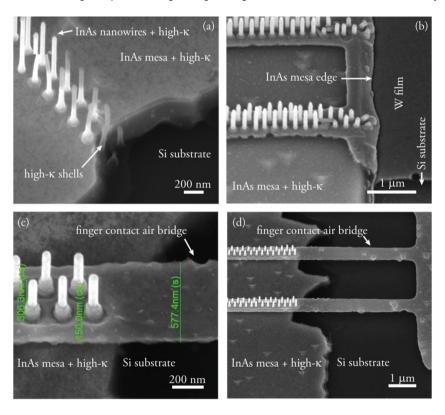

In the third generation of high-frequency InAs nanowire MOSFETs, *i.e.* Paper VII, the RF performance was boosted by reducing the excess metal overlap and, hence, the parasitic gate capacitance,  $C_{gg,p}$ . Figure 2.11a presents a schematic of the device, while figure 2.11b shows a cross-section of a device enabled by focused ion beam (FIB) milling.

**Figure 2.11:** (a) Schematics of the transistor cross-section using finger gate and drain contacts both with a width of 600 nm, and with  $Si_3N_4$  source-gate spacer, and (b)  $52^{\circ}$  tilted SEM micrograph of a device cross-section cut by focused ion beam (FIB).

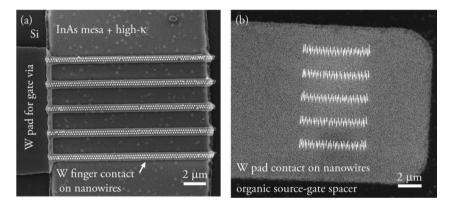

**Figure 2.12:** (a) Top view SEM image of the new design with finger gate contacts on nanowire double rows and, (b) 30° tilted SEM image of the old design using a large pad gate contact.

The metal overlap was reduced by replacing the pad contacts, which was used in previous publications, with finger contacts formed by EBL and dry etching. The new and old contact designs are compared in figure 2.12. In the new design, W contacts were used both for gate and drain. The EBL pattern was automatically aligned to the array using markers formed by vertical nanowires. For the gate contact shown in figure 2.12a, the mean width of the fingers is 670 nm with a standard derivation of 28 nm. The mean shift from the center is 29 nm. Furthermore, figure 2.13 depicts the complete transistor layout both for a device with finger contacts and for a reference device with pad contacts.

**Figure 2.13:** Illustration of the layout including (a) an overview, (b) gate-to-drain cross-section, (c) source-to-source cross-section using finger contacts, and (d) source-to-source cross-section using pad contacts. The spacers are omitted for clarity.

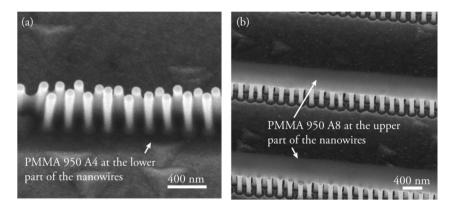

It should be noted that the nanowires do not need to be fully covered by resist when forming the finger contacts. The used resist was PMMA 950 A4, which has a thickness of about 300 nm. For the employed exposure settings, back scattering gives a large undercut in the resist profile for thicker resists, such as PMMA 950 A8, which has a nominal thickness of about 1  $\mu$ m. The resist profiles in the two cases are depicted in figure 2.14. The resist profile in figure 2.14b is not suitable for finger contacts, but could possibly be used as a mask when etching at the lower part of the nanowire.

In future generations of the vertical InAs nanowire MOSFET, the parasitic capacitance could be reduced even more by scaling the width of the finger contacts. The positive effect is enhanced if the spacing between the nanowires is reduced as this will increase the screening of electric field between the contacts by the nanowires and, hence, reduce the capacitance [51]. However, increased resistance in the fingers must

**Figure 2.14:** 30° tilted SEM images of fingers formed by EBL in two types of resist: (a) PMMA 950 A4, which was used the finger contacts formation, with a spin-on thickness of 300 nm, and (b) PMMA 950 A8 with a spin-on thickness of about 1  $\mu$ m.

Figure 2.15: Si<sub>3</sub>N<sub>4</sub> spacer (a) before and (b) after etch-back. 30° tilted SEM images.

be avoided either by shortening the fingers or by adding more metal in the vertical direction.

In a broader perspective, it is not a reduction of  $C_{gg,p}$  that boost the RF performance, but an improved  $g_m/C_{gg}$  ratio. To increase this ratio, the length of the nanowire double rows can be extended so that the size of the nanowire array will be self-aligned to the width of the source pad. To achieve this, double rows are first fabricated that are longer than the width of the source pad. The nanowires outside the source pad will then be removed when forming the source mesa with an InAs wet etch. This method was used in figure 2.12a and 2.16a.

Another modification in the third generation of vertical InAs nanowire MOSFETs was that the organic source-gate spacer was replaced by a Si<sub>3</sub>N<sub>4</sub> spacer. Si<sub>3</sub>N<sub>4</sub> was deposited by chemical vapor deposition (CVD) and etched back by dry etching. The

$Si_3N_4$  spacer is shown in figure 2.15 before and after the back-etch. Compared to an organic spacer,  $Si_3N_4$  has an improved mechanical stability and can withstand higher temperatures. Hence, a post-metallization annealing (PMA) after gate deposition could be implemented to improve the quality of the gate dielectric. Here, a PMA at  $300^{\circ}$ C in forming gas was used for the  $Al_2O_3/HfO_2$  bilayer gate dielectric.

The height differences on the sample are always a potential problem. One example is the step at the edges of the InAs mesa, which is depicted in 2.16a. The step remains after forming the Si<sub>3</sub>N<sub>4</sub> spacer and if the gate metal is sputtered on this structure, the risk is high for increased gate resistance caused by poor film coverage at the InAs mesa edge, see 2.16b. This problem was avoided by postponing the InAs etch and, hence, forming air bridges underneath the gate fingers as shown in figure 2.16c-d. The following process flow was used: First, a protection for the InAs source pads was formed in the gate dielectric by UV-lithography. Finger gate pads were formed in gate metal and source-gate spacer using a finger length which was extended at least 1 μm

**Figure 2.16:** SEM images at 30° tilt showing (a) the edge of the InAs source mesa covered with high- $\kappa$ . Here, also nanowires not protected by resist were etched in the source mesa wet etch. (b) Finger gate contacts with poor metal coverage at the InAs mesa edge. (c), (d) Air bridged finger gate contact formed by InAs mesa under etching.

from the source pad edge. Finally, the InAs layer was etch for to form the source mesa using the gate dielectric as an etch mask. The etch time was prolonged for complete under-etch of the gate fingers outside of the source pad.

# 3. Electrical Performance

#### 3.1 DC Characterization

A completed transistor usually undergoes initial DC characterization before any other measurements are performed. The data is acquired by on-chip probing where DC voltages are applied to the source, gate, and drain terminals, and the resulting currents are measured. From this some fundamental metrics can be deduced as discussed in chapter 1.1.2. DC metrics for the devices with the best RF performance published in Paper I (on InP substrate, 2010), Paper II (on Si substrate, 2011), and Paper VII (with finger contacts, 2014) are compared in table 3.1.

|           | l <sub>ds</sub> | R <sub>oN</sub> | $g_{ds}$ | g <sub>m</sub> | SS       |

|-----------|-----------------|-----------------|----------|----------------|----------|

|           | (mA/mm)         | (kΩ- $\mu$ m)   | (mS/mm)  | (mS/mm)        | (mV/dec) |

| Paper I   | 300             | 1.8             | 130      | 150            | -        |

| Paper II  | 550             | 1.6             | 260      | 155            | -        |

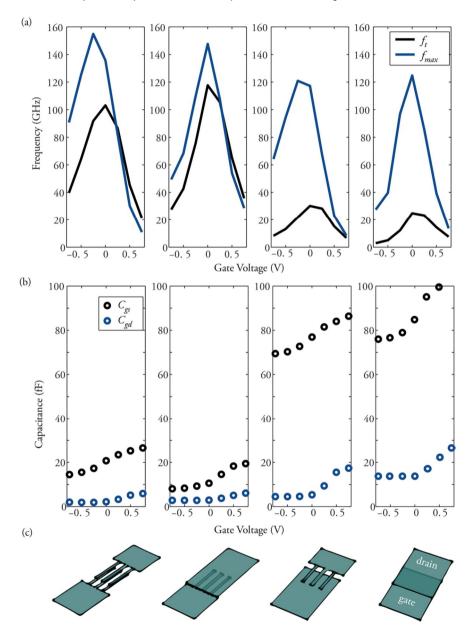

| Paper VII | 450             | 1.4             | 72       | 730            | 420      |