# A 2GHz merged CMOS LNA and mixer for WCDMA

Karimi-Sanjaani, Ali; Sjöland, Henrik; Abidi, Asad

Published in:

Symposium on VLSI Circuits, 2001. Digest of Technical Papers.

DOI:

10.1109/VLSIC.2001.934180

2001

## Link to publication

Citation for published version (APA):

Karimi-Sanjaani, A., Sjöland, H., & Abidi, A. (2001). A 2GHz merged CMOS LNA and mixer for WCDMA. In *Symposium on VLSI Circuits, 2001. Digest of Technical Papers.* (pp. 19-22). IEEE - Institute of Electrical and Electronics Engineers Inc.. https://doi.org/10.1109/VLSIC.2001.934180

Total number of authors:

## General rights

Unless other specific re-use rights are stated the following general rights apply:

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

• You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal

Read more about Creative commons licenses: https://creativecommons.org/licenses/

Take down policy

If you believe that this document breaches copyright please contact us providing details, and we will remove access to the work immediately and investigate your claim.

Download date: 18. Dec. 2025

# A 2 GHz Merged CMOS LNA and Mixer for WCDMA

## Ali Karimi-Sanjaani, Henrik Sjöland\*, Asad A. Abidi

Electrical Engineering Department University of California, Los Angeles, CA 90095-1594 \*Lund University, Sweden

### Abstract

A merged LNA and mixer with an on-chip VCO is fabricated in 0.35 µm CMOS for a 2.1 GHz WCDMA receiver. The front-end consumes 8mA from 2.7V and gives NF of 3.2dB, conversion gain of 24.2 dB, and input IP3 of -1.5dBm. The VCO consumes 3mA while achieving phase noise of -128.4 and -138.5 dBc/Hz at offsets of 5 and 15 MHz, respectively.

#### Front-End Architecture

Noise and linearity requirements are very demanding in WCDMA receivers [1]. The zero-IF architecture is of interest because 1/f noise and DC offset can be filtered with little impact on the 5 MHz wide spread-spectrum signal [2]. This paper revisits the idea of sharing bias current to introduce a merged LNA and mixer which achieves very good dynamic range with less power compared to the conventional cascade LNA and mixers.

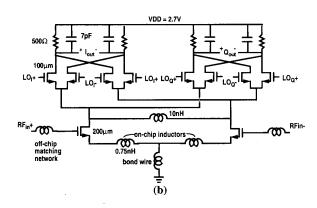

Fig. 1 shows the merged LNA and quadrature mixers. Risks with this topology are lower gain and lower LO-RF isolation. However, with careful design, the front-end is shown to satisfy 3G WCDMA specifications.

## Low Noise Amplifier

The NF of a 3G receiver should be 5-6 dB, which implies that if the conversion gain of the receiver front-end is about 20 dB, its own NF is 3 dB. The common-source (CS) LNA deemphasizes FET noise by the voltage gain through the input matching circuit. At impedance match the noise factor (F) is given by  $F = 1 + \gamma \cdot \alpha / (1 + L_g / L_s)$ , which points to small source degeneration (Ls) for lower noise figure. This is implemented in this differential LNA as a pair of 0.78nH on-chip inductors, each realized by 1.5 turns of Metal-4 layer with 1.4 $\Omega$ resistance.

The pad capacitance (60fF) is included in the input matching network. Metal routing of gate and source of LNA transistors to the pads also contribute to noise. The higher the quality factor (Q) of the input circuit, the lower the thermal noise, but the higher the gate induced noise. It's been found by simulations that the lowest F is at the point that the thermal noise and the gate induced noise have the same share of input referred noise. Simulations showed that a size of  $200\mu m/0.35\mu m$  for LNA transistors would make the share of thermal noise to be 21% and the share of gate induced noise to be 22.4%. The dynamic range (DR) of a CS degenerated LNA is constant at a given current, and slides up or down with Lg. A bias current of 4mA in each side of LNA gives the DR needed for whole front-

Two mixers driven by quadrature LO phases commutate the LNA output current. As there are no additional transistors in the LNA path, this gives best overall linearity. A resistor load further lowers noise. A large mixer FET size (100/0.35μm) promotes faster switching, which lowers nonlinearity due to signal-dependent current division during current transition. The on-chip LO drives the mixer with 1 volt peak.

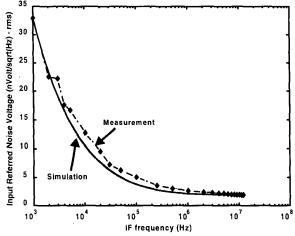

According to [3], slowly varying flicker noise at the gate of mixer FETs appears untranslated in frequency at the mixer output through two mechanisms: by modulating the zerocrossing of the tail current (direct mechanism), and by inducing current in the tail capacitance (indirect mechanism). Large LO amplitude lowers the direct mechanism. This circuit features a new method to lower the indirect mechanism. A differential inductor between the two LNA outputs tunes out the tail capacitance. Now only the direct mechanism remains, and the total flicker noise spectral density at the mixer output is lowered by about 35%.

## **Properties of Merged Quadrature Mixers**

The merged quadrature mixers, coupled at the tails of the two differential pairs, behave differently than two independent mixers. In addition to the downconverted signal, a strong component at the 2<sup>nd</sup> harmonic of the LO appears at each load resistor. A capacitor of 7pF is connected across the  $500\Omega$  mixer load to pass the 5 MHz-wide downconverted channel but suppress this component at 4.2 GHz.

Also, as quadrature phases of the LO induce the voltage ripple at the merged sources of the mixer differential pairs, the magnitude of the ripple is lower than in a conventional mixer, but its dominant component lies at the 4th harmonic of the LO.

Every quarter period of the LO, one of the four FETs attached to each LNA drain conducts in sequence. The large LO amplitude used here forces the conducting FET into triode. It is found through simulation that the capacitance at the LNA drain, when sequentially switched into the four 7pF filter capacitors at the mixer outputs, acquires a voltage ripple at the LO fundamental. This is potentially a serious problem, because it can couple through the CGD of the LNA FETs to the receiver input and radiate in-band. WCDMA restricts the LO radiation to -60 dBm. Simulations show that the LO feedthrough to the antenna at each terminal of the LNA is less than -78.3 dBm across the band, and as this is a common-mode signal, it is further suppressed by the input balun.

## On-Chip VCO

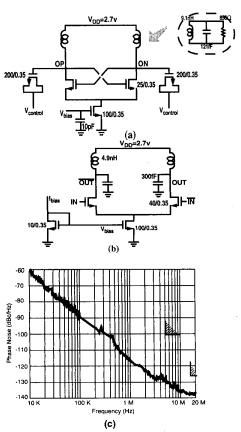

A 3mA VCO has been designed to fulfill WCDMA phase noise specifications with a fully on-chip resonator (Fig. 3(a)). The oscillator is tuned with a single 18.2nH differential spiral inductor with Q of 7, and a MOSFET varactor. It has 200MHz tuning range centered at 2.14GHz. Its phase noise at the offset of 5 and 15MHz is -128.4 and -138.5dBc/Hz respectively (Fig. 3(c)). An RC polyphase filter with two stages tuned to 2.27 GHz and 1.73 GHz generates quadrature phases. A buffer, Fig. 3(b), is inserted between the VCO and polyphase filter to prevent the resonator from being loaded by the polyphase filter or pulled by the mixer.

## **Experimental Results and Discussion**

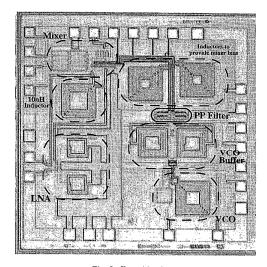

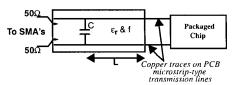

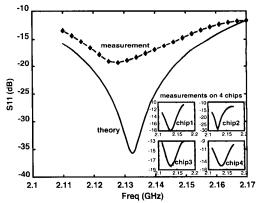

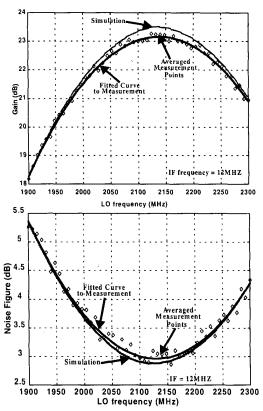

The front-end IC was fabricated in 0.35- $\mu$ m BiCMOS6M from ST Microelectronics using only MOSFETs (Fig. 3). The IC is mounted in a standard microwave package. A 2pF chip capacitor is slid along a differential microstrip transmission line on the PC board, about 2 cm long, until the input impedance is satisfactorily matched (Fig. 4). Fig. 5 shows the differential  $s_{11}$  for four different chips tested.

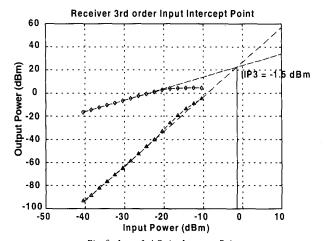

The NF is de-embedded with proper procedures [4]. Fig. 6 shows the gain and NF measured by a noise figure meter at an output IF of 12MHz. After calibration, NF at lower frequencies is measured on a spectrum analyzer. System simulations show that a highpass filter with a cutoff frequency of 5 kHz does not degrade BER of the 5 MHz-wide channel centered at DC. Flicker noise (Fig. 7) degrades the integrated noise from 5 kHz to 5 MHz by only 0.2dB. Measured LO feedthrough to the antenna lies in the range of -76 to -71dBm over the 2.11GHz to 2.17 GHz band. IIP3 measured on four chips varies from +3dBm to -3dBm, with an average of -1.5dBm (Fig. 8). Table 1 compares measured results with simulations. Second-order intercept point (IIP2) cannot be simulated, but is measured to be +47 dBm which is sufficient [1].

This front end, when cascaded with baseband circuits with NF of at most 17dB and an IIP3 of at least +6 dBm, will satisfy the WCDMA receiver specifications [1],[5]. These figures are attainable in practice; for example, baseband circuits described in [2] show NF of 12.7dB and IIP3 of +14 dBm.

In full-duplex WCDMA the power amplifier output couples through the imperfect duplexer to the receiver input [1]. Although this feedthrough lies in the TX band, it potentially overloads the front end and desensitizes reception in the RX band. The receiver must be sufficiently linear to guard against this eventuality. Assuming peak PA output of +24dBm and 58 dB attenuation of TX to RX feedthrough in the duplexer and filter, the highest leakage to the LNA input is -32 dBm. The 1dB gain compression level is one-third of the IIP3 signal level [6]. So if a WCDMA front-end has an IIP3 of at least -22.4 dBm, PA feedthrough will not desensitize it.

Others, too, have investigated ways to merge the LNA and mixer; for example, [7-9]. We define a figure of merit (FOM) to compare the performance of these various front-ends. This FOM normalizes the dynamic range (DR) to the power consumption of the front end:

$$\mathbf{DR} \propto \frac{\mathbf{IIP_3}}{\mathbf{F} \cdot \mathbf{1}} \propto \mathbf{I_{dc}} \qquad FOM(dB) = 10 \log \left( \frac{11P3(mW)}{(F-1) \cdot Vdd \cdot Idc} \right)$$

Table 2 compares the FOM of the most relevant competing circuits.

## Conclusions

A merged LNA-mixer topology is proposed to obtain the high dynamic range at low power consumption required in a WCDMA receiver. Flicker noise is characterized, and negligibly degrades sensitivity. Special issues of LO feedthrough that arise by merging quadrature mixers in this way are addressed. An on-chip VCO fulfilling phase noise specifications for WCDMA RX drives the mixer through a polyphase filter to generate quadrature phases.

This prototype gives substantially higher dynamic range per unit power consumption than previously published similar topologies.

Table 1: Front-end measured and simulated specifications.

| Quantity                               | Measurement         | Simulation |

|----------------------------------------|---------------------|------------|

| Cascade Noise Figure @ IF = 12MHz [dB] | 3                   | 3          |

| Average NF from 50 kHz to 2.5 MHz [dB] | 3.2                 | 3.2        |

| liP3 [dBm]                             | -1.5(avg) / -3(min) | -0.2       |

| Conversion Gain @ IF = 12MHz [dB]      | 22.5                | 24.5       |

| Conversion Gain to dc                  | 24.2                | 27         |

| LNA+Mixer Bias Current [mA]            | 8                   | 8          |

| VCO Bias Current [mA]                  | 3                   | 3          |

| LO power @ antenna input [dBm]         | < -71               | < .78.3    |

| s11, Input Matching [dB]               | < -11               | < -11      |

Table 2: Comparison with other recent LNA & mixers (some merged)

| Ref.                   | Gain<br>(dB) | NF<br>(dB) | IIP3<br>(dBm) | I <sub>dc</sub><br>(m A) | LO-RF<br>isol.<br>(dB) | Process          | Use             | FOM<br>(dB) |

|------------------------|--------------|------------|---------------|--------------------------|------------------------|------------------|-----------------|-------------|

| This work              | 24.2         | 3.2        | -1,5          | 8                        | >7.2                   | 0.35µ CMOS       | WCDMA           | 14.8        |

| [9]<br>(merged)        | 27           | 9          | -18           | 0.2                      | 50                     | 0.5µ CMOS        | 430MHz<br>ISM   | 10.2        |

| [11]                   | 16           | 4.7        | -4.2          | 12                       | >70                    | 0.6μ CMOS        | 2.4 GHz<br>WLAN | 6.9         |

| [10]                   | 25           | 4          | -9            | 8                        | >66                    | BJT              | WCDMA           | 5.9         |

| [7] (partly<br>merged) | 12           | 2.6        | -14.5         | 8                        | >70                    | 0.5µ CMOS        | GPS             | 5.6         |

| [8]<br>(merged)        | 14           | 6.9        | -5.9          | 10.3                     | 61                     | 0.5µ SiGe<br>BJT | 5 GHz<br>WLAN   | 5.5         |

- [1] O. K. Jensen, et al., "RF Receiver Requirements for 3G W-CDMA Mobile Equipment," Microwave Journal, Feb. 2000.

- [2] A. Parssinen, et al., "A 2-GHz Wide-Band Direct Conversion Receiver for WCDMA Applications," *IEEE Journal of Solid-State Circuits*, vol. 34, no. 12, pp. 1893-1903, Dec. 1999.

- [3] H. Darabi and A.A. Abidi, "Noise in RF-CMOS Mixers: A Simple Physical Model," *IEEE Journal of Solid-State Circuits*, vol. 35, no. 1, pp. 15-25, Jan. 2000.

- [4] A. A. Abidi, J. C. Leete, "De-Embedding the Noise Figure of Differential Amplifiers," *IEEE Journal of Solid-State Circuits*, vol. 34, no. 6, pp. 882-5, June 1999.

- [5] Third Generation Partnership Project (3GPP), "UE Radio Transmission and Reception(FDD)," Technical Specification 25.101, Vol. 3.3.0, June 2000, [Online], http://www.3gpp.org.

- [6] R. G. Meyer, et al., "Blocking and Desensitization in RF Amplifiers," IEEE Journal of Solid-State Circuits, vol. 30, no. 8, pp. 944-946, Aug. 1995.

- [7] A. R. Shahani, et al., "A 12-mW Wide Dynamic Range CMOS Front-End for a Portable GPS Receiver," *IEEE Journal of Solid-State Circuits*, vol. 32, no. 12, pp. 2061-70, Dec. 1997.

- [8] J. R. Long, et al., "A 5.1-5.8GHz Low-Power image-Reject Down converter in SiGe Technology," IEEE 1999 BCTM, pp. 67-70.

- [9] A-S. Porret, et al., "A 1V, 1mW, 434 MHz FSK Receiver fully integrated in a Standard Digital CMOS Process," IEEE 2000 Custom Integrated Circuits Conference, May 2000, pp. 171-4.

- [10] J. Ryynanen, et al., "An RF Front-End for the Direct-Conversion WCDMA Receiver," 1999 IEEE Radio Frequency Integrated Circuits symposium, June 1999, pp. 21-4.

- [11] F. Behbahani, et al., "A 2.4GHz Low-IF Receiver for Wideband WLAN in 0.6-µm CMOS", IEEE Journal of Solid-State Circuits, vol. 35, no. 12, pp. 1908-1916, Dec. 2000.

Fig. 1. Merged LNA and Mixer for 2.14 GHz direct conversion front-end

Fig. 2. (a) VCO circuit. (b) VCO buffer. (c) Measured phase noise at 2.1 GHz, with WCDMA RX phase noise specs overlaid.

Fig. 3. Test chip photo.

Fig. 4. Matching circuit with sliding capacitor on a differential transmission line.

Fig. 5. Input Matching (s<sub>11</sub>) Measurements vs. Simulations.

Fig. 6. Measured Gain & Noise Figure on four chips, averaged vs. simulation.

Fig. 7. Low frequency Noise Measurement vs. Simulations.

Fig. 8. Input 3rd Order Intercept Point.