# A 30 GHz 90-nm CMOS Passive Subharmonic Mixer with 15 GHz Differential LO

Wernehag, Johan; Sjöland, Henrik

Published in:

[Host publication title missing]

DOI:

10.1109/NORCHP.2008.4738296

2008

# Link to publication

Citation for published version (APA):

Wernehag, J., & Sjöland, H. (2008). A 30 GHz 90-nm CMOS Passive Subharmonic Mixer with 15 GHz Differential LO. In *[Host publication title missing]* (pp. 123-126). IEEE - Institute of Electrical and Electronics Engineers Inc.. https://doi.org/10.1109/NORCHP.2008.4738296

Total number of authors:

### General rights

Unless other specific re-use rights are stated the following general rights apply:

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

• You may not further distribute the material or use it for any profit-making activity or commercial gain

- You may freely distribute the URL identifying the publication in the public portal

Read more about Creative commons licenses: https://creativecommons.org/licenses/

Take down policy

If you believe that this document breaches copyright please contact us providing details, and we will remove access to the work immediately and investigate your claim.

**LUND UNIVERSITY**

**PO Box 117** 221 00 Lund +46 46-222 00 00

Download date: 18. Dec. 2025

# A 30 GHz 90-nm CMOS Passive Subharmonic Mixer with 15 GHz Differential LO

Johan Wernehag and Henrik Sjöland Department of Electrical and Information Technology Lund University, Box 118, 221 00 Lund Sweden Email: {Johan.Wernehag, Henrik.Sjoland}@eit.lth.se

Abstract—A new passive subharmonic mixer topology is presented and compared to a previously published passive topology. The comparison is conducted using simulations at 30 GHz with a 90-nm CMOS design kit.

The advantage of the new passive subharmonic mixer is that it only requires a differential local oscillator (LO) signal, compared to the previously published mixer that requires a quadrature LO signal. The mixer consists of two cascaded passive mixers with an interstage second order filter suppressing harmonics while providing some 10 dB of voltage gain at the LO frequency.

The noise performance of the differential mixer is slightly worse than for the quadrature one, with a simulated down conversion SSB NF of 10 dB compared to 7 dB. The voltage conversion gain is -1 dB for both mixers, all with a 1 V LO amplitude.

### I. Introduction

A wide range of applications use frequency bands located at several tens of gigahertz, e. g. automotive radar (24 GHz and 77 GHz) and WLAN/WPAN (60 GHz). To make these applications penetrate the mass market the cost of the chip sets must be reduced, which is a drive and motivation to use CMOS technology also when implementing the analog and RF parts [1], [2].

The motivation to integrate automotive radar, also in the low cost segment cars, is high. The injuries from car collisions cost the society a lot both in medical bills and in human tragedies. Just in the United States (US) alone motor vehicle accidents accounted for 42,000 deaths, more than 5.3 million injuries, and over \$231 billion in economic losses in year 2000 [3]. The consumer electronics, WLAN/WPAN applications, is extremely cost sensitive, and to succeed a low cost solution is a must.

A drawback when it comes to high speed CMOS processes is the low supply voltage. It reduces the available dynamic range of receivers and the achievable output power of the transmitters. To overcome these disadvantages a beamforming transceiver can be used [4], [5]. Combining a beamforming transceiver and phased array antenna the system will have an increased antenna directivity ( $\propto$  the number of antennas) compared to a single antenna element [6]. The increased antenna directivity increases the strength of the signal to receive and at the same time reduces the level of interferers from other directions.

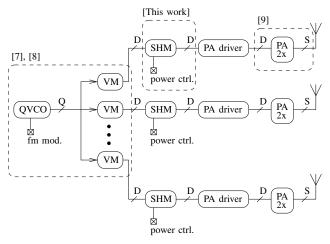

In Fig. 1 the proposed beamforming transmitter architecture is presented. The phase shifting to control the direction of the

beam is performed in the local oscillator (LO) path, by means of a quadrature to differential vector modulator (VM) [7], [8], one modulator for each transmitter path. A subharmonic mixer, presented in this paper, upconverts the phase shifted signal to twice the LO frequency. A power amplifier (PA) driver and a frequency doubling PA then converts the signal to four times the LO frequency and transforms the differential to a single-ended signal [9]. The LO thus runs at a quarter of the carrier frequency, which increases the tuning range of the LO and the robustness to parasitics. Furthermore, the vector modulator

Fig. 1. Proposed beamforming architecture with LO phase shifting. Q means quadrature signals, D differential, and S single-ended

could be simplified, as  $360^{\circ}$  at the the output corresponds to  $90^{\circ}$  at the LO, and thus it is sufficient to be able to steer the phase across one quadrant. The frequency (phase) modulation is inserted on the control voltage of the QVCO. The IF port of the subharmonic mixer is used to control the output power, and also to reduce the level of the side lobes.

Two of the three main building blocks have been presented earlier [7]–[9]. In this paper the third block, the subharmonic mixer (SHM), is addressed. A subharmonic passive mixer driven with quadrature LO was presented in [10]. It shows good performance but it is not suitable for a beamforming transmitter due to the quadrature LO needed. In a beamforming transmitter there are many transmit paths, and distributing the quadrature (phase shifted) LO across the chip to the mixers with sufficient signal quality is non-trivial and requires significant chip area and power consumption [11]. Distributing

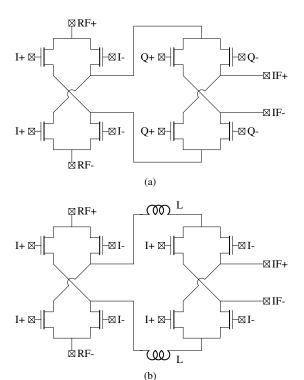

a differential signal is much easier. The demands on the vector modulators are also relaxed, since implementing vector modulators with differential output is less difficult than with quadrature output. An active SHM with differential LO was presented in [12]. The design uses two inductors, as does the proposed topology in Fig. 2(b). The hardware cost for the two mixers are about the same but the passive has less power consumption and is less complex. When used in a direct conversion receiver the passive mixer also has a 1/f noise advantage.

Therefore a comparison between the topology in [10], Fig. 2(a), and a novel topology presented in Fig. 2(b) is conducted.

# II. SUBHARMONIC MIXER TOPOLOGIES

The comparison is performed using a 90-nm CMOS design kit with BSIM4.3 transistor models [13]. The non-quasi static model of the transistors is used, Table I shows the BSIM4 user switch settings. All simulations were performed with the Cadence SpectreRF simulator.

TABLE I BSIM4.3 Transistor Model Switches

| acnqsmod = 1 | trnqsmod = 1 | rgatemod = 0 | mobmod = 2 |

|--------------|--------------|--------------|------------|

| rdsmod = 1   | igcmod = 1   | igbmod = 1   | capmod = 2 |

| rbodymod = 1 | diomod = 2   | pemod = 1    | geomod = 3 |

| rgeomod = 1  |              | _            |            |

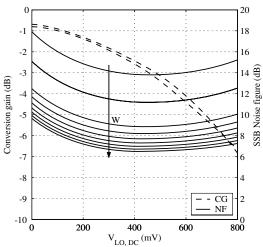

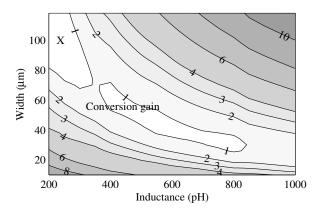

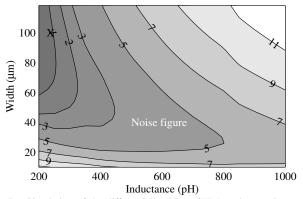

To determine the dimensions of the transistors and the LO bias voltage, parametric sweeps were performed and the voltage conversion gain (CG) and the single sideband noise figure (SSB NF) were plotted. The finger width was fixed to  $2 \mu m$  and the number of fingers was changed to change the width of the transistor. The transistor length was the minimum, 90 nm. To fit into the beamforming architecture presented in the introduction the LO frequency was 15 GHz, RF was 30 GHz, and the IF was zero. The LO was applied through a 5 pF DC-block capacitance while the bias was fed through a  $10 \text{ k}\Omega$  resistor with an effective resistance of  $3.8 \text{ k}\Omega$  at 15 GHz. The LO amplitude was held constant at 1 V peak, which can be achieved in a 1.2 V process. The higher the LO amplitude the better performance of the mixer. When simulating downconversion a differential capacitive load of 500 fF was applied at the IF side, and a resistive load of 300  $\Omega$  was applied at the RF side in up conversion simulations.

# A. Quadrature LO SHM

The dimensions of the transistors and the LO bias voltage were determined through a two-dimensional parametric sweep. In Fig. 3 the SSB NF and CG are plotted. The width was swept from 10  $\mu m$  to 100  $\mu m$  in steps of 10  $\mu m$ . The NF decreases with increasing width, while the CG just drops slightly. Only the CG at 10  $\mu m$  and 100  $\mu m$  are plotted. At 100  $\mu m$  the decrease in NF has flattened out, and the width of the transistors was thus chosen to 100  $\mu m$ . The CG is largest at zero LO bias while the NF reaches its minimum at 420 mV, thus a trade-off has to be made. Making the degradation from

Fig. 2. The two passive subharmonic mixer topologies. a) Quadrature LO. b) Differential LO

their optimum equal, a bias level of 210 mV was chosen, with a corresponding degradation of 0.6 dB. It can also be seen

Fig. 3. Simulation of down conversion voltage gain and SSB noise figure of the quadrature LO SHM, at an IF of 10 MHz. The width is swept from 10  $\mu$ m to 100  $\mu$ m in steps of 10  $\mu$ m

that the LO bias voltage and transistor size are orthogonal with respect to CG and NF.

With the transistor sizes and LO bias voltage now set, CG and NF versus frequency, and linearity were investigated. The 1-dB compression point referred to the RF side is 0.8 dBm, while CG and SSB NF remain constant at -1.4 dB and 7.0 dB, respectively, up to 1 GHz IF frequency the degradation is less than 1 dB. The up-conversion comparison between the two

topologies with respect to noise, gain, and compression point is presented in Section II-C.

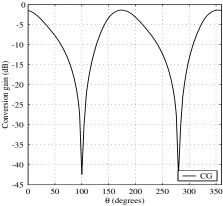

An LO signal with perfect quadrature is difficult to achieve and route across the chip. The sensitivity against quadrature phase error,  $\theta$ , was therefore simulated, see Fig. 4. The quadrature phase error stretches from 0 to 360 degrees and one can see that the order of Q+ and Q- is arbitrary (works well at  $180^{\circ}$  error), which can be valuable if the locking order of the QVCO is difficult to assure. It is also clear that the CG deteriorates as  $\theta$  approaches 90 and 270 degrees, thus a modification of the mixer is required to work with differential LO signals.

Fig. 4. Conversion gain vs. quadrature phase error

# B. Differential LO SHM

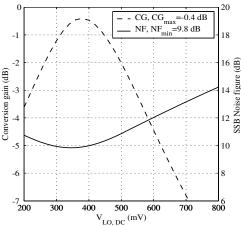

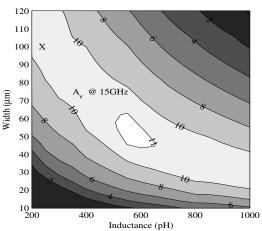

In the previous section it was observed that the effects of transistor width and LO bias voltage on CG and NF were orthogonal. Thus the transistor width and inductance are chosen first through a two dimensional parametric simulation. The LO bias voltage is then chosen through a separate simulation. The inductance and transistor width are connected together in the interstage filter function and thus have to be changed simultaneously. The inductors are spiral inductors supplied by the foundry, swept from 200 pH to 1 nH. Their Q-value at 15 GHz is above 18 for all sizes. Two-dimensional contour plots of the SSB NF and CG are presented in Fig. 5. The plots are normalized relative to the optimum value since the LO bias was not yet optimized. The conversion gain is best for a seemingly constant LC-product, corresponding to a peak in the filter function at the LO frequency, see Fig. 7. The SSB NF is also in this case the lowest for large transistors. A transistor width of 100  $\mu$ m and an inductance of 225 pH were chosen, indicated by the cross (X) in Fig. 5.

The LO bias level was swept and then set to 370 mV, which gives a CG and SSB NF of -0.43 dB and 9.9 dB, respectively, see Fig. 6. For the bias point selected the CG and NF deviates less than 0.5 dB from their optimum values. The noise figure of this mixer is 2.9 dB worse than the quadrature LO one.

The compression point at the RF side is -6.2 dBm. The CG and SSB NF are rather constant up to 1 GHz IF frequency, deviates less than 1 dB.

Fig. 5. Simulation of the differentially driven SHM as the transistor width and the inductance are swept, at 10 MHz IF. Top: Relative voltage conversion gain. Bottom: Relative single sideband NF

Fig. 6. Down conversion CG and SSB NF for the differentially driven SHM versus LO bias voltage, IF is  $10~\mathrm{MHz}$

# C. Up Conversion Comparison

The up conversion performance for both topologies is evaluated with respect of noise, gain, and 1-dB compression point (Fig. 8). The load at the RF side is 300  $\Omega$ , emulating the load of a tuned 30 GHz PA driver following the SHM. The SSB noise figure is 4 dB higher for up conversion than down conversion, 11 dB and 14 dB for the quadrature and differential LO SHM respectively. The 3-dB difference between the two topologies remain.

Fig. 7. Voltage gain for the 15 GHz tone of the interstage second order filter

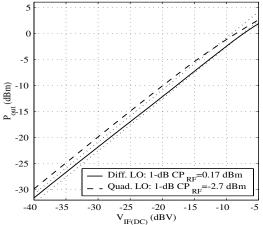

The voltage conversion gain, simulated with one RF tone and a DC IF input voltage, is 0.14 dB and -1.59 dB for the quadrature and differential LO SHM respectively. In Fig. 8 output power vs. input DC voltage is plotted and the 1-dB compression points are extracted, -2.7 dBm and 0.17 dBm for the quadrature and differential LO corresponding to an output voltage of 220 mV and 320 mV respectively over a 300  $\Omega$  load.

Fig. 8. Up-conversion output power vs. DC IF input voltage

# D. Summary

The performance and design parameters of the two SHM are summarized in Table II.

### III. CONCLUSION

A comparison between two passive SHM has been performed, one with quadrature LO and one with differential LO. The new mixer topology with differential LO uses a second order interstage filter to suppress high order harmonics and provide some 10 dB of voltage gain for the desired signal at the LO frequency. In a beamforming transceiver, with multiple receive and transmit paths, the LO generation (with or without phase shift) is performed at one place on the chip. The LO therefore needs to be distributed to all the mixers in the

TABLE II Performance and Design Parameter Summary

|                          | Down-Conversion |          | Up-Conversion |          |

|--------------------------|-----------------|----------|---------------|----------|

|                          | Quad. LO        | Diff. LO | Quad. LO      | Diff. LO |

| SSB NF (dB)              | 7               | 10       | 11            | 14       |

| CG (dB)                  | -1.4            | -0.4     | 0.14          | -1.6     |

| $RFCP_1$ (dBm)           | 0.8             | -6.2     | -2.7          | 0.2      |

| V <sub>LO, DC</sub> (mV) | 210             | 370      | 150           | 270      |

| $V_{LO, amp}(V)$         | 1               | 1        | 1             | 1        |

| Width $(\mu m)$          | 100             | 100      | 100           | 100      |

| Inductance (pH)          |                 | 225      | _             | 225      |

transceiver (Fig. 1), which is much easier with a differential than with a quadrature LO signal.

The differential subharmonic mixer, however, has some penalties in noise figure and chip area, but in a beamforming application the advantage of having of having differential LO signals is so large that these penalties in most cases can be accepted.

# IV. ACKNOWLEDGMENT

The authors would like to thank United Microelectronics Corporation (UMC) for giving us the opportunity to work with a state-of-the-art 90-nm CMOS process and the VINNOVA industrial excellence center System Design on Silicon for funding the research.

### REFERENCES

- B. Razavi, "Gadgets Gab at 60 GHz," *IEEE Spectrum*, vol. 45, no. 2, pp. 40–45, Feb. 2008.

- [2] S. K. Moore, "Cheap Chips for Next Wireless Frontier," *IEEE Spectrum*, vol. 43, no. 6, pp. 8–9, June 2006.

- [3] L. Blincoe, A. Seay, E. Zaloshnja, T. Miller, E. Romano, S. Luchter, and R. Spicer, "The Economic Impact of Motor Vehicle Crashes, 2000," *National Highway Traffic safety Administration*, May 2002, report NO. DOT HS 809 446.

- [4] A. Natarajan, A. Komijani, and A. Hajimiri, "A Fully Integrated 24-GHz Phased-Array Transmitter in CMOS," *IEEE Journal of Solid-State Circuits*, vol. 40, no. 12, pp. 2502–2514, Dec. 2005.

- [5] A. Hajimiri, H. Hashemi, A. Natarajan, X. Guan, and A. Komijani, "Integrated Phased Array Systems in Silicon," *Proceedings of the IEEE*, vol. 93, no. 9, pp. 1637–1655, Sep. 2005.

- [6] R. J. Mailloux, Phased Array Antenna Handbook, 2nd ed. Norwood, MA: Artech House Books, 2005.

- [7] J. Wernehag and H. Sjöland, "An 8-GHz Beamforming Transmitter IC in 130-nm CMOS," in *IEEE Radio Frequency Integrated Circuits Symposium*, July 2007, pp. 577–580.

- [8] —, "A 24-GHz Automotive Radar Transmitter with Digital Beam Steering in 130-nm CMOS," in Ph. D. Research in Microelectronics and Electronics, June 2006, pp. 481–484.

- [9] —, "60 GHz 130-nm CMOS Second Harmonic Power Amplifiers," in *IEEE Asia Pacific Conference on Circuits and Systems (APCCAS)*, Accepted 2008.

- [10] R. M. Kodkani and L. E. Larson, "A 24-GHz CMOS Passive Subharmonic Mixer/Downconverter for Zero-IF Applications," *IEEE Transactions on Microwave Theory and Techniques*, vol. 56, no. 5, pp. 1247–1256, May 2008.

- [11] E. Mensink, D. Schinkel, E. A. M. Klumperink, E. van Tuijl, and B. Nauta, "Optimal Positions of Twists in Global On-Chip Differential Interconnects," *IEEE Transactions on very Large Scale Integration* (VLSI) Systems, vol. 15, no. 4, pp. 438–446, Apr. 2007.

- [12] A. Parsa and B. Razavi, "A 60GHz CMOS Receiver Using a 30GHz LO," in *IEEE International Solid-State Circuits Conference, Digest of Technical Papers*, Feb. 2008, pp. 190–606.

- [13] BSIM Research Group, "BSIM4.3.0 MOSFET Model," http://www-device.eecs.berkeley.edu/~bsim3/bsim4.html.