#### Receiver Front-Ends in CMOS with Ultra-Low Power Consumption

Bryant, Carl

2013

#### Link to publication

Citation for published version (APA):

Bryant, C. (2013). Receiver Front-Ends in CMOS with Ultra-Low Power Consumption. [Doctoral Thesis (compilation), Department of Electrical and Information Technology]. Department of Electrical and Information Technology, Lund University.

Total number of authors:

General rights

Unless other specific re-use rights are stated the following general rights apply:

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

• Users may download and print one copy of any publication from the public portal for the purpose of private study

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal

Read more about Creative commons licenses: https://creativecommons.org/licenses/

Take down policy

If you believe that this document breaches copyright please contact us providing details, and we will remove access to the work immediately and investigate your claim.

# Receiver Front-Ends in CMOS with Ultra-Low Power Consumption

Carl Bryant

Doctoral Thesis Lund, September 2013

Carl Bryant

Department of Electrical and Information Technology

Lund University

P.O. Box 118, 221 00 Lund, Sweden

Series of licentiate and doctoral dissertations ISSN 1654-790X; No. 53 ISBN 978-91-7473-707-3 (print) ISBN 978-91-7473-708-0 (pdf)

© 2013 Carl Bryant Typeset in Palatino and Helvetica using  $\LaTeX$ 2 $_{\epsilon}$ . Printed in Sweden by Tryckeriet i E-huset, Lund University, Lund.

No part of this dissertation may be reproduced or transmitted in any form or by any means, electronically or mechanical, including photocopy, recording, or any information storage and retrieval system, without written permission from the author.

## **Abstract**

Historically, research on radio communication has focused on improving range and data rate. In the last decade, however, there has been an increasing demand for low power and low cost radios that can provide connectivity with small devices around us. They should be able to offer basic connectivity with a power consumption low enough to function extended periods of time on a single battery charge, or even energy scavenged from the surroundings. This work is focused on the design of ultra-low power receiver front-ends intended for a receiver operating in the 2.4 GHz ISM band, having an active power consumption of 1 mW and chip area of 1 mm<sup>2</sup>. Low power consumption and small size make it hard to achieve good sensitivity and tolerance to interference. This thesis starts with an introduction to the overall receiver specifications, low power radio and radio standards, front-end and LO generation architectures and building blocks, followed by the four included papers.

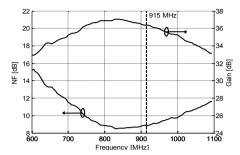

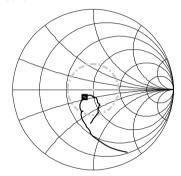

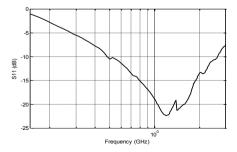

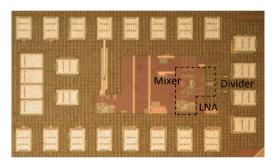

Paper I demonstrates an inductorless front-end operating at 915 MHz, including a frequency divider for quadrature LO generation. An LO generator operating at 2.14 GHz is shown in Paper II, enabling a front-end operating above 2 GHz. Papers III and IV contain circuits with combined front-end and LO generator operating at or above the full 2.45 GHz target frequency. They use VCO and frequency divider topologies that offer efficient operation and low quadrature error. An efficient passive-mixer design with improved suppression of interference, enables an LNA-less design in Paper IV capable of operating without a SAW-filter.

# Populärvetenskaplig sammanfattning

I avhandlingen presenteras delar till radiomottagare med extremt låg effektförbrukning. Detta behövs då dagens samhälle blir allt mer och mer uppkopplat, och detta gäller inte bara persondatorer och mobiltelefoner. Med den snabba teknikutvecklingen inom radiokommunikation, driven av små och smarta mobiltelefoner, går det nu även att få prylar av alla de slag att tala med varandra. I förlängningen strävas det efter att i princip allting i ens omgivning ska kunna kommunicera trådlöst. Bland annat ska små givare kunna sättas lite överallt för insamling av data i så kallade sensornätverk. Till exempel kan de användas i smarta hus för att hålla reda på luftkvalitet och temperatur, och för att styra belysning och liknande. Sensornätverk kan också användas för att hålla reda på belastningar i en struktur vid t.ex. byggnadsarbeten. De kan även komma till användning på och även i kroppen. Det kan då handla om medicinska sensorer, som håller koll på din hälsa, och kontinuerligt vidarebefordrar informationen till en mobiltelefon eller kanske även till sjukvården. Redan idag har vi enkla trådlösa sensorer för att hålla reda på hjärtrytm och stegfrekvens vid sportutövning. Utvecklingen av effektsnåla trådlösa sensorer är dock ännu i sin linda. Några steg har redan tagits, med sport-sensorer och nya trådlösa standarder som Bluetooth Smart och ANT, men vi kommer nog att se vilken potential de har först när tekniken är bättre utvecklad.

Sensorerna behöver klara sig länge på en batteriladdning, vilket i vissa fall som med trådlösa möss och tangentbord, kan lösas med hjälp av relativt stora batterier. För att verkligen kunna sprida sensorer överallt måste de dock kunna göras mycket små och trots det ha en lång batteritid; i många fall kan det handla om flera år. För att klara av detta behövs nya radiokretsar och kommunikationsstandarder som är mycket bättre optimerade för låg effektförbrukning än dagens lösningar.

Avhandlingens syfte var att ta fram de analoga byggblocken i en extremt effektsnål radio. Delarna det handlar om sitter direkt vid antennen (front-end) och har som funktion att ta emot radiosignalen, förstärka den, och flytta ner den till en mycket lägre frekvens som kan hanteras av resten av radion. Den här delen av radion måste alltså hantera de högfrekventa radiosignalerna, och kretsarna måste därför vara snabba nog. Eftersom strömförbrukningen i en krets är i stort sett proportionell mot hastigheten är det svårt att bygga radiokretsar med mycket låg effektförbrukning, och i små trådlösa sensorer är det de analoga radiokretsarna som kräver mest ström. Därför är det mycket viktigt att de använder strömmen så effektivt som möjligt. Ytterligare ett problem vid konstruktionen av kretsar med låg strömförbrukning är att de har svårare att hantera stora signalstyrkor med låg distorsion (olinjäritet). Det innebär är att radion får svårare att klara av starka störsignaler. Mottagaren är tänkt att fungera i det licensfria 2.4GHz-bandet, som dessutom används av bland annat trådlösa hemnätverk (WiFi), Bluetooth-enheter och mikrovågsugnar. Alla dessa riskerar att störa ut en mottagare utan tillräcklig linjäritet.

Arbetet har utförts som en (i stort sett oberoende) del av ett större projekt med målet att utveckla alla delarna (analoga och digitala) av en radiomottagare med låg effekt. Målet har varit att kunna ta emot en signal i det öppna 2.4GHz-bandet med datatakt på 250kbit/s, med en total strömförbrukning av 1mW, viket är ett rätt så aggressivt mål. Ytterligare ett mål har varit att få in hela mottagarkjedjan på ett 1x1mm² chip. För att t.ex. kunna hantera kommunikation mellan två hörapparater eller andra enheter på olika delar av kroppen bör mottagaren dessutom ha god känslighet.

Avhandlingen har undersökt flera varianter av "front-end"-kretsar. Den första är konstruerad helt utan induktanser på chip för att den ska vara så fysiskt liten som möjligt (induktanser/spolar kan inte göras lika små på chip som andra komponenttyper). Den har en effektförbrukning på  $280\mu$ W och arbetar vid 915MHz. Nästa front-end klarar att arbeta vid 2.4GHz tack vare en ovanligt kompakt spole, och är dessutom mer komplett då den även innehåller en källa som genererar referenssignalen som behövs

för att stämma av mottagaren till en viss frekvens. Den sista front-end-kretsen lyckas kraftigt förbättra undertryckningen av störsignaler utan att nämnvärt höja effektförbrukningen. Undertryckningen av störningar är i nivå med mottagare som normalt brukar kräva minst tio gånger mer effekt.

# Contents

| C  | ontei | nts                            | vii  |

|----|-------|--------------------------------|------|

| Pı | efac  | e                              | xi   |

| A  | ckno  | wledgments                     | xiii |

| Li | st of | Acronyms                       | xv   |

| Li | st of | Symbols                        | xix  |

| Iı | ntrod | luction                        | 1    |

| 1  | Mo    | tivation                       | 3    |

| 2  | Ult   | ra Portable Devices            | 5    |

|    | 2.1   | UPD Sub-projects               | 5    |

|    | 2.2   | UPD System Overview            | 7    |

|    |       | 2.2.1 Receiver Architecture    | 8    |

|    |       | 2.2.2 Modulation               | 9    |

|    |       | 2.2.3 Link Budget              | 10   |

|    |       | 2.2.4 MAC protocol             | 12   |

|    |       | 2.2.5 Handling of Interference | 13   |

| 3  | Lov   | v Power Radio                  | 17   |

|    | 3.1   | Network configurations         | 18   |

|    | 3.2   | Low power radio standards            | 19<br>19<br>19<br>20 |

|----|-------|--------------------------------------|----------------------|

| 4  | Rec   | eiver Front-end                      | 21                   |

|    | 4.1   | Architecture                         | 21                   |

|    |       | 4.1.1 Hetrodyne                      | 21                   |

|    |       | 4.1.2 Homodyne/Direct conversion     | 22                   |

|    | 4.2   | LO Generation                        | 23                   |

|    |       | 4.2.1 Quadrature generator           | 23                   |

|    |       | 4.2.2 PLL                            | 25                   |

|    | 4.3   | Building Blocks and Components       | 26                   |

|    |       | 4.3.1 LNA                            | 26                   |

|    |       | 4.3.2 MIXER                          | 33                   |

|    |       | 4.3.3 Oscillator                     | 36                   |

|    |       | 4.3.4 Frequency divider              | 39                   |

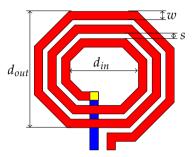

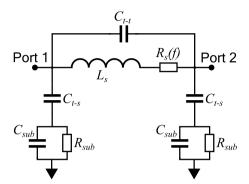

|    |       | 4.3.5 Inductors                      | 40                   |

|    | 4.4   | Low Power Front-end Design           | 44                   |

|    |       | 4.4.1 Survey of Low Power Front-ends | 44                   |

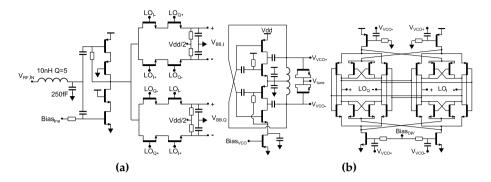

|    |       | 4.4.2 Summary, Paper I               | 45                   |

|    |       | 4.4.3 Summary, Paper II              | 46                   |

|    |       | 4.4.4 Summary, Paper III             | 47                   |

|    |       | 4.4.5 Summary, Paper IV              | 48                   |

|    |       | 4.4.6 Performance summary            | 50                   |

| Bi | bliog | graphy                               | 53                   |

| I A 65nm CMOS 282 $\mu$ W 915MHz Direct Conversion Receiver Front-end            | 59 |

|----------------------------------------------------------------------------------|----|

| II A 65-nm CMOS 250uW Quadrature LO Generation Circuit                           | 67 |

| III A 2.45GHz Ultra-Low Power Quadrature Front-End in 65nm CMOS                  | 75 |

| IV A 0.55mW SAW-less Receiver Front-end for Bluetooth<br>Low Energy Applications | 83 |

## **Preface**

The first part of this thesis consists of an introduction and gives a general overview of the field of study. The main scientific contribution is in the papers attached at the end, and consists of:

- [1] C. Bryant and H. Sjöland, "A 65nm CMOS 282 μW 915MHz Direct Conversion Receiver Front-end," *Proceedings of the European Solid State Circuits Conference (ESSCIRC)*, 2011, pp. 547–550, 2011.

- [2] C. Bryant and H. Sjöland, "A 65-nm CMOS 250uW Quadrature LO Generation Circuit," *International Microwave Symposium Digest (MTT)*, 2012 IEEE MTT-S, 2012 IEEE, 2012.

- [3] C. Bryant and H. Sjöland, "A 2.45GHz Ultra-low Power Quadrature Frontend in 65nm CMOS," *Radio Frequency Integrated Circuits Symposium (RFIC)*, 2012 IEEE, pp. 247–250, 2012.

- [4] C. Bryant and H. Sjöland., "A 0.55mW SAW-Less Receiver Front-end for Bluetooth Low Energy Applications," *IEEE J. Solid-State Circuits [Submitted]*.

The research work included in this dissertation is funded by SSF – Swedish Foundation for Strategic Research

In addition to the papers included as part of the dissertation, I have authored or co-authored the following works:

- [5] K.-K. Lee, C. Bryant, M. Törmänen, and H. Sjöland, "A 65-nm CMOS Ultralow-power LC Quadrature VCO," NORCHIP, 2009, pp. 1–4, 2009.

- [6] H. Sjöland, C. Bryant, V. Bassoo, and M. Faulkner, "Switched mode transmitter architectures," in *Analog Circuit Design*, pp. 325–342, Springer, 2010.

- [7] C. Bryant and H. Sjöland, "A 175  $\mu$ W 100MHz-2GHz Inductorless Receiver Frontend in 65nm CMOS," *in NORCHIP*, 2010, pp. 1–4, Nov. 2010.

- [8] K. K. Lee, C. Bryant, M. Törmänen, and H. Sjöland, "Design and Analysis of an Ultra-low-power LC Quadrature VCO," *Analog Integrated Circuits and Signal Processing*, vol. 67, no. 1, pp. 49–60, 2011.

- [9] J. Lindstrand, C. Bryant, M. Törmänen, and H. Sjöland, "A 1.6-2.6GHz 29dBm Injection-locked Power Amplifier with 64% peak PAE in 65nm CMOS," in ESSCIRC (ESSCIRC), 2011 Proceedings of the, pp. 299–302, 2011.

- [10] H. Sjöland, J. B. Anderson, C. Bryant, R. Chandra, O. Edfors, A. J. Johansson, N. S. Mazloum, R. Meraji, P. Nilsson, D. Radjen, et al., "A Receiver Architecture for Devices in Wireless Body Area Networks," *Emerging and Selected Topics in Circuits and Systems, IEEE Journal on*, vol. 2, no. 1, pp. 82–95, 2012.

- [11] C. Bryant, J. Lindstrand, H. Sjöland, and M. Törmänen, "A 70 and 210 GHz LO Generator in 65nm CMOS," in Radio-Frequency Integration Technology (RFIT), 2012 IEEE International Symposium on, pp. 195–197, 2012.

#### Patents & patent applications

- [12] C. Bryant, "Pulse-width modulator methods and apparatus," July 2010. US Patent 7,760,041.

- [13] C. Bryant, "Pulse-elimination pulse-width modulation," Jan. 2011. US Patent 7,863,956.

- [14] C. Bryant, "Quadrature pulse-width modulation methods and apparatus," May 2012. US Patent 8,179,957

- [15] J. Lindstrand, C. Bryant, and H. Sjöland, "High efficiency power amplifier," Feb. 2013, US Patent application 2013/0033,321.

# Acknowledgments

I would like to acknowledge those who have helped me in my PhD work, or just made my time a memorable experience.

Fist of all I would like to extend my gratitude to my supervisor, Professor Henrik Sjöland. He appears to know something about pretty much everything, is rarely stumped, and knows how to get to the core of a problem.

Thanks to past and present members of the Analog RF group for friendship and inspiration. I should neither forget the friendly people elsewhere in the department, especially in the Digital/mixed signal corridor. In fact I have a debt of gratitude to a large part of the department, so I had better not even try to list everyone, lest I forget someone.

A thank you to the staff that are always helpful and keep the wheels of the department moving, including administration, CAD and computer support and printing; including, but not limited to Pia Bruhn, Stefan Molund, Erik Jonsson, Lars Hedenstjerna, etc.

Special thanks to Göran Jönsson, one of the most patient persons I know, for a fruitful cooperation over the years in the Radio courses.

Oh, and I should not forget Lars Olsson, a character like no other, for, among other things, reading through parts of this thesis when Henrik was away.

Lastly, I would like to thank my mother and father who are always there.

It is very hard to acknowledge everyone who have been important to me in my time here, so perhaps I should try a different approach:

To whom it may concern:

Thanks!

# List of Acronyms

ADC Analog-to-Digital Converter

AGC Automatic Gain Control

BAN Body Area Network

BB Baseband

BER Bit Error Rate

BFSK Binary Frequency Shift Keying

BLE Bluetooth Low Energy

BT Bluetooth

BW Bandwidth

CG Common Gate

CML Current Mode Logic

CMOS Complementary Metal Oxide Semiconductor

CS Common Source

DAC Digital-to-Analog Converter

DC Direct Current

DR Dynamic Range

$\Delta\Sigma$  Delta Sigma

ESD Electro-Static Discharge

F Noise Factor

FET Field Effect Transistor

FOM Figure of Merit

FSK Frequency Shift Keying

GFSK Gaussian Frequency Shift Keying

GPS Global Positioning System

IC Integrated Circuit

ICP<sub>1dB</sub> Input referred 1dB Compression Point

IF Intermediate Frequency

IIP<sub>2</sub> Input referred Second-Order Intercept Point

IIP<sub>3</sub> Input referred Third-Order Intercept Point

IL Insertion Loss

IM Intermodulation

IM<sub>2</sub> Second order intermodulation

IRR Image Rejection Ratio

ISM Industrial Scientific Medical

LNA Low Noise Amplifier

LPF Low Pass Filter

LO Local Oscillator

MAC Media Access Control

MOS Metal Oxide Semiconductor

NF Noise Figure

NMOS N-channel Metal Oxide Semiconductor

NR Noise Ratio

OFDM Orthogonal Frequency-Division Multiplexing

OOK On-Off Keying

P2P Point-to-Point

PAR Peak-to-Average Ratio

PCB Printed Circuit Board

PhD Doctor of Philosophy

PLL Phase Locked Loop

PMOS P-channel Metal Oxide Semiconductor

PN Phase Noise

PVT Process, Voltage, Temperature

SAW Surface Acoustic Wave

SNR Signal to Noise Ratio

SRF Self Resonance Frequency

Q Quality factor

QAM Quadrature Amplitude Modulation

QVCO Quadrature Voltage Controlled Oscillator

RF Radio Frequency

VCO Voltage Controlled Oscillator

V<sub>DD</sub> Supply Voltage

WUR Wake-up Receiver

WSN Wireless Sensor Network

XO Crystal Oscillator

# List of Symbols

$C_{gs}$  Gate to source parasitic capacitance

$\Delta\omega$  Offset angular frequency

Eb Energy per bit

$F_{min}$  Minimum achievable noise factor  $NF_{min}$  Minimum achievable noise figure

$f_{LO}$  Local oscillator frequency

$f_{RF}$  Radio frequency

$f_T$  Transition frequency

$g_m$  Transconductance

i<sub>n</sub> Noise current

k Boltzmann's constant

$\mathcal{L}\left(\Delta\omega\right)$  Phase noise at certain offset frequency

No Noise power density  $P_{int}$  Power of interferer

$PN_{1MHz}$  Relative phase noise at 1 MHz offset

$R_S$  Source resistance

T Temperakture

$Z_{in}$  Input impedance

$\omega_0$  Resonance angular frequency

# Introduction

# Motivation

With the advent of widespread computer networks, both wired and wireless, the world is becoming ever more connected. It is now possible to access services and information from pretty much anywhere in the world using a smartphone small enough to be held in one hand. The next step in the wireless revolution, the connection of all the things around us to the wider world, popularly referred to as the Internet of Things, has only just taken its first tentative steps. Currently we have low power wireless connectivity with a few select items, such as Bluetooth headsets, keyboards, game controllers, heart rate monitors, etc. While not really a true internet of things, the radios in such devices need to solve the same basic problem of providing basic connectivity at all times, while consuming hardly any power at all. My home keyboard, for example, is rated to last three years on a couple of AA batteries. This is all well and good, but in order to put wireless connectivity just about everywhere, we need devices that can operate at least that time on a single button cell battery, or even energy scavenged from the surroundings.

To achieve this level of portability we need transceivers capable of operating with minimal power consumption. One of, if not the main power consumer in such a device, is the RF front-end. Having to operate at high frequencies compared to the baseband circuits, the RF circuits need to draw a comparatively high current just to function properly. Thus, we need efficient circuit designs that use every drop of current exactly where it is needed, and where as few parts as possible operate at radio frequencies. To enable placement of such devices all around us, they should be as cheap as possible. For this purpose it is advantageous to produce such a device in a CMOS process. CMOS technology is used primarily for digital circuits such as processors, but since the unit cost is low when manufactured on a large scale, its use for analog circuits has also become common. Although initially too slow to make it particularly

4 Motivation

suitable for the implementation of radio circuits, CMOS technology has undergone a remarkable scaling over the past decades. With Moore's "Law" predicting a doubling of transistors in integrated circuits approximately every two years, the devices are now so small that more than a billion of them can be fitted into a high performance CPU. As the feature sizes have shrunk, the intrinsic speed has increased to the point where CMOS is suitable for high performance RF circuits. With the advanced processes available today, CMOS has become so fast that we can afford to trade away some of that speed for increased efficiency, and in turn open up the opportunity to operate RF circuits at very low power.

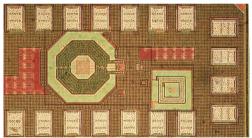

This thesis focuses on the design of receiver front-ends with ultra-low power consumption, implemented in CMOS. Different circuits have been designed exploring different performance metrics, as well as incrementally advancing overall performance. The first front-end presented in this thesis explores a fully inductorless implementation at a lower operating frequency. It was early determined that LO generation circuits had to be included to give a fair representation of the overall performance under realistic circumstances, so the next circuit is a basic LO-generation circuit, demonstrating low power operation at above 2 GHz. The next circuit is a front-end operating at the full 2.45 GHz target frequency, together with an integrated LO-generation circuit. It departs slightly from the previous inductorless approach, demonstrating improved performance with a highly compact inductor. This circuit essentially fulfills the initial design targets. The front-end after that demonstrates operation without the LNA, and greatly improves tolerance to interference for slight increases in size and power consumption.

This work is not intended as a text book on the design of low power frontends. To put the work into perspective, however, the following chapters provide an introduction to the project as well as some background information on receiver front-ends, the necessary building blocks, and issues faced in their design.

This research has been conducted within the wider project "Wireless Communication for Ultra Portable Devices", UPD in short, funded by SSF — Swedish Foundation for Strategic Research. The goal of this project is to buld a radio receiver for operation in ultra-low power devices, such as sensor nodes or medical devices or similar. Some project targets are shown in Table 2.1. Apart from a small chip area, the receiver should have as few external components as possible to further aid portability.

Table 2.1: Project targets

| Active power consumption | 1 mW              |

|--------------------------|-------------------|

| Data rate                | 250kbps           |

| Operating frequency      | 2.45 GHz          |

| Chip area                | 1 mm <sup>2</sup> |

The project is divided into six sub-projects with one PhD student in each. Although each person has primarily been responsible for one part, there has been common work to study overall receiver and system functionality, such as finding more detailed specifications. An overview of the proposed system can be found in a joint journal paper from 2012 [10].

#### 2.1 UPD SUB-PROJECTS

#### Antenna design/Channel modeling, Rohit Chandra

Small, compact antennas have been investigated combined with channel modeling of primarily on-body communication, such as ear-to-ear communication between hearing aids. The information obtained has

been taken into account in the overall system design specifications, so that it will function even in some of the tougher use cases of on-body communication.

#### Front-end, Carl Bryant

The sub-project described in this dissertation. The basic function of the front-end is to receive a weak RF signal from the antenna, amplify it and shift it to a much lower frequency range where it can be more easily processed. It is in the front-end and associated local oscillator (LO) signal generation we encounter the highest frequency circuits, since they have to operate at the full frequency of the incoming radio signal. Fast circuits generally have high power consumption, and so the majority of our power budget will be needed by the RF circuits. As the first active part of the receiver chain the performance of the front-end is what ultimately limits the overall sensitivity and tolerance to interference. Thus we need carefully optimized circuits that makes use of every bit of power it draws, and without too large sacrifices in performance.

#### Analog to digital converters, Dejan Radjen

The goal is to design an analog to digital converter (ADC) with sufficient dynamic range so that the receiver may operate without automatic gain control, while still maintaining small size and low power consumption. Continuous time Delta Sigma ( $\Delta\Sigma$ ) converters are considered to be a suitable architecture. The advantage of  $\Delta\Sigma$  converters is that it can use a low resolution quantizer, trading speed for resolution, advantageous with the high inherent speed of advanced CMOS processes available also at low power. The main advantage of the continuous time  $\Delta\Sigma$  is that the loop filter, implemented in the analog domain, also functions as an anti-aliasing filter, relaxing the filtering requirements before the ADC.

#### Digital baseband, Yasser Sherazi

The digital baseband includes decimation and sharp channel filtering, as well as synchronization and demodulation. While coarse filtering is performed in the analog domain early in the signal chain, digital filters allow a much sharper cutoff. This subproject is concerned with finding optimized structures and efficient implementations. One of the fundamental trade-offs in digital circuitry implemented in an advanced CMOS node is speed versus leakage current. Techniques that trade these include series versus parallel logic, use of multiple thresholds, bulk biasing, etc.

#### Analog Decoder, Reza Meraji

In situations with poor signal transfer, error correcting codes can trade data rate for fidelity by adding redundancy to the data. Traditionally the decoding of such signals is performed in the digital domain. The decoder circuits can be fairly complex and it is believed that performing the computations in the analog domain may actually be faster and more power efficient, possibly by orders of magnitude [16]. An example of an operation that may be more efficient in the analog domain is multiplication. In the digital domain it is costly, while in the analog domain a multiplication can be performed using only a handful of devices. The main issues with analog computations are the susceptibility to noise and particularly device mismatch. Although both can be mitigated by making the devices large enough, this will make the circuits slower and also a large physical size may be an issue when used in a device meant to be compact and very cheap to manufacture. Methods of mitigating the effect of mismatch other than increasing the device size should therefore be sought. To test the viability of analog decoders, they should be compared to equivalent digital implementations. The results to date are very promising with an analog decoder substantially outperforming its digital counterpart in simulations, both in terms of power consumption and size [17].

#### System Control, Nafiseh Mazloum

The system control concerns the proper and efficient operation of the receiver in different situations. In practice this to a large extent involves the study and design of the media access control (MAC) protocol for a low power sensor network. The MAC describes the fundamental operations performed to establish a link and transfer data. How this is performed can be just as important to achieving low power operation as the circuits themselves. We expect the data requirements for the target applications to be small and infrequent. If the radio circuits can be powered down when there is no data the average power consumption can then be reduced substantially, but this has to be performed without incurring an unacceptable latency. The work done in this area has shown the potential power savings that can be achieved by introducing a separate ultra-low power wake-up receiver. This is discussed further in section 2.2.4.

#### 2.2 UPD SYSTEM OVERVIEW

To get a better understanding of how the front-end is intended to function together with its surroundings, we should look at the system as a whole,

i.e. the front-end together with the rest of the receiver chain. In a paper from 2012 the intended architecture of the Ultra Portable Devices receiver is presented together with an analysis of some of the basic specifications [10]. In this case we have assumed an application of communication between two hearing aids. When using hearing aids for both ears simultaneously, they need to keep synchronized for best performance. This is one of the tougher examples of on-body communication since radio energy is quickly absorbed by the body and the radio waves thus have to propagate around the head.

The receiver is intended to operate in the 2.4 GHz ISM (Industrial, Scientific, Medical) band (2400-2483 MHz). Lower frequencies require larger antennas for efficient radiation, while losses tend to increase with higher frequencies. The 2.4 GHz band is deemed to offer a fair trade-off, but more importantly the ISM-band provides 80 MHz of unlicensed bandwidth. Additionally it is adjacent to a band recently approved for medical body area networks at 2360-2400 MHz, of which the top 10 MHz requires no registration or coordination [18].

#### 2.2.1 RECEIVER ARCHITECTURE

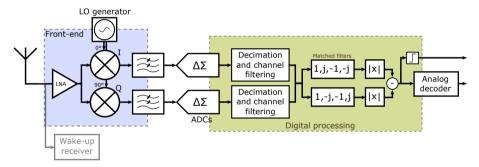

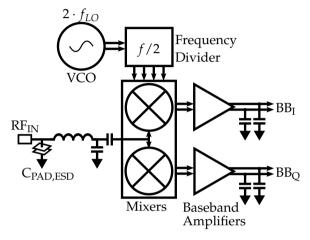

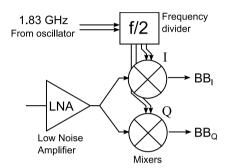

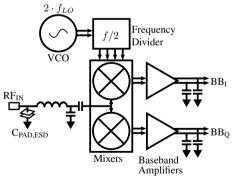

Figure 2.1: Proposed receiver structure

The proposed receiver architecture is shown in figure 2.1. It consists of a direct conversion front-end, ADCs and a digital demodulator. Coding may be used when the signal to noise ratio (SNR) is low. In this case an analog decoder is used since it is reckoned to be power efficient (See section 2.1). Although the analog decoder requires digital to analog converters (DAC) the resolution needed is low enough that they shouldn't require much power. At  $100\,\mu\text{W}$  each it is reckoned that the ADCs can achieve more than  $50\,\text{dB}$  SNDR [10] which should give the receiver sufficient dynamic range (DR) to minimize the need for automatic gain control (AGC).

The 1 mW power budget is designated as follows: The synthesizer and

front-end should together draw  $650\,\mu\text{W}$ . The ADCs are each allocated  $100\,\mu\text{W}$ , the digital baseband  $100\,\mu\text{W}$  and decoder  $50\,\mu\text{W}$ . The work on digital baseband and analog decoders indicates that the power required will be considerably less than this, so there is likely room to reallocate some of that power.

#### 2.2.2 MODULATION

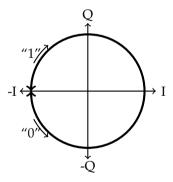

The system is intended to use wideband frequency shift keying (FSK) as it has several properties especially well suited for a low power transceiver. The modulation index is chosen such that the frequency deviation and data rates match (250 kbit/s,  $\pm 250$  kHz). This results in a full 360° change of phase each symbol. The data is encoded in the direction of rotation, with an advancing phase encoding a "1" and a retreating phase a "0". Fig. 2.2 shows this phase rotation in the I/Q-plane. We see that as the signal spends an equal time at all phase positions, the I and Q signals contain no DC component. This is advantageous for a direct conversion receiver architecture, that can have problems with low frequency noise and DC-offsets. The signal also has a constant envelope (amplitude), i.e. a unity peak to average ratio (PAR). The transmitter thus doesn't need any additional headroom when transmitting at a certain power level. It is also suitable for use with a non-linear (often more efficient) power amplifier.

**Figure 2.2:** Path taken in I/Q diagram during transmission of one symbol. The direction of rotation determines the encoded bit.

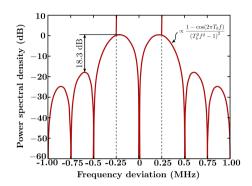

The resulting power spectrum of a binary FSK (BFSK) signal with data rate of 250kbit/s and matching deviation of  $\pm 250$  kHz is shown in figure 2.3. The notch in the centre is due to the absence of DC in the modulation.

**Figure 2.3:** Ideal spectrum of wideband BFSK modulation with  $250 \, \text{kHz}$  deviation.

This type of modulation is also easy to demodulate with a simple detector, a major advantage for a system like this, since simplicity usually translates to low power consumption. In this case the detection is performed by multiplying the complex input vector with a pair of matched filters. One filter uses the sequence "1, j, -1, -j" and the other "1, -j, -1, j", representing a clockwise and counter-clockwise rotation in the complex plane. By comparing the output magnitudes of the filters we can determine if the data is most probably a "1" or "0". Just as the modulation lacks DC, this detector will reject any DC content.

#### 2.2.3 LINK BUDGET

As previously mentioned we have assumed hearing aid to hearing aid communication as a representative example of low power communication. Since there is no line of sight between the two nodes and they are separated by a highly lossy medium, we can get an idea of the worst case conditions that we should handle for a body area network (BAN) application.

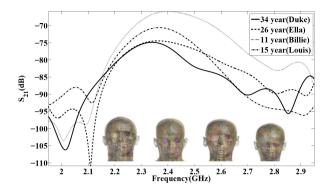

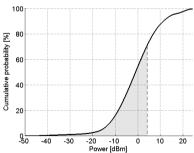

Figure 2.4: Ear-to-Ear Link Loss for different head phantoms

Simulations using four heterogeneous head phantoms based on real people [19], show that the worst case link loss in the  $2.4\,\text{GHz}$  band with in-the-ear antennas is  $-79\,\text{dB}$ , as seen in Fig.  $2.4\,[20]\,[10]$ .

The transmitter should also consume below 1 mW, and assuming it has an overall efficiency of 20%, it should be able to transmit  $0.2 \,\mathrm{mW}$  or  $-7 \,\mathrm{dBm}$ . Assuming a SAW-filter with 3 dB (worst case) loss this becomes −10 dBm. This indicates that the receiver needs a sensitivity of -10-79=-89dBm. Uncoded the data rate is 250kbps and we require a Eb/No of 12 dB for 0.001 bit error rate (BER). To meet the required sensitivity we need an overall receiver noise figure of  $-89 - 12 + 174 - 10 \cdot log_{10}(250k) = 19dB$ . With the SAW-filter loss and assuming the front-end and ADC contribute equally to the noise figure, we achieve this with a front-end noise figure of 13 dB. If we can achive a lower noise figure we will have a bit of margin. A front-end NF of 10 dB for instance gives a sensitivity of  $-92 \, dBm$ . There may still be situations when even more sensitivity is required to guarantee a viable connection, however, and with coding data rate can be sacrificed for sensitivity. With half the data rate the sensitivity can be increased by 5 dB. The filter is used to protect the receiver from interference, and to prevent the transmitter from emitting interference in other bands. Since linearity, and with it sensitivity to interference, is intimately connected to power consumption, it is one of the main trade-offs when designing a low power receiver. If, despite this, we can construct a receiver with sufficient robustness to not warrent a SAW-filter, the link budget is improved by 3 dB. If we can build such a receiver, it is probably not too hard to build a trasmitter that doesn't require an external filter either, improving the situation by another 3 dB. The transmitted power is low, and so it does not need very high spectral purity to meet regulations on spurious emissions.

#### 2.2.4 MAC PROTOCOL

Building a transceiver with very low power consumption is only part of the solution to providing radio connectivity with extremely low power consumption. For this we also need to make sure that the radio circuits are powered down as much as possible when there is no data to be transferred. In sensor networks and similar we expect the data to be rare and sporadic. This means that the receiver is effectively unused most of the time. The problem is that we do not know when another node has data to send, and thus the receiver needs to keep listening to its surroundings. The transceiver should thus be paired with an efficient protocol that can establish a link even while requiring the radio circuits to be turned on as little as possible. The main way of achieving this is to duty cycle the receiver, so that it wakes up at regular intervals to check for a signal. This moves some of the burden to the transmitter instead, as it has to provide a preamble/beacon alerting the receiver of the impending message, and this has to be long enough to ensure that the receiver will wake up at least once in this time period. Increasing the listening interval reduces the average receiver power consumption, but increases the time it takes until we can establish a connection with any certainty. Thus there is a trade-off between power consumption and latency. One of the more advanced MACprotocols built on this principle is XMAC [21] [22]. In this protocol short pauses are inserted in the preamble, where the receiver has an opportunity to send an acknowledgment (ACK) once it has detected the preamble.

An alternative method to reduce power consumption is to use a secondary receiver that is used only for the purposes of waking up the main receiver. This secondary receiver would be of a simple construction and have even lower power consumption. A wake-up signal could for instance be modulated with on-off-keying (OOK), which could be detected with an envelope detector, a diode rectifier in its simplest implementation. A wake-up receiver is not without its problems, however. Firstly the sensitivity is generally quite poor. The best to date having a  $-72\,\mathrm{dBm}$  sensitivity at a raw data rate of 100kbps and power consumption of  $52\,\mu\mathrm{W}$  while opearting at  $2\,\mathrm{GHz}$  [23]. Secondly this kind of circuit has poor frequency selectivity, making it sensitive to interference over a large bandwidth. Both of these could potentially be mitigated by transmitting long, known, coded wake-up messages. By correlating the received signal to the expected message, the chances of picking up the wake-up signal improves. Although we are trading data rate, the wake-up message should carry hardly any data, a recipient address at most.

The wake-up receiver holds on its own little advantage to the previously discussed receiver duty cycling, since there is a limit to how much less power the wake-up receiver can consume compared to the main receiver and still be functional. The wake-up receiver itself can, however, also be duty cycled [24].

#### 2.2.5 HANDLING OF INTERFERENCE

#### DYNAMIC RANGE

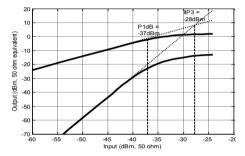

Assuming a front-end NF of 10 dB we have a sensitivity of -92 dBm. With an Eb/No of 12 dB, a data rate of 250kbps and RF bandwidth of 1 MHz, the effective signal to noise ratio (SNR) before the ADCs is about 6 dB. If the ADCs have a full scale (differential) input amplitude of 200 mV it reaches an SNDR of 6 dB at approximately 1.3 mV, assuming a dynamic range of 50 dB. With -92 dBm equating to  $7.94\,\mu\text{V}$  over  $50\,\Omega$ , at least 44 dB voltage gain is required before the ADCs while at maximum sensitivity. In practice it looks like the ADCs will achieve more than 50 dB dynamic range, and so the gain required will likely be lower than this.

At 44 dB front-end gain and 50 dB dynamic range the ADCs saturate at an RF input power of -92+(50-6)=-48 dBm in-channel. With a supply voltage of 0.8-0.9V the front-end baseband amplifiers can probably handle higher output signal amplitudes. Assuming they can handle a peak-to-peak amplitude 50% of a 0.8V supply, equating to a differential amplitude of 400 mV, the front-end saturates at an input power of -42 dBm in-channel. This equates to an IIP $_3$  of around -32 dBm assuming the well known 10 dB relation when compression is dominated by third order effects. Though there are ways of increasing this somewhat, including rail-to-rail amplifiers, it is ultimately constrained by our sensitivity specification and the dynamic range that can be achieved by an ADC in our power budget.

Outside the receive and neighboring channels the linearity is improved as the signal reaching the ADCs is attenuated by filtering in the front-end and anti-aliasing filters.

#### SECOND ORDER DISTORTION

The second order intermodulation distortion is a concern particularly for direct conversion receivers, as a single amplitude modulated signal anywhere in the band will cause low frequency  $\mathrm{IM}_2$  products at the mixer output. Operating in the 2.4 GHz band a common source of interference is from wireless local area networks (WLAN). The low bandwidth of our system compared to WLAN is beneficial in this case, as most distortion falls outside the receiver bandwidth. We have assumed a WiFi interferer with a power of  $P_{int}$  and a channel bandwidth of 20 MHz. The RF bandwidth is in this case 16 MHz. The resulting input referred  $\mathrm{IM}_2$  product can be estimated as (2.1) where  $IL_{band-select}$  is the worst-case insertion loss of the band-select (SAW) filter.

$$IM_2 = 2 \cdot (P_{int} - IL_{band-select}) - IIP_2 \tag{2.1}$$

This energy will be distributed as follows; DC (50%), twice the carrier frequency (25%), and baseband (25%) [25]. The energy at baseband will be distributed from DC to the RF bandwidth of the signal, which in this case is 16 MHz. Since the energy at DC is rejected by the matched filters and the baseband has a bandwidth of 0.5 MHz, compared to the interfering signal bandwidth of 16 MHz, we can estimate the total IM<sub>2</sub> energy entering the receiver as (2.2), where  $-6\,\mathrm{dB}$  corresponds to the 25% energy at baseband, and  $-15\,\mathrm{dB}$  to the bandwidth ratio. With a data rate of 250kbit/s (no coding) an Eb/No of 12 dB is required. With an intermodulation power density of  $P_{int-BB}-10\cdot log(500k)$  the largest WiFi interferer with 3 dB loss of sensitivity can be estimated as (2.3), where  $+3\,\mathrm{dB}$  is an increase in effective Eb, since the energy comes from both sidebands.

$$P_{int-BB} = 2 \cdot (P_{int} - IL_{band-select}) - IIP_2 - 6dB - 15dB \tag{2.2}$$

$$P_{int} = IL_{band-select} + \frac{P_{sens} + IIP_2 + 21 - Eb/No + 3 + 10 \cdot log(500k) - 10 \cdot log(250k)}{2}$$

(2.3)

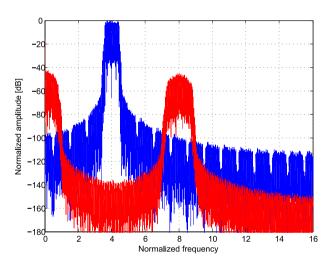

**Figure 2.5:** Simulated interfering WiFi signal and its IM<sub>2</sub>.

With a base sensitivity ( $P_{sens}$ ) of  $-92 \, dBm$  and an IIP<sub>2</sub> of  $0 \, dBm$  the maximum tolerable interferer is estimated to  $-35.5 \, dBm$ . However, it should be noted that the power spectral density of the intermodulation is not flat, and the intermodulation is strongest at low baseband frequencies. The above calculations are thus a bit optimistic. A more accurate estimate can be had from

a Matlab simulation. A 64QAM OFDM WiFi signal was generated and sent through a  $2^{nd}$  order nonlinearity, and the resulting spectrum can be seen in figure 2.5. The signal is in blue and the IM<sub>2</sub> in red. Note that since the carrier frequency is not important it is reduced for improved visibility. The result is that we can tolerate a  $-37.5\,\mathrm{dBm}$  interferer, a degradation of  $2\,\mathrm{dB}$  compared to the calculation.

#### **SELECTIVITY**

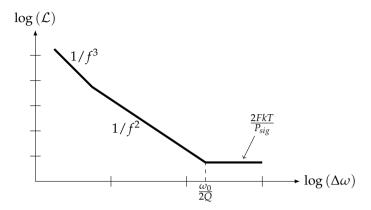

With sharp digital filters the selectivity performance in the adjacent channels is dominated by the phase noise superimposed on an interferer due to reciprocal mixing. The phase noise introduced through an interferer in an adjacent channel can be estimated by integrating the noise that spills over into the receiver channel. Assuming the phase noise power falls off at a  $1/(\Delta f)^2$  slope (see section 4.3.3) the integrated phase noise can be estimated as (2.4), from the phase noise at 1 MHz offset.  $BW_{rcv}$  is the receiver bandwidth, in our case 1 MHz, within which the phase noise is approximated as flat.

$$P_{PN,rcv} = P_{int} \cdot PN_{1MHz} \cdot \left(\frac{1M}{\Delta f}\right)^2 \cdot BW_{rcv}$$

(2.4)

This is a fair approximation in most cases. For the adjacent channel, however, the receiver bandwidth is large compared to the distance to the interferer, and so assuming the phase noise to be flat in the receive channel is inaccurate. To find out how much difference it makes, we can integrate the phase noise (assuming a  $1/(\Delta f)^2$  falloff), equation (2.5). We know the phase noise at 1 MHz which we can use to find  $N_0$  by equation 2.6.

$$P_{PN_{1/f^2},rcv} = \int_{f_1}^{f_2} N_0 \frac{1}{f^2} df = N_0 (\frac{1}{f_1} - \frac{1}{f_2})$$

(2.5)

$$N_0 \cdot \frac{1}{(1M)^2} = P_{int} \cdot PN_{1MHz}$$

(2.6)

$$\frac{P_{PN_{1/f^2},rcv}}{P_{PN,rcv}} = \frac{N_0(\frac{1}{f_1} - \frac{1}{f_2})}{N_0 \cdot \frac{1}{(1M)^2}(f_2 - f_1)} = \frac{(1M)^2}{f_1 \cdot f_2}$$

(2.7)

With  $f_1$ =0.5 MHz and  $f_2$ =1.5 MHz we find the flat noise approximation underestimates the integrated noise by 1.25 dB (2.7). For most estimates this is actually quite acceptable.

The oscillators built within this project have all had better than  $-106 \mathrm{dBc/Hz}$  phase noise at 1 MHz offset. The receiver requires an effective SNR of 6 dB and has a base sensitivity of  $-92 \mathrm{\,dBm}$ . From these numbers we estimate that for

16 Ultra Portable Devices

a sensitivity degradation of 3 dB the receiver can tolerate an adjacent channel interferer about 35.5 dB stronger than the desired signal, and 42.5 dB in the second adjacent channel. This assumes an unmodulated interferer in the center of the channel, and may therefore in practice be slightly worse.

At larger offsets the tolerance to interference is instead dominated by other effects such as saturation of the ADC and compression of the front-end. In the absence of a SAW-filter the phase noise may also affect the tolerance to out-of-band interference, as the LO generator phase noise is white at large frequency offsets.

# Low Power Radio

In the past a lot of research has gone into providing radio communication with increasing data rates, especially since the introduction of the smartphone. Lately, however, interest is increasing for providing connectivity with portable devices and sensors, that can be all around us. Such connectivity is sometimes referred to as the internet of things (IoT) [26]. Here, the challenge is, instead, to provide basic connectivity at very low power consumption. An example of the application of ultra-low power radio communication is wireless sensor networks (WSN). A wireless sensor network consists of small sensors combined with a radio transmitter/transceiver. They are used for monitoring, possibly over a wide area, usually reporting data back to a central controller. They could, for example, monitor temperature and air quality, or structural loading during construction work. Each node should be small and cheap, and should function extended periods of time on a battery charge. With low enough power consumption the energy used may be harvested from the surroundings, from sources such as heat, motion, radio interference, blood glucose, etc. Ideally the sensors should be cheap enough for one time use.

Similar to the WSN, a body area network (BAN) consists of devices worn on the body, or perhaps even implanted. A BAN may be used for health monitoring, perhaps detecting medical conditions early, or to help diagnose a condition that requires long term monitoring. Currently an early form of BAN exists in the form of sports sensors that connect to your phone or sports watch, and are used to monitor things like heart rate and activity. Some of these devices can also connect to stationary sports equipment such as a treadmill. Low power wireless devices may also, for example, be used in smart houses to, apart from monitoring purposes, control lights and other equipment. The full potential of low power radio will materialize as the technology matures.

18 Low Power Radio

### 3.1 NETWORK CONFIGURATIONS

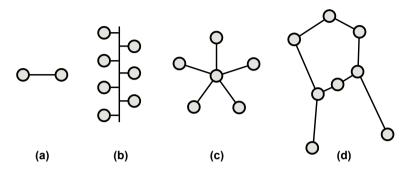

**Figure 3.1:** Network topologies (a) Point to point (b) Bus (c) Star (d) Mesh

A wireless network may be organized in a number of different ways. Figure 3.1 shows some of the basic network topologies. The simplest configuration is point-to-point (P2P) which is just a link set up between two devices.

In a bus topology all nodes have equal access to the rest of the network on the same frequency with no particular priority. Steps must be taken to avoid collisions when two nodes have data to communicate simultaneously, such as carrier sensing, where a node will only attempt to transmit if it detects that the channel is free.

In a star network, all devices are connected to a central node (hub), which handles all traffic on the network. Any data passed from one peripheral node to another has to be repeated by the hub. This configuration makes sense in a network combining low power sensor nodes with a single higher powered device. An example is peripheral devices such as a wireless headset or sports monitors connected to a mobile phone. The phone has a large battery compared to the connected devices and it is possible to let it provide the main part of the energy required to communicate. The hub, for instance, can keep the network synchronized by transmitting a beacon at regular intervals. It may also contain a more sensitive radio, allowing the other devices to transmit with less power.

Another network topology is the mesh. In a mesh messages may be relayed through several nodes, and there may be more than one path available. With the nodes collaborating, the network may cover larger distances and improve connectivity with nodes otherwise obscured by large objects.

# 3.2 LOW POWER RADIO STANDARDS

# 3.2.1 BLUETOOTH

Created by Ericsson in the late nineties, and now maintained by the Bluetooth special interest group (SIG), Bluetooth (BT) is a wireless standard intended for providing a short range connection to devices such as computers, phones, headsets, etc. Operating in the 2.4 GHz ISM band it is designed to be simple and cost effective. The original BT standard has a data rate of 1 MBit/s in a 1 MHz channel, using Gaussian frequency shift keying (GFSK) modulation. To reduce susceptibility to interference, BT employs frequency hopping, and will also actively avoid crowded channels [27].

Later revisions of the BT standard have added optional support for increased data rates by enabling more advanced modulation schemes, or by transferring large data payloads via a 802.11 (WiFi) link. Enhanced data rate (EDR) and high speed (HS) options increase the maximum data rate to 3 and 24 MBit/s, respectively.

With the recent introduction of BT v4.0 [28] support for a new low power communication protocol has been added, called Bluetooth Low Energy (BLE). It is not directly compatible with classic bluetooth, and a BT v4.0 device may implement either classic BT, BT low energy, or both. Support for BLE is also referred to as Bluetooth SMART, indicating a BLE only device, or Bluetooth SMART ready for a device implementing both protocols. Recently a number of smartphones have been released that are Bluetooth SMART ready.

Bluetooth low energy has a data rate of 1 Mbit/s with an average throughput of 270 kbit/s. It uses frequency hopping and GFSK modulation, similar to classic BT, but at a higher modulation index (0.5 instead of 0.35), which is easier to demodulate, but results in a larger signal bandwidth. It is configured in a star-bus hybrid network topology.

## 3.2.2 ZIGBEE

Zigbee is a standard from 2003, based on the 802.15.4 standard. It can operate in the 868 MHz (Europe), 915 MHz (North America) and 2.4 GHz ISM bands, and it supports a mesh network topology with up to 65536 nodes. The data rate varies from 20kbit/s in the 868 MHz band to 250 kbit/s in the 2.4 GHz band. Binary phase shift keying (BPSK) is used for lower data rates, and offset quadrature phase shift keying (OQPSK) for the highest data rate. To improve resistance to interference the signal is spread over a 5 MHz wide channel using direct sequence spread spectrum (DSSS) [29].

20 Low Power Radio

# 3.2.3 ANT

Launched in 2003, ANT is a proprietary protocol for communication with ultra low power devices, and optimized for communication with small payloads. The 2.4 GHz ISM band is used, divided into 1 MHz channels. It can be configured into a wide range of network topologies, including P2P, Star, Bus, Mesh, Broadcast, and hybrid solutions [30]. While communicating one node is designated as the master. The master node will transmit short eight bit payloads at regular intervals, which the slave nodes use to synchronize to the master. A slave may also transmit data to the master. One frequency channel may be divided up into several time-interleaved channels, and devices on different networks will adjust their timing to avoid collisions. The data rate is 1 Mbit/s with GFSK and the average throughput is 20 kbit/s.

This chapter briefly describes the function of a receiver front-end as well as the components that it is constructed from, including some of the considerations required in the design of a low power receiver front-end. A short summary of the circuits described in the included papers is also given, together with a table comparing their performance.

### 4.1 ARCHITECTURE

#### 4.1.1 HETRODYNE

The traditional way of building a receiver front-end is with the superhetrodyne structure, Fig. 4.1, invented by E. H. Armstrong in 1918. After coarse filtering, the RF signal is amplified by a first amplifier to strengthen the signal before further processing. At the heart of the hetrodyne receiver is a mixer, basically a multiplier, which is used to bring the signal down to a much lower intermediate frequency ( $f_{IF}$ ). To do so the RF signal is multiplied with a reference signal from the local oscillator (LO), placed such that its frequancy  $f_{LO} = f_{RF} \pm f_{IF}$ . Products of the multiplication will appear at various frequencies, among them the difference frequency  $f_{IF}$ . Two different input frequencies,  $f_{RF} = f_{LO} \pm f_{IF}$ , will yield the same output frequency. Since we are only interested in receiving one frequency at the time, anything at the other frequency (the image frequency) is attenuated by image rejection filtering prior to mixing. The bandwidth of a filter is generally proportional to the center frequency, and the sharp filtering for selectivity is thus performed at the IF frequency where it is much easier to build a narrow filter, allowing us to separate out just one channel.

Figure 4.1: Superhetrodyne receiver

The super heterodyne architecture is effective and it has been used widely for a long time. The extensive filtering required is, however, a drawback when implementing it on-chip. On-chip components have considerable component variation and, especially inductors, generally have low quality (Q) values, rarely exceeding 20. This limits the filtering properties of the RF filters, and especially the image reject filter will be too poor, as the frequencies of the wanted signal and the image are very close to each other at RF. The IF filter is also an issue since the inductors required to build a passive filter at low frequency will be so large that they may not even fit on the chip. Though there are other ways of implementing an IF filter more suitable on chip, including active filters, it is not an ideal situation.

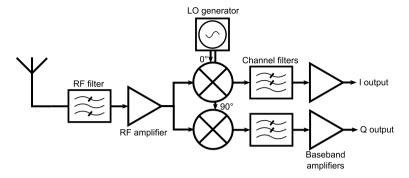

### 4.1.2 HOMODYNE/DIRECT CONVERSION

The direct conversion architecture is an attractive solution. The concept is fundamentally very similar to the heterodyne receiver, with the main difference that the IF frequency is zero (it is also referred to as a "zero IF" receiver). This is attractive for a couple of reasons. Firstly the image frequency does not pose any problem, since it coincides with the frequency of the wanted signal. This also means that twice as much of the wanted signal power enters the mixer, improving the SNR by 3 dB, effectively reducing the mixer noise figure. Secondly, the output signal is now at baseband. This means that the circuits after the mixer are operating at the lowest possible frequency, and can be implemented in a power efficient manner. Also the channel (IF) filter is now of a low-pass characteristic, and much easier to implement on-chip. The direct conversion receiver does require some additional circuitry to function properly, however. Since both the upper and lower sidebands of the RF signal are converted to the same output frequencies, we need additional measures to keep the information apart. This is achieved with a quadrature mixer, which is basically two separate mixers operated with LO signals 90° apart. This effectively treats the RF signal as two separate amplitude modulated carriers, sine and cosine, which according to Fourier theory are orthogonal to each other.

4.2. LO Generation 23

Figure 4.2: Direct conversion receiver

There are, however, some issues that have prevented the direct conversion architecture from being widely used until the last decade. Noise tends to increase at very low frequencies. As current passes through an electric component, such as a transistor, it will emit a type of noise dubbed "flicker noise". A property of this noise is that most of its energy is concentrated to low frequencies. In fact its spectral content is inversely proportional to the frequency as 1/f, and it is often known as 1/f noise. Since the receiver output signals appear at baseband, they are sensitive to low frequency noise, and the flicker noise must thus be kept to a minimum to not impair the receiver sensitivity. There are also other issues. The LO frequency is the same as that of the RF signal, and if the mixers are not perfectly symmetrical energy from the LO will leak into the signal path. Apart from leading to unwanted emission through the antenna, some of the power may be reflected back into the mixers, and will produce a DC offset at the outputs. Though these problems can be reduced by different means they will always be present. As mentioned in section 2.2.2 we have proposed a modulation scheme which contains no information close to DC. Additionally, the direct conversion architecture is sensitive to second order intermodulation distortion. Second order distortion will cause intermodulation products from an amplitude modulated interfering signal to appear at baseband (and at twice the signal frequency), potentially desensitizing the receiver. The low frequency IM<sub>2</sub> products from a signal with constant amplitude will appear at DC.

#### 4.2 LO GENERATION

## 4.2.1 QUADRATURE GENERATOR

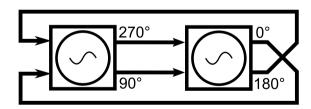

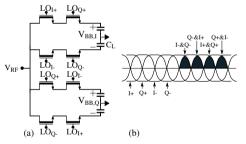

Operating a direct conversion receiver requires quadrature LO signals. Typically two differential signals are required, resulting in four signals spaced 90°

apart ( $0^{\circ}$  90° 180° 270°). There are different ways of generating such signals, including quadrature coupled oscillators or a single voltage controlled oscillator (VCO) together with a frequency divider or a polyphase filter [31]. Since the polyphase filter attenuates the signal, especially if implemented with multiple stages, it is less suitable for low power implementations where we have to conserve as much power as possible. This section briefly introduces the first two options.

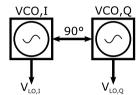

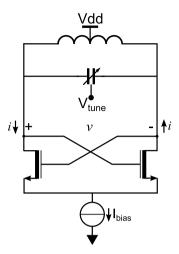

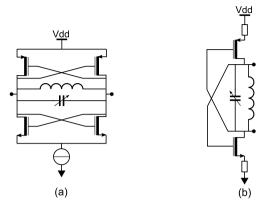

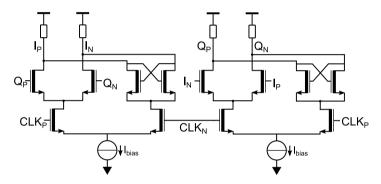

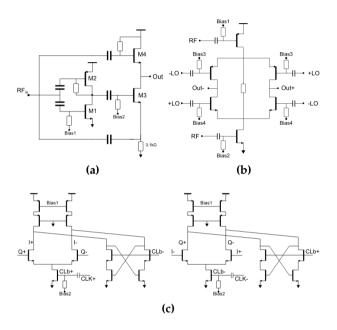

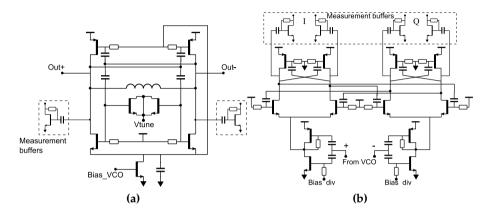

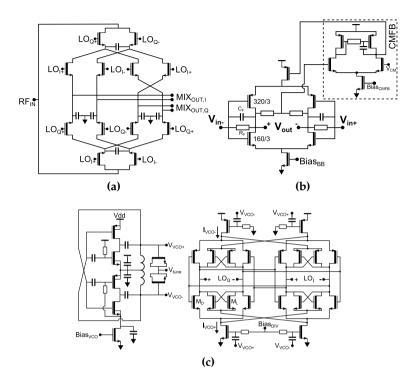

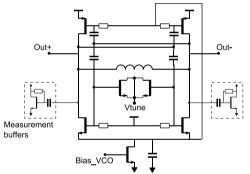

Figure 4.3: Quadrature coupled VCO

The quadrature VCO (QVCO, Fig. 4.3) consists of two VCO cores that are coupled together in a way that forces them to oscillate with a phase difference of 90°. With all high frequency nodes in resonance, the QVCO can potentially operate with lower power consumption than the frequency divider approach. The QVCO is, however, sensitive to interference injected from the RF signal path. To address this LO buffers should be used to isolate it, and these may offset the power saved by the use of a QVCO. A second issue with the QVCO is that since both cores require an inductor each, it occupies a fairly large area on chip.

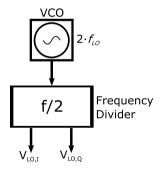

Figure 4.4: VCO and frequency divider

The main alternative to a QVCO is the combination of a VCO operating at a harmonic frequency of the LO, and a frequency divider (Fig. 4.4). Since the VCO is operating at a higher frequency each oscillation period takes less time, resulting in sufficient time resolution to define signals with multiple phase

4.2. LO Generation 25

positions at a lower frequency. A differential VCO produces two signals 180° apart. Generating enough phases for a quadrature front-end the number of phases thus needs to be doubled, from two to four, which can be achieved by halving the frequency.

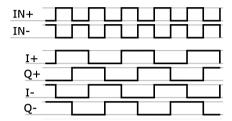

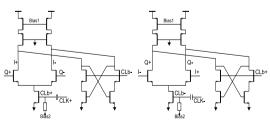

**Figure 4.5:** Frequency divider f/2 operation

To illustrate how a frequency divider can be used to produce quadrature signals, consider figure 4.5. At the top of the figure are the input signals, in this case assumed to be square waves for purposes of clarity. Below are the four phases produced by a digital f/2 frequency divider. The digital dividers will act on the flanks of the input signals, so that each flank in the outputs corresponds to a flank in the input signal.

A high frequency digital divider requires large power consumption to handle the fast transitions required. It does, however, help isolate the VCO from the mixers, and if it has enough drive strength it avoids the need for separate LO buffers. The divider can potentially achieve better quadrature accuracy than the QVCO thanks to its sharp transitions that are well defined in time. Furthermore, this approach requires only one VCO inductor and this can be made smaller as the oscillator operates at higher frequencies, meaning it is likely to require considerably less chip area.

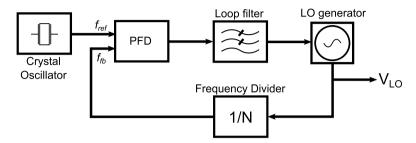

## 4.2.2 PLL

An LO generator based on just an LC VCO cannot achieve the frequency accuracy and signal purity required by the receiver. A VCO tuned by a varactor is sensitive to variations in component values from manufacturing tolerances as well as changes induced by varying operating temperature. Free running, the frequency is not accurate and stable enough for use in a narrow-band receiver. With practical Q factors below 20, the VCO also has enough integrated noise for the jitter to interfere with demodulation. Compare this with a crystal resonator which typically has a Q above 10000. A crystal, however, resonates at low frequencies, typically below 30 MHz, and is effectively not tunable. The phase locked loop (PLL) [32] allows the RF VCO to be locked to a frequency multiple of a crystal oscillator (XO). This allows an LO signal

to be produced with a frequency accuracy approaching that of the XO, but which can be tuned in frequency by changing the multiplication factor.

Figure 4.6: PLL

Figure 4.6 shows the basic structure of a PLL. A frequency divider produces a feedback signal at frequency  $f_{fb} = f_{LO}/N$ . It can be implemented as a counter that produces one pulse for every N input pulses. A phase frequency detector (PFD) compares this signal with the reference generated by the XO, and a signal proportional to the time difference is passed to the LO generator through a loop filter that suppresses ripple at the reference frequency, and that shapes the frequency response of the PLL. When  $f_{fb}$  and  $f_{ref}$  are close enough the difference in phase corresponds to (4.1).

$$(\theta_{fb} - \theta_{ref}) = \int (f_{fb} - f_{ref}) \tag{4.1}$$

The PLL strives to minimize the phase difference  $\theta_{fb} - \theta_{ref}$  through continuous adjustments to the VCO frequency, until eventually  $f_{fb}$  and  $f_{ref}$  are equal, and the output is locked to  $f_{LO} = f_{fb} \cdot N = f_{ref} \cdot N$ . By letting the divider ratio change slightly each reference period it is possible to achieve an effective non-integer division ratio, allowing finer frequency steps.

### 4.3 BUILDING BLOCKS AND COMPONENTS

## 4.3.1 LNA

## **COMMON SOURCE**

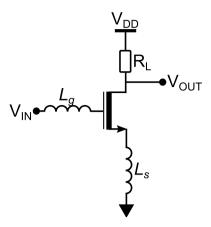

The inductively degenerated Common Source (CS) LNA, shown in figure 4.7, is a popular LNA topology as it is capable of achieving high noise performance. The input impedance is given by (4.2), assuming ideal inductors. Inductor  $L_s$  and the gate-source capacitance  $C_{gs}$  form a feedback path from the transistor drain current to the input current, which results in a resistive part of the input impedance equal to  $L_s \frac{g_m}{C_{gs}} = L_s \omega_T$ .

Figure 4.7: Common source topology with inductive degeneration

$$Z_{in} = L_s \frac{g_m}{C_{gs}} + \frac{1}{j\omega C_{gs}} + j\omega (L_s + L_g)$$

(4.2)

$L_s$  is chosen to provide a desired input resistance, typically  $50\Omega$ . For a fast transistor  $\frac{g_m}{C_{gs}}$  will be high, and  $L_s$  may thus be very small, perhaps below 1 nH, making it difficult to implement, especially in a single ended design, where it will be sensitive to any inductance in the ground path.  $L_g$  is chosen such that it resonates with  $C_{gs}$  and  $L_s$  (4.3), making the input impedance completely resistive at the operating frequency. With practical device sizes,  $C_{gs}$  is fairly small, leading to a large value of  $L_g$ , requiring large area to implement.

$$\omega_0(L_g + L_s) = \frac{1}{\omega_0 C_{gs}} \tag{4.3}$$

These problems may be mitigated by placing a capacitor in parallel with  $C_{gs}$ . This increases the effective value of  $C_{gs}$ , without the increased Q of the input circuit increasing the gate induced noise [33].

#### COMMON GATE

The common gate (CG) LNA (Fig 4.8) provides a resistive input while being both simple and inductorless. The input impedance  $Z_{in}$  is equal to  $1/(g_m + g_{mb})$ , neglecting source terminal capacitance and drain-source conductance. If the device, and hence  $C_{gs}$ , is small, the input impedance may be predominantly resistive over a very wide frequency range, making the CG topology particularly well suited for ultra-wideband (UWB) applications.

Figure 4.8: Common gate topology

Since the input impedance is almost entirely dependent on  $g_m$ , and it should be matched to the RF source ( $Z_{in}=R_S$ ), we have very little freedom in the design parameters. One way this manifests itself is the noise performance that is limited to (4.4), where  $\gamma$  is ideally 2/3 for a long channel device (and significantly larger for short channel devices), and  $\alpha$  is equal to  $g_m/g_{ds0}$ . For long channel devices  $\alpha$  is ideally one, while it is smaller for short channel devices. If, for example, a short channel device has  $\frac{\gamma}{\alpha}=2$  this means that the lowest noise figure we can achieve with that device is 4.8 dB.

$$F_{min,CG} = 1 + \frac{\gamma}{\alpha} \cdot \frac{1}{g_m R_s} = 1 + \frac{\gamma}{\alpha}$$

(4.4)

More important when designing for low power consumption is that the current consumption is set by the need to provide a certain input impedance. Although  $g_m/I_d$  can be improved somewhat by biasing the transistor in weak inversion (at the expense of bandwidth), it is not enough for truly low power designs.

A differential CG LNA design may improve the noise performance through capacitive cross-coupling, where the gates are driven by the opposite polarity input. This halves the required  $g_m$ , and reduces the minimum noise factor (4.5) [34].

$$F_{min,cross-coupled\ CG} = 1 + \frac{\gamma}{\alpha \cdot 2}$$

(4.5)

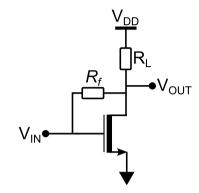

## SHUNT FEEDBACK

Just like the CG and CS amplifiers, the shunt feedback LNA (Fig. 4.9) provides a resistive input impedance through a feedback path, with an input

impedance given by (4.6). Compared to the CG topology,  $g_m$  may be larger than  $1/R_S$ , and thus it can achieve better noise performance.

Figure 4.9: Shunt feedback topology

$$Z_{in} \approx \frac{R_f + R_L}{1 + g_m R_L} \tag{4.6}$$

All the input current still has to be provided by the transistor, and so  $g_m$  still has a lower limit of  $1/R_S$  (which we get when  $R_L \gg R_f$ ). This approach is thus unlikely to be any better for ultra-low power designs than the CG stage.

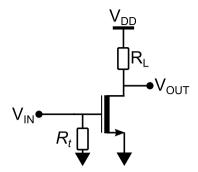

#### RESISTIVE TERMINATION

By far the simplest method of matching is to simply terminate the input with a resistor to ground (Fig. 4.10). Independent of the amplifier it is quite attractive at first glance. The problem with this solution is that we are attenuating the RF signal. In other words we are just dumping RF power without making proper use of it, and so it is hard to achieve an acceptable noise figure with this topology [35].

Figure 4.10: Resistive termination

$$F_{RT} \approx 2 + \frac{4\gamma}{\alpha g_m R_S} \tag{4.7}$$

Ignoring the noise of  $R_L$  the noise factor is given by (4.7). We can see that  $NF_{min} > 3$  dB. This may not seem so bad, but to get close to this  $g_m$  must be much larger than  $1/R_S$ , which results in a very large power consumption. If, for the sake of comparison, we assume the same power consumption as in the CG topology ( $g_m = 1/R_S$ ) and the same  $\gamma/\alpha = 2$  we get a noise figure of 10 dB, compared to 4.8 dB for the CG. Lowering the power consumption further, the noise figure will quickly become unacceptable.

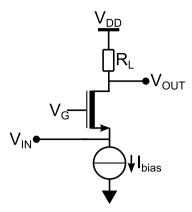

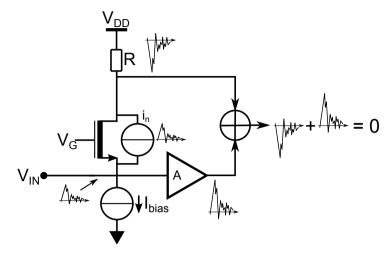

### NOISE CANCELLATION

Noise cancellation is a method where the noise contribution from the channel of one device can be suppressed at the output [36]. An example of this is shown in figure 4.11. The noise  $i_n$  from the transistor channel is injected into the signal path at two different points with opposite polarity. The wanted signal has the same polarity in these two points, and if the gain to the output from both points is matched, for instance with a second gain stage, the noise will be canceled while the wanted signal is amplified. This is precisely the operation of [37].

Figure 4.11: Example of noise cancellation

With the noise from one device being canceled other sources will dominate, for instance the amplifier used to match the gain of both signal paths. Noise canceling can be particularly useful when employed to combine the properties of different amplifier stages. For instance, a common gate and a common source stage may be combined in one LNA. Together they act as a balun, while the total noise figure is close to that of the common source stage, which can reach lower noise figures than the common gate [38].

#### LC-RESONATOR

Most RF circuits are designed for use in a  $50\Omega$  (or in some cases  $75\Omega$ ) environment, but that does not mean that it is an absolute requirement. A transceiver could operate with other impedances, as long as the antenna, interconnects, and filters are designed with this in mind. The impedance (or characteristic impedance) indicates the ratio of voltage to current. Moving to a higher impedance thus results in a larger voltage swing for a given power. As shown in (4.8) a move from an impedance of  $50\Omega$  to  $Z_Z$  gives a voltage increase  $V_Z/V_{50\Omega}$  equal to the square root of the relative change in impedance. By increasing the operating impedance we can lower the circuit power consumption (while trading linearity), since the circuits can operate with lower  $g_m$ .

$$P_Z = P_{50\Omega} \implies \frac{V_Z^2}{Z_Z} = \frac{V_{50\Omega}^2}{Z_{50\Omega}} \implies \frac{V_Z}{V_{50\Omega}} = \sqrt{\frac{Z_Z}{Z_{50\Omega}}}$$

(4.8)

Increasing the operating impedance is, however, not without drawbacks. Firstly, all components in the RF path need to be fully customized. The an-

tenna should most likely be a custom design in any case, but it is hard to acquire SAW-filters for non-standard impedances. There is, however, a chance that a standard filter component may still function well enough, although its frequency response will be affected. Secondly, there are limits to the characteristic impedance that can be practically achieved with a PCB transmission line. An extremely narrow 0.1 mm non-grounded coplanar waveguide even on a thin substrate with low  $\epsilon_r$  is unlikely to exceed a characteristic impedance of  $200\Omega$  by far.

The problems of non-standard components and difficulty of verifying a non  $50\Omega$  device makes an on-chip impedance transformation attractive. The chip can then be used in a standard  $50\Omega$  environment, while the LNA can have a higher input impedance resulting in less power consumption. An LC filter (Fig. 4.12) may provide the impedance transformation with a single on-chip inductor. Ignoring the parasitic capacitance of the pad and ESD-diodes as well as the finite Q of the reactive components, the basic design equations are given in (4.9)-(4.11). The mentioned non-idealities will degrade the performance by introducing losses and by reducing the effective transformation ratio.

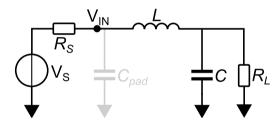

Figure 4.12: LC matching network

$$Q = \sqrt{\frac{R_L}{R_S} - 1} \tag{4.9}$$

$$\frac{1}{\omega_0 C} = R_L / Q \tag{4.10}$$

$$\omega_0 L = R_S \cdot Q \tag{4.11}$$

Ideally the components should have high Q, but that means the inductor will require large chip area. It is, however possible to make quite a compact inductor if a low Q can be tolerated. Returning to the matching technique with resistive termination, a possibility is to let the parasitic resistance of the inductor form the termination resistance.

### 4.3.2 MIXER

The mixer acts to convert a signal from one frequency to another. In a receiver front-end it converts the RF signal to a much lower frequency where it can be more easily amplified and processed. The mixing is essentially a multiplication of the signal with a tone at some other frequency. Although this can be performed with pretty much any non-linear device, due to its high performance the most used method is to use transistors as switches, rapidly switching the polarity of the signal as it passes from input to output.

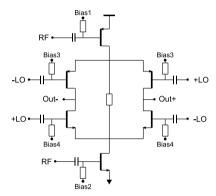

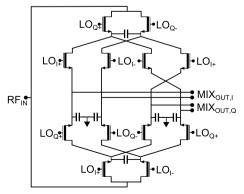

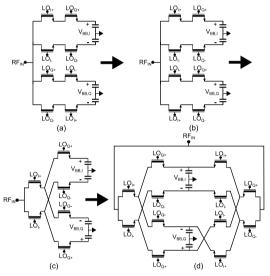

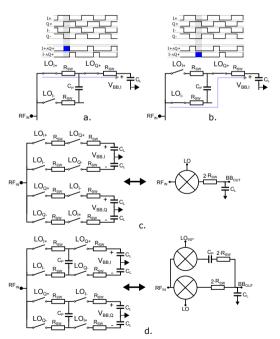

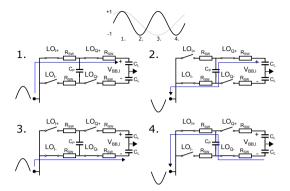

A mixer may be implemented with just a single device, but suffers from a lack of isolation between the RF and LO signals. The single balanced mixer provides this isolation, and with a differential output, it is much better suited to conveying IF signals close to DC. There is still some leakage from the LO to IF ports, but in a direct conversion receiver the frequency difference is high enough that it can be easily attenuated with a filter. Placing two single balanced mixers side by side, operating with opposite phase RF and LO signals and combining the outputs, we get a double balanced mixer, where all ports are differential, and where also RF to IF leakage is attenuated. Triple balanced mixers do exist, but are rarely necessary. In low power design a single ended RF port is generally preferred since it usually requires less power for the same noise performance, and we avoid some extra circuit complexity, especially since most antennas do not provide balanced signals. In this section single balanced active and passive mixers are briefly treated.

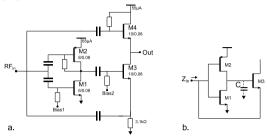

### **ACTIVE MIXER**

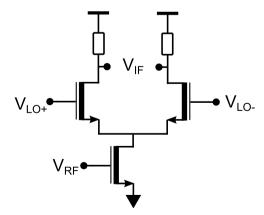

Figure 4.13: Single balanced active mixer

Being powered, the active mixer (Fig. 4.13) can provide power gain. The input device also provides additional isolation from LO to RF ports. The main drawback of the active mixer, apart from the power consumption, is the noise generated, particularly low frequency 1/f noise. 1/f noise is especially harmful to direct conversion receivers since the output signals are at baseband. The mixer noise is mainly injected during the switch period, where both devices are conducting at the same time [39], [40]. At other times the switch devices are saturated, acting as cascodes, and so their noise will have little effect on the current passing through.

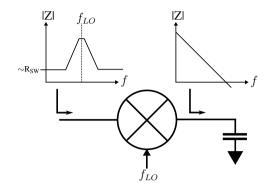

### **PASSIVE MIXER**

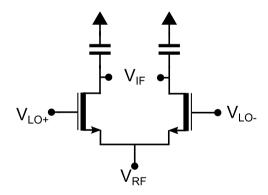

The passive mixer, like its name suggests, does not consume any power, and at the RF node the DC current is zero. The main advantage of passive mixers is the lack of 1/f noise, making them particularly suited for direct conversion receivers. The passive mixer in Fig. 4.14 is operating in voltage mode. They can also operate in current mode, but this requires low impedances, and thus large devices, and it is thus less suitable for low power applications and more for situations when very high linearity is required. One way of viewing a voltage mode passive mixer driven by square waves is as a sample and hold operation performed directly on the RF signal, and they are sometimes referred to as sampling mixers.

Figure 4.14: Single balanced passive mixer

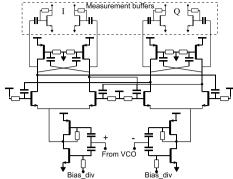

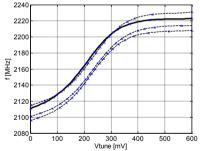

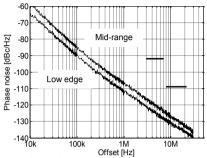

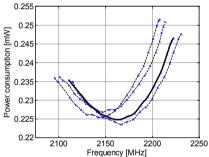

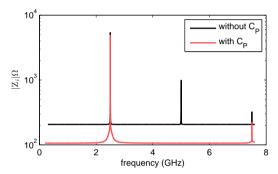

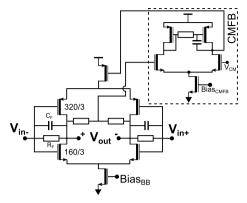

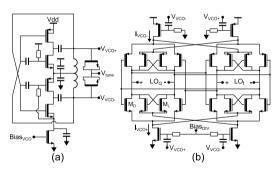

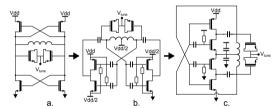

The gain and linearity of especially a passive mixer are dependent on the LO waveforms. A transistor requires a certain voltage between gate and source to conduct well. As the amplitude of the RF or IF signal gets large enough, the voltage may force the transistors to turn off when they should not. In a similar way it could also cause the transistors to turn on when they should be off. The larger the LO amplitude, the larger the other signals