# A 65-nm CMOS ultra-low-power LC quadrature VCO

Lee, Kin Keung; Bryant, Carl; Törmänen, Markus; Sjöland, Henrik

Published in:

Proc. IEEE NORCHIP

2009

# Link to publication

Citation for published version (APA): Lee, K. K., Bryant, C., Törmänen, M., & Sjöland, H. (2009). A 65-nm CMOS ultra-low-power LC quadrature VCO. In Proc. IEEE NORCHIP (pp. 1-4)

Total number of authors:

General rights

Unless other specific re-use rights are stated the following general rights apply:

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

• You may not further distribute the material or use it for any profit-making activity or commercial gain

- You may freely distribute the URL identifying the publication in the public portal

Read more about Creative commons licenses: https://creativecommons.org/licenses/

Take down policy

If you believe that this document breaches copyright please contact us providing details, and we will remove access to the work immediately and investigate your claim.

Download date: 18. Dec. 2025

# A 65-nm CMOS Ultra-Low-Power LC Quadrature VCO

Kin Keung Lee, Carl Bryant, Markus Törmänen, Henrik Sjöland

Department of Electrical and Information Technology, Lund University, Box 118, 221 00 Lund, Sweden

Abstract — An ultra-low-power LC quadrature VCO (QVCO) is presented. It is designed in a single-poly seven-metal 65nm CMOS process. To minimize power dissipation an inductor with a high LQ product of 188nH at 2.4GHz, and a self-resonant frequency ( $f_o$ ) of 3.8GHz, was designed. According to SpectreRF simulations the power dissipation is below 250 $\mu$ W at a 0.6V supply. At this supply the simulated tuning range and phase noise at 1MHz offset are 10.4% (2.34–2.59GHz) and -113.4dBc/Hz respectively. The phase noise figure of merit (FoM) is better than 187dB at all supply voltages of interest, which is competitive to other state-of-the-art QVCOs.

#### I. INTRODUCTION

The ubiquity of wireless links in everyday life increases rapidly, medical implants and wireless sensor networks are two good examples. For such applications, not only production costs are important, but also maintenance costs and user satisfaction. Replacing the battery frequently is therefore unrealistic, so the power consumption of the whole system must be extremely small in order to maximize the battery life.

Zero-IF and low-IF receivers are widely used in modern radio systems because of their small size and low power dissipation compared to classical super-heterodyne receivers. In such receivers, quadrature down-conversion is required to reject the image signals. This requires quadrature local oscillator signals, which can be generated directly using ring oscillators. Unfortunately ring oscillators have poor phase noise performance compared to the LC oscillator counterparts.

To address these requirements, this paper presents the design of an ultra-low-power quadrature LC VCO in a 65nm CMOS process. To achieve low power consumption in an LC oscillator, the inductor LQ product should be maximized. An inductor with an LQ product of 188nH at 2.4GHz was

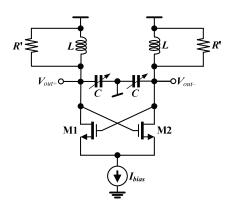

Fig. 1. Negative-resistance VCO

therefore designed. According to Spectre RF simulations this leads to a very low power consumption of the complete QVCO of less than  $250\mu W$  at 0.6V supply. At such low supply voltages, the large-signal capacitance range of varactors usually becomes reduced and, thus, also the frequency tuning

range. In this paper, the use of nMOS inversion-mode varactors, however, provide more than 10% tuning range in all cases of interest. Meanwhile, the FoMs are above 187dB, which is competitive to other state-of-the-art QVCOs.

## II. LOW-POWER LC VCO DESIGN

A typical negative-resistance LC VCO is depicted in *Fig. 1*, with a cross-coupled pair connected in parallel to the LC tank to compensate the loss. *R'* is the equivalent resistance contributed by the inductor.

In order to start oscillation, the start-up gain of the oscillator must be larger than unity, which gives:

$$A_{start-up} = g_m \cdot R' = \frac{I_{bias}}{V_{OV}} \cdot R' \ge 1 \tag{1}$$

Usually,  $A_{start-up}$  is set to at least 2-3 to have some margin.

In order to drive connected circuits, there are always some requirements of the output voltage swing of the oscillator. Assume M1 and M2 are ideal switches, the differential output current can be regarded as the result of multiplying the drain current of M1 by a unit-amplitude square wave.

Since the amplitude of the fundamental component of a square wave is  $4/\pi$  times the amplitude of the square wave:

$$I_O = \frac{4}{\pi} \cdot I_{bias} \tag{2}$$

Hence the differential peak output voltage is:

$$V_{O-diff,peak} = I_O \cdot R' = \frac{4}{\pi} \cdot I_{bias} \cdot R'$$

(3)

Eq. (1) and (3) are very important to power consumption of oscillators, and they show that the bias current is inversely proportional to R', where:

$$R' = \omega_o \cdot LQ \tag{4}$$

The result is that in order to minimize the power consumption the LQ product of the inductor must be maximized.

#### III. INTEGRATED INDUCTOR

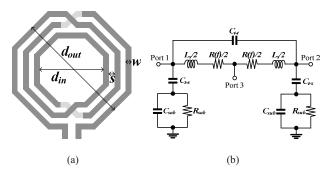

The single- $\pi$  lumped model was adopted in this paper because of its simplicity. Refer to  $Fig.\ 1$ , instead of using two separate spiral inductors, the use of a single center-tapped inductor gives the benefit of higher inductance at a given area. A center-tapped octagonal inductor and its single- $\pi$  model are shown in  $Fig.\ 2$ . Its parameters are discussed in this section.

The expression for spiral inductance calculation in [1] is adopted in this thesis:

$$L_{s} = \frac{\mu_{o} n^{2} d_{avg} c_{1}}{2} \left[ \ln(\frac{c_{2}}{\rho_{fill}}) + c_{3} \rho_{fill} + c_{4} \rho_{fill}^{2} \right]$$

(5)

where  $\mu_o$  is the permeability of free space, n is the number of turns,  $c_i$  are layout dependent coefficients,  $\rho_{fill}$  and  $d_{avg}$  are the fill ratio and average diameter, respectively, given by:

978-1-4244-4311-6/09/\$25.00 ©2009 IEEE

Fig. 2. (a) Center-tapped octagonal inductor and (b) its single- $\pi$  lumped model.

$$\rho_{fill} = \frac{d_{out} - d_{in}}{d_{out} + d_{in}}$$

(6)

$$d_{avg} = \frac{d_{out} - d_{in}}{2}$$

(7)

The capacitance expressions in [2] were adopted but not mentioned explicitly here.

#### Skin Effect

For a single metal line, at high frequency the skin depth can be comparable to or even smaller than the cross-sectional dimensions of the line and the AC current is pushed towards the surface of the conductor. This is described as skin effect and the skin depth is given by:

$$\delta = \sqrt{\frac{2}{\omega\mu\sigma}} \tag{8}$$

where  $\mu$  and  $\sigma$  are the permeability and conductivity of the conductor respectively.

When w or the thickness t of the conductor is larger than  $\delta$ , AC resistance including skin effect equals [3]:

$$R_{skin}(f) = R_{DC} \left[ 1 + \left( \frac{f}{f_1} \right)^2 + \left( \frac{f}{f_n} \right)^5 \right]^{\frac{1}{10}}$$

(9)

where  $f_I$  and  $f_u$  indicate at what frequency the skin effect starts to be significant and are given by:

$$f_1 = \frac{\pi}{2\mu w t \sigma} \qquad (10) \qquad f_u = \frac{\pi^2}{2\mu t^2 \sigma} \left[ K(\sqrt{1 - \left(\frac{t}{w}\right)^2}) \right] \qquad (11)$$

and K(m) is the elliptic function of the first kind.

#### **Proximity Effect**

For multi-turn inductors, the magnetic field generated by neighboring lines affects the current distribution and causes a

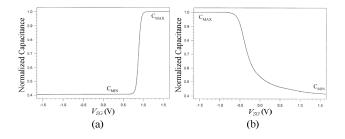

Fig. 3. C-V characteristics of (a) inversion-mode and (b) accumulation-mode varactor.

| Inputs     | Values |  |  |  |

|------------|--------|--|--|--|

| # of turns | 9      |  |  |  |

| w          | 4.5µm  |  |  |  |

| S          | 3µm    |  |  |  |

| $d_{out}$  | 200μm  |  |  |  |

| $d_{in}$   | 71μm   |  |  |  |

| (a)        |        |  |  |  |

| Parameters       | Values  |  |  |  |  |

|------------------|---------|--|--|--|--|

| $C_{t-t}$        | 120.4fF |  |  |  |  |

| $C_{t\text{-}s}$ | 64.6fF  |  |  |  |  |

| R(f)             | 11Ω     |  |  |  |  |

| $L_s$            | 11.7nH  |  |  |  |  |

| Q                | 16.1    |  |  |  |  |

| $f_{SR}$         | 3.8GHz  |  |  |  |  |

| LQ Product       | 188nH   |  |  |  |  |

| (b)              |         |  |  |  |  |

Table 1. (a) Input parameters and (b) simulation results at 2.4GHz.

higher current density at the edges of metal lines. This is the so-called proximity effect.

The proximity effect can have a higher impact than the skin effect in increasing the wire resistance. In integrated circuits the proximity effect can be significant also at frequency below 500MHz. Meanwhile, the skin depth of copper is  $2.1\mu m$  at 1GHz, and its influence is therefore limited for typical integrated inductors.

According to [4], the proximity effect begins to become significant at  $\omega_{crit}$ :

$$\omega_{crit} = \frac{3.1}{\mu} \left( \frac{w+s}{w^2} \right) R_{\square} \tag{12}$$

where  $R_{\square}$  is the sheet resistance of the wire. And the AC resistance including proximity effect is:

$$R_{prox}(f) = R_{DC} \left[ 1 + \frac{1}{m} \cdot \left( \frac{2\pi}{\omega_{crit}} \right)^2 \cdot f^2 \right]$$

(13)

where m is a layout-dependent parameter. Simulations show m is approximately equal to ten.

There is a misunderstanding that w should be as large as possible to improve the inductor quality by minimizing the winding resistance. The proximity effect is considered first, from (12) and (13) we see  $\omega_{crit}$  is inversely proportional to w and R(f) increases nonlinearly after  $\omega_{crit}$ . The situation is similar for the skin effect, when w is larger than the skin depth.

Clearly, w should be set with careful attention to make a good balance between the DC and AC resistance. If there is not much freedom to increase w, how can we then improve the quality of the inductor? The answer, instead, is to decrease w. From (5)–(7), for a given area and filling ratio, more turns can be implemented with a smaller w. Hence more inductance and higher Q can be obtained. Moreover, a higher  $\omega_{crit}$  can also be obtained, which is very important for high frequency performance. The major drawback is a reduced self-resonance frequency due to larger total turn-to-turn capacitance,  $C_{t-t}$ .

Considering all the points mentioned above, a nine-turn center-tapped symmetrical octagonal inductor was designed. The turns of the inductor were implemented in the combination of M7, CB and AP layers ( $R_{\square}=12\mathrm{m}\Omega/\square$ ). A patterned-ground shield was utilized in M1 layer to minimize substrate loss. The inductor performance was simulated using FastHenry. *Table 1* summarizes the input parameters and simulation results.

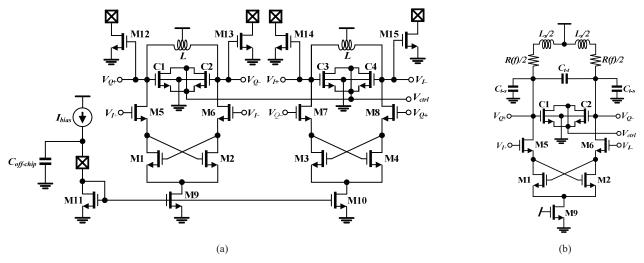

Fig. 4. (a) Overall schematic and (b) simulation schematic for the QVCO

## IV. VARACTOR

Fig. 3 shows example C-V curves of accumulation-mode and inversion-mode varactors. Clearly, the inversion-mode varactor is more favorable for low-power applications because of its sharper transition, which results in a larger achievable large-signal average capacitance range with limited output swing compared to its accumulation-mode counterpart. However, the sharper transition also means they are more sensitive to substrate noise [5], thus it may be necessary to put the varactor inside a deep n-well to avoid the noise coupling. nMOS is used because electrons have higher mobility than holes, hence a lower series resistance is obtained.

# V. QUADRATURE VCO

Compared to other QVCO topologies [6][7][8], the series QVCO [9] (S-QVCO) shows a good compromise between power consumption, area and complexity [10]. The major drawback is that the parasitic capacitance of coupling transistors degrades the tuning range. However, in sub-100nm CMOS processes, this capacitance is not significant anymore.

The overall schematic is shown in *Fig. 4a*. The reference current source is implemented off-chip to provide more freedom to control the measurement. M5–M8 are the coupling transistors.  $C_{off-chip}$  is added to filter out the noise contributed by the reference current source and the transistor M11. Open-drain buffers M12–M15 are added to output the quadrature signals off-chip. C1–C4 are nMOS inversion-mode varactors. Cross coupled nMOS negative-resistance pairs are used as they have better driving ability at a given area than their pMOS counterparts.

## V. SIMULATION RESULTS

Because the parasitic extraction tools for the 65-nm process were not available up to the moment this paper is written, only pre-layout simulations were performed.

The single- $\pi$  lumped inductor model was adopted for the circuit simulation because it gives more insight to the system and shorter simulation time compared to its S-parameter counterpart [11]. The drawback is that it is only accurate for a limited frequency range because of the rapid change of R(f) at radio frequencies. The simulation schematic, only one VCO is shown for readability, appears in Fig.~4b.

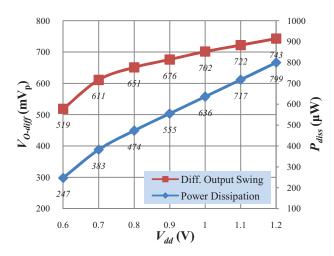

Fig. 5 shows  $V_{O-diff}$  and power dissipation at different  $V_{dd}$  when  $f_o$  is 2.4GHz. When  $V_{dd}$  is between 0.7V and 1.2V,  $V_{O-diff}$

Fig. 5. Power dissipation and output swing vs.  $V_{dd}$ .

increases constantly with  $V_{dd}$  because short-channel effects change the output current of the current mirrors (M9 and M10). When  $V_{dd}$  is smaller than 0.7V, the transistors enter the weak-inversion region, and  $V_{O\text{-}diff}$  and the power dissipation drop rapidly.

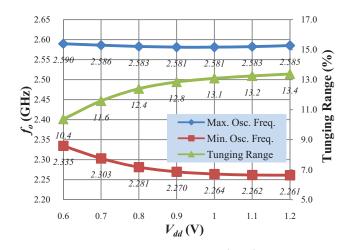

Fig. 6. Tuning range vs. supply voltage.

Despite R(f) changing rapidly, the oscillating frequency of the QVCO is not affected if Q is high enough. This allows the single- $\pi$  model to be used when simulating the frequency tuning range. The result is depicted in Fig.~6. When  $V_{dd}$  is below 0.8V,  $V_{O\text{-}diff}$  is not large enough to exercise the entire

| Design | Technology  | $f_o(\mathrm{GHz})$ | $V_{dd}(V)$ | $P_{diss}$ (mW) | Tuning Range (%) | L(1MHz) (dBc/Hz)      | FoM (dB) |

|--------|-------------|---------------------|-------------|-----------------|------------------|-----------------------|----------|

| This   | 65nm CMOS   | 2.4                 | 0.6         | 0.247           | 10.4             | -113.4                | 187      |

| Work   |             |                     | 0.8         | 0.474           | 12.4             | -116.6                | 187.4    |

|        |             |                     | 1.0         | 0.636           | 13.1             | -118                  | 187.5    |

|        |             |                     | 1.2         | 0.799           | 13.4             | -119.3                | 187.9    |

| [6]    | 0.25μm CMOS | 1.8                 | 2.5         | 20              | 17               | -143 @3MHz ∆ <i>f</i> | 185.5    |

| [9]    | 0.35μm CMOS | 1.8                 | 2           | 50              | 18               | -140 @3MHz ∆ <i>f</i> | 182      |

| [7]    | 0.18μm CMOS | 17                  | 1           | 5               | 16.5             | -110                  | 187.6    |

| [8]    | 0.25μm CMOS | 4.88                | 1.8         | 22              | 13               | -125                  | 185      |

| [12]   | 0.18μm CMOS | 5.1                 | 1.8         | 27.7            | 17               | -132.6                | 192      |

Table 2. Summary of simulation results, and comparisons to other published QVCOs

capacitance transition of the varactors. This confines the tuning range to 10.4% at 0.6V supply, and 11.6% at 0.7V. Otherwise, the tuning range is about 13%.

To fairly compare different VCOs, FoM is usually adopted and defined as:

$$FoM = 10 \log \left[ \left( \frac{f_o}{\Delta f} \right)^2 \cdot \frac{1}{\mathcal{L}(\Delta f) \cdot P_{diss}|_{mW}} \right]$$

(14)

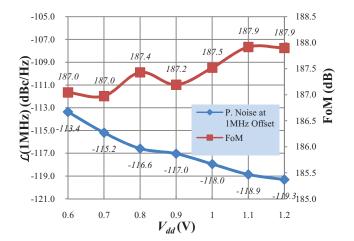

*Fig.* 7 depicts the phase noise at 1MHz offset and the corresponding FoM of the QVCO. Note that the FoM is better than 187dB at all interesting supply voltages.

A summary of the simulation results and comparisons to other recently published QVCOs are shown in *Table 2*. The pre-layout simulations show that the designed QVCO performs very well, especially in terms of power dissipation, and is competitive to the state-of-the-art QVCOs.

## VI. CONCLUSION

The design of an ultra-low-power QVCO in a 65nm CMOS process has been presented. A high performance center-tapped octagonal inductor with a LQ product of 188nH at 2.4GHz and an  $f_{SR}$  of 3.8GHz was designed. This results in a very low power dissipation of 247 $\mu$ W at 0.6V supply according to pre-layout simulations. At this supply voltage, the tuning range and the phase noise at 1MHz offset are 10.4% and -113.4dBc/Hz, respectively. The FoM is better than 187dB at all interesting supply voltages, which is competitive to the state-of-the-art QVCOs.

# REFERENCES

- [1] S. S. Mohan et al., "Simple Accurate Expressions for Planar Spiral Inductances," *IEEE JSSC*, vol. 34, pp. 1419–1424, Oct. 1999.

- [2] N. Troedsson et al., "A Distributed Capacitance Analysis of Co-Planar Inductors for a CMOS QVCO with Varactor Tuned Buffer Stage," *Analog Integrated Circuits and Signal Processing*, vol. 42, pp. 7-19, Jan. 2005.

- [3] D. Kehrer, Design of Monolithic Integrated Lumped Transformers in Silicon-based Technologies up to 20 GHz, Diplomarbeit, Vienna Uni. of Technology, 2000.

- [4] W. B. Kuhn et al., "Analysis of Current Crowding Effects in Multiturn Spiral Inductors," *IEEE Trans. on Microwave Theory and Tech.*, vol. 49, pp. 31–38, Jan. 2001.

Fig. 7. Phase noise and FoM vs. supply voltage.

- [5] R. L. Bunch et al., "Large-Signal Analysis of MOS Varactors in CMOS –Gm LC VCOs," *IEEE JSSC*, vol. 38, pp. 1325–1332, Aug. 2003.

- [6] M. Tiebout, "Low-Power Low-Phase-Noise Differentially Tuned Quadrature VCO Design in Standard CMOS," *IEEE JSSC*, vol. 36, pp. 1018–1024, Jul. 2001.

- [7] A. W. L. Ng et al., "A 1-V 17-GHz 5-mW CMOS Quadrature VCO Based on Transformer Coupling," *IEEE JSSC*, vol. 42, pp. 1933–1941, Sep. 2007.

- [8] S. L. J. Gierkink et al., "A Low-Phase-Noise 5-GHz CMOS Quadrature VCO Using Superharmonic Coupling," *IEEE JSSC*, vol. 38, pp. 1148–1154, Jul. 2003.

- [9] P. Andreani et al., "Analysis and Design of a 1.8-GHZ CMOS LC Quadrature VCO," *IEEE JSSC*, vol. 37, pp. 1737–1747, Dec. 2002.

- [10] K. K. Lee, *Design of Ultra-Low-Power LC Quadrature VCO*, M.Sc. Dissertation, Lund University, 2009.

- [11] A. V. Sathanue et al., Design, Analysis and Modeling of On-Chip Transformers for RF Applications and Development of a Transformer Design Tool, M.Sc. Dissertation, Lund University, 2004.

- [12] C. W. Yao et al. et al., "A Phase-Noise Reduction Technique for Quadrature LC-VCO with Phase-to-Amplitude Noise Conversion," in *ISSCC*, pp. 196–197, 2006.