# **Low-Frequency Noise in Nanowire and Planar III-V MOSFETs**

Hellenbrand, Markus; Kilpi, Olli-Pekka; Svensson, Johannes; Lind, Erik; Wernersson, Lars-Erik

Published in:

Microelectronic Engineering

DOI:

10.1016/j.mee.2019.110986

2019

# Link to publication

Citation for published version (APA): Hellenbrand, M., Kilpi, O.-P., Svensson, J., Lind, E., & Wernersson, L.-E. (2019). Low-Frequency Noise in Nanowire and Planar III-V MOSFETs. *Microelectronic Engineering*, Article 110986. https://doi.org/10.1016/j.mee.2019.110986

Total number of authors:

Creative Commons License: CC BY-NC-ND

### General rights

Unless other specific re-use rights are stated the following general rights apply:

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

• You may not further distribute the material or use it for any profit-making activity or commercial gain

- You may freely distribute the URL identifying the publication in the public portal

Read more about Creative commons licenses: https://creativecommons.org/licenses/

#### Take down policy

If you believe that this document breaches copyright please contact us providing details, and we will remove access to the work immediately and investigate your claim.

Download date: 07. Dec. 2025

# Low-Frequency Noise in Nanowire and Planar III-V MOSFETs

Markus Hellenbrand\*, Olli-Pekka Kilpi, Johannes Svensson, Erik Lind, Lars-Erik Wernersson

Department of Electrical and Information Technology, Lund University, Box 118, 221 00 Lund, Sweden

#### **Abstract**

Nanowire geometries are leading contenders for future low-power transistor design. In this study, low-frequency noise is measured and evaluated in highly scaled III-V nanowire metal-oxide-semiconductor field-effect transistors (MOS-FETs) and in planar III-V MOSFETs to investigate to what extent the device geometry affects the noise performance. Number fluctuations are identified as the dominant noise mechanism in both architectures. In order to perform a thorough comparison of the two architectures, a discussion of the underlying noise model is included. We find that the noise performance of the MOSFETs in a nanowire architecture is at least comparable to the planar devices. The input-referred voltage noise in the nanowire devices is superior by at least a factor of four.

Keywords: III-V, Nanowire (NW), MOSFET, Low-Frequency Noise, Gate Oxide Defects, Border Traps

### 1. Introdution

The continuous improvement of the metal-oxide-semiconductor field-effect transistor (MOSFET) has been one of the major driving forces in electronics. In the future, further improvements of the MOSFET will require more innovative measures than the so far tremendously successful conventional geometrical scaling. Common suggestions include gate-all-around architectures and novel materials at the device level [1–4], and monolithic 3D integration at the system level [4, 5]. III-V nanowire (NW) MOSFETs, especially in a vertical architecture, can facilitate all these approaches at once and they have already demonstrated competitive or even superior performance in comparison with planar MOSFETs or FinFETs both in simulation [6] and in experiment [7–10].

In this paper we compare planar and NW III-V MOSFETs with similar channel and gate-oxide materials and investigate to what extent the change in architecture affects the low-frequency noise (LFN) of the devices, a property which is important as a technology quality metric at the device level, and for analog circuit performance at the system level [11]. Although LFN has been studied in both planar [12] and in NW [13] III-V MOSFETs, the two architectures have not yet been compared directly. The first part of the article describes the measured devices and the measurement setup. The comparison of the two MOSFET architectures comprises two metrics: the gate oxide defect density  $N_{\rm bt}$  and the input-referred gate voltage noise power  $S_{\rm V_G}$ . In order to facilitate a detailed comparison of  $N_{\rm bt}$ , its calculation is accompanied by a detailed discussion of the LFN model.

### 2. Devices and Measurement Setup

The following device descriptions focus on the channel and the gate stack as the two parts, which are most important for LFN. References are provided for further processing details.

For the vertical nanowire (vNW) devices, single nanowires were grown by metal-organic vapor-phase epitaxy on an n<sup>+</sup>-InAs buffer layer integrated on Si. The nanowires were graded from intrinsic InAs on the source side to n<sup>+</sup>-InGaAs on the drain side. During the InGaAs growth, an n<sup>+</sup>-shell was formed around the InAs source to reduce the access resistance. After growth, the nanowires were covered with a top metal and a bottom spacer, so that the

Email address: markus.hellenbrand@eit.lth.se (Markus Hellenbrand)

<sup>\*</sup>Corresponding author

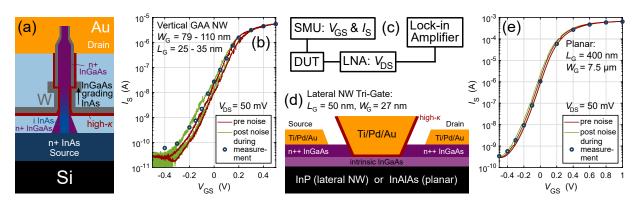

channel area could be thinned down by digital etching (alternating surface oxidation and oxide etching) to form a recess gate. After digital etching, the 1 nm  $Al_2O_3/4$  nm  $HfO_2$  bilayer gate oxide (equivalent oxide thickness (EOT)  $\approx 1.5$  nm) and the 60 nm W gate metal were applied by atomic layer deposition (ALD) and by sputtering, respectively. A schematic of the device structure is provided in Fig. 1(a) and details about the processing can be found in [14]. Fig. 1(b) provides transfer curves representative of the vNW MOSFETs along with the gate lengths and the channel widths of the different measured devices. For the vNW MOSFETs, the channel width corresponds to the nanowire circumference.

For the planar reference devices, the channel consisted of not intentionally doped, 10-nm-thick InGaAs, which was grown by molecular beam epitaxy. In order to investigate differences between different gate oxides, three different ALD high-κ gate oxides were used in the planar devices: 5 nm Al<sub>2</sub>O<sub>3</sub>, 4 nm HfO<sub>2</sub>, and 6.5 nm HfO<sub>2</sub>. Evaporated Ti/Pd/Au was used as the gate metal. A schematic of the planar device structure is provided in Fig. 1(d) and details about the processing can be found in [15]. Fig. 1(e) provides a transfer curve representative of the planar MOSFETs along with the gate lengths and widths of the measured devices.

Figure 1: Schematics of the measured structures (a) & (d), the measurement setup (c), and representative transfer curves for the vertical (b) and the planar devices (e). Similar materials were used for the different devices and all devices exhibit good gate control with typically at least four orders of magnitude current modulation.

As an intermediate reference between the planar and the vNW MOSFETs, lateral NW MOSFETs from [16] are included in the analysis as well. Their structure was similar to that of the planar devices, although with a single lateral nanowire as the channel, formed by selective area growth, and with a gate oxide similar to that of the vNW devices. Prior to high- $\kappa$  application, the nanowires were digitally etched, then sulfur-passivated and annealed in an  $N_2$  atmosphere. Details about processing of the lateral nanowire devices can be found in [17] and their dimensions are included in Fig. 1(d).

Fig. 1(c) depicts the LFN measurement setup. The drain current of the device under test was measured by a low-noise amplifier (LNA), which also supplied the drain bias  $V_{\rm DS} = 50$  mV. The current noise power spectral density  $S_{\rm I_D}$  was measured by a lock-in amplifier, which recorded the signal from the LNA. Gate and source bias were supplied by a Source/Measure Unit, which also measured the corresponding currents. For all measured devices, the gate current was at least one order of magnitude lower than the lowest source-drain current and in some cases it was below the measurement noise floor.

## 3. Results and Analysis

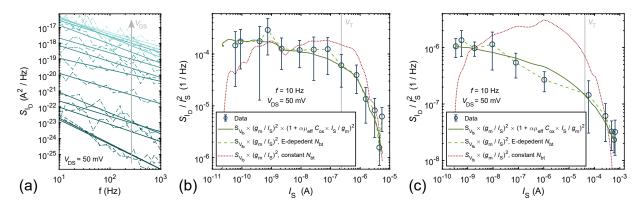

LFN in MOSFETs is typically explained as either number fluctuations, caused by gate oxide defects, or as mobility fluctuations, often described with the Hooge model [18]. The two mechanisms can be identified by the dependence of the measured  $S_{\rm I_D}$  on the device current  $I_{\rm S}$ . In the case of mobility fluctuations,  $S_{\rm I_D}/I_{\rm S}^2$  is expected to be proportional to  $1/I_{\rm S}$ , which was not observed for any of the measured devices. Instead, the measured  $S_{\rm I_D}$  was roughly proportional to the transconductance squared (Fig. 2(b) and (c)), which identified number fluctuations as the dominant LFN mechanism. When measured as a function of the frequency f, LFN typically exhibits a  $1/f^{\gamma}$  shape with  $\gamma \approx 1$ , where, in the case of number fluctuations, the value of  $\gamma$  depends on the spatial distribution of gate oxide defects. The  $1/f^{\gamma}$

dependence was verified in Fig. 2(a), which presents a measurement for a vNW MOSFET, which is representative for the lateral NW and the planar devices as well.

In the case of number fluctuations, electrons from the MOSFET channel tunnel into and out of gate oxide defects with a certain time constant that determines the corresponding frequency component of  $S_{\rm ID}$ . The changing charge states in the oxide cause fluctuations in the flatband voltage and in carrier scattering, which then cause fluctuations in the device current. The two effects are called number fluctuations and correlated mobility fluctuations (CMF), respectively, and the relation between  $S_{\rm ID}$  and the gate oxide defect density  $N_{\rm bt}$  can be derived as [19]

$$S_{\rm I_D} = \frac{q^2 k_{\rm B} T \lambda N_{\rm bt}}{f^{\gamma} L_{\rm G} W_{\rm G} C_{\rm g}^2} \left( 1 + \frac{\alpha \mu_{\rm eff} C_{\rm g} I_{\rm S}}{g_{\rm m}} \right) g_{\rm m}^2 = S_{\rm V_{fb}} \left( 1 + \frac{\alpha \mu_{\rm eff} C_{\rm g} I_{\rm S}}{g_{\rm m}} \right) g_{\rm m}^2, \tag{1}$$

where  $g_{\rm m}$  is the transconductance, q the elemental charge,  $k_{\rm B}$  the Boltzmann constant, T the temperature,  $\lambda$  the tunneling attenuation length (calculated by the WKB approximation),  $L_{\rm G}$  and  $W_{\rm G}$  are the gate length and width, respectively, and  $C_{\rm g}$  is the oxide capacitance in series with the quantum capacitance, which has to be taken into account for III-V MOSFETs. The prefactor including  $N_{\rm bt}$  in the left term is the detailed expression for the power spectral density of the flatband voltage noise  $S_{\rm V_{fb}}$ . For the term in parentheses,  $I_{\rm S}$  is the device current,  $\mu_{\rm eff}$  the effective carrier mobility and  $\alpha$  is the scattering parameter, which describes the change in mobility due to a change of charge in the gate oxide. To take into account screening due to charges in the channel,  $\alpha$  decreases with increasing current. This can be expressed empirically as  $\alpha = \alpha_0 - \alpha_1 \ln(N_{\rm q})$ , where  $\alpha_0$  and  $\alpha_1$  are fitting parameters and  $N_{\rm q}$  is the number of charges in the channel [20]. Here, instead of calculating  $N_{\rm q}$  in detail, we express it as proportional to the device current  $I_{\rm S}$ , which is an acceptable approximation, since  $\ln(N_{\rm q})$  is multiplied by the fitting parameter  $\alpha_1$ .

The derivation of (1), which relies on the assumption of elastic tunneling as the trapping/de-trapping mechanism, calls for a short side note. Evidence, in particular from reliability measurements [21], but also from some LFN measurements [22, 23], point towards inelastic rather than elastic tunneling as the charge exchange mechanism. However, since tunneling is still part of the inelastic mechanism, the assumption of elastic tunneling constitutes a lower limit of the inelastic model and it is as such that it was used in this study. This lower limit assumption especially affects the values for  $N_{\rm bt}$ , calculated in the following, which thus also constitute a lower limit.

Results from different measurement techniques in literature [24–27] strongly suggest that  $N_{\rm bt}$  varies with respect to energy with a minimum in vicinity to the InGaAs conduction band and increasing both above and below. Since different  $V_{\rm GS}$  in the LFN measurement probe different energy levels in the gate oxide,  $N_{\rm bt}$  is expected to vary with respect to the device current  $I_{\rm S}$ . With two varying fitting parameters,  $N_{\rm bt}$  and  $\alpha$ , virtually arbitrary results could be obtained by fitting (1) to the measured data. Therefore, instead of choosing a random partitioning of the effects of a distributed  $N_{\rm bt}$  and the CMF, we consider the two effects individually by studying the two "extreme" cases of (i) CMF with a constant  $N_{\rm bt}$  and (ii) a varying  $N_{\rm bt}$  without the influence of CMF (i.e.  $\alpha = 0$ ).

Figure 2: (a) Noise current power spectral density  $S_{\rm I_D}$  as a function of the frequency for a vNW MOSFET. The  $1/f^{\gamma}$  dependence with  $\gamma$  close to one is typical of LFN. (b) and (c)  $S_{\rm I_D}$  at a fixed frequency of 10 Hz for a vertical and a planar device, respectively. Circles represent the measured  $S_{\rm I_D}$  with the measurement standard deviation as error bars, lines represent different models with dependences according to the legend entries. Dark green, solid: Number and correlated mobility fluctuations with a constant  $N_{\rm bt}$ . Light green, broken: Pure number fluctuations with an energy-dependent  $N_{\rm bt}$ . Red, dotted: Reference for the assumption of pure number fluctuations with a constant gate oxide defect density  $N_{\rm bt}$ .

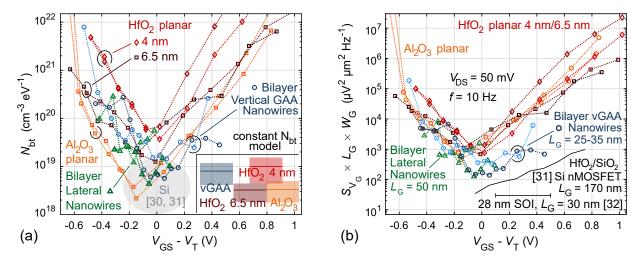

Case (i) results in reasonable fits for the vertical and the planar devices, as demonstrated by the dark green, solid lines in Fig. 2(b) and (c). The corresponding constant  $N_{\rm bt}$  are summarized in the inset of Fig. 3(a), where lines indicate the average  $N_{\rm bt}$  for the respective architecture and shaded boxes indicate the standard deviation of the residuals. For the fits in Fig. 2(a) and (b), values of  $\mu_{\rm eff} = 1300~{\rm cm^2/Vs}$  [13] and 3500 cm<sup>2</sup>/Vs [28] were used for the vertical and the planar devices, respectively,  $C_{\rm g}$  was typically about half the value of the geometrical oxide capacitance, and  $\alpha$  typically varied between  $2 \times 10^4$  and  $10^3~{\rm Vs/C}$ , which is in agreement with values from literature [11, 29, 30]. The simplest approach to (ii) is calculating  $N_{\rm bt}$  pointwise from the measured  $S_{\rm I_D}$  and (1) (with  $\alpha = 0$ ). The resulting  $N_{\rm bt}$  are presented in Fig. 3(a) and their shapes resemble the findings in literature. For both (i) and (ii), the values for the NW devices are comparable to those of the planar references and they are comparable to planar Si MOSFETs with HfO<sub>2</sub> gate oxides and a SiO<sub>2</sub> interface layer (EOT <2 nm, values adapted from [30] and [31]). In case (ii), the NW devices actually achieve lower values than both of the planar HfO<sub>2</sub> references. For the lateral NW MOSFETs, (i) did not properly model the measured data over the whole measurement range, whereas (ii) resulted in good fits, so that the lateral NW devices are not included in the inset of Fig. 3(a).

Figure 3: (a) Gate oxide defect density  $N_{\rm bt}$  calculated with two models. (i) Inset: Constant  $N_{\rm bt}$ , correlated mobility fluctuations. The lines represent the average values for all measured devices and the shaded boxes the standard deviation of the residuals. (ii) Main: Energy-dependent  $N_{\rm bt}$ , no correlated mobility fluctuations. The differences between the two models are larger for the planar devices. Shaded oval as reference for  $HfO_2$  on Si with a thin  $SiO_2$  interface layer from [30] and [31]. (b) Input-referred voltage noise power spectral density  $S_{\rm V_G}$  normalized with the gate area. Black lines as references for [31] as in (a) and commercial SOI [32]. The literature values from [30] and [31] are shifted with respect to  $V_{\rm GS}$  so that they coincide with the measured minima. The metrics in both (a) and (b) reveal that MOSFETs in a (vertical or lateral) nanowire architecture are not degraded when compared with planar MOSFETs. Especially for the input-referred noise  $S_{\rm V_G}$ , the nanowire devices actually achieve better values.

Although in most cases, both (i) and (ii) reproduced the measured data reasonably well, neither of the two models can be assumed to be sufficient on their own. (i) does not take into account the distributed nature of  $N_{\rm bt}$ , while (ii) yields unphysical values for the highest and lowest  $V_{\rm GS}$  (see Fig. 3(a)). Thus, a combination of both models is likely so that the actual  $N_{\rm bt}$  resembles the shape of (ii), but with a shallower distribution and slightly lower overall values. Irrespective of the exact contribution of either model, it can be concluded that the mere change from a conventional planar to a NW architecture does not cause a degradation of the gate oxide in terms of LFN performance. In the comparison of the different high- $\kappa$  gate oxides in the planar architecture, the HfO<sub>2</sub> oxides, especially the thinner ones, tend to exhibit higher values for  $N_{\rm bt}$  than the Al<sub>2</sub>O<sub>3</sub> oxides, when CMF are disregarded (i). Upon inclusion of CMF (ii), the differences are diminished, although the thin (4 nm) HfO<sub>2</sub> still tends to yield the highest values. These trends are most likely related to the ALD growth dynamics, but a more thorough investigation is beyond the scope of this study.

Since the differences in  $N_{bt}$  between (i) and (ii) are more prominent for the planar than for the NW devices (especially for  $HfO_2$ ), it can be concluded that the relative contribution of CMF is stronger in the planar devices. This conclusion is supported by the comparison of the curves for (i) with the dark red, dotted reference curves in Fig. 2(b) and (c), which represent a constant  $N_{bt}$  without CMF. For the planar devices, it requires a larger contribution of CMF

to merge the two curves than it does for the NW devices. Since the effect of CMF was smaller or even negligible on both the vertical and the lateral NW MOSFETs, the influence of CMF seems to be related to the dimensions of the transistors rather than the lateral or vertical architecture. With large gate areas of  $L_{\rm G}=400$  nm and  $W_{\rm G}=7.5$  µm in the planar MOSFETs, mobility and scattering play an important role in carrier transport. With much shorter  $L_{\rm G}=25$ -35 nm (vertical) and 50 nm (lateral), the NW MOSFETs are governed by quasi-ballistic carrier transport [28] and they are approaching the one dimensional regime, which diminishes the influence of scattering. Furthermore, the larger surface-to-volume ratio in the nanowires is likely to entail a larger ratio of pure number fluctuations over correlated mobility fluctuations.

As a further comparison besides  $N_{\rm bt}$ , Fig. 3(b) presents the input-referred gate voltage noise power spectral density  $S_{\rm V_G} = S_{\rm I_D}/g_{\rm m}^2$ . This metric does not rely on a specific model, since it merely describes how much of a voltage fluctuation would be required at the gate terminal of a transistor without gate oxide defects to cause the same fluctuations in the device current that were measured for the actual transistor. Thus,  $S_{\rm V_G}$  indicates the minimum size of a signal that could still be amplified by the transistor, if it was used e.g. as the input stage of an amplifier. Fig. 3(b) shows that in terms of  $S_{\rm V_G}$ , the nanowire devices perform better than the planar references by typically at least a factor of four. For comparison with Si, Fig. 3(b) provides reference values for the same devices as Fig. 3(a) and furthermore for 28 nm silicon-on-insulator (SOI) MOSFETs, the  $S_{\rm V_G}$  values of which were calculated from [32] and [33]. The values for the Si and the nanowire devices differ by only a factor three to five. With further optimization of the gate stack in the NW MOSFETs, it should be possible to overcome the remaining difference as well.

#### 4. Conclusions

We measured and compared LFN in nanowire and in planar III-V MOSFETs. Number fluctuations were identified to dominate the LFN in both types of devices and two models were discussed in order to obtain values for the gate oxide defect distribution  $N_{bt}$ : number fluctuations with correlated mobility fluctuations for a constant  $N_{bt}$  and pure number fluctuations with an energy-dependent distribution of  $N_{bt}$ . The results for  $N_{bt}$  suggest that a combination of both is likely, where NW devices are less susceptible to correlated mobility fluctuations. Both models resulted in comparable values for  $N_{bt}$  in the NW and the planar architecture, which demonstrates that the change from a planar to a NW architecture does not deteriorate the gate oxide in terms of low-frequency noise. This, together with the lower values for the input-referred gate voltage noise in nanowire MOSFETs, demonstrates that the performance of the nanowire MOSFET architecture is not inhibited by low-frequency noise.

# Acknowledgements

We thank C. Möhle for the LFN data of the lateral NW MOSFETs, C. Zota for fabricating the lateral NW MOSFETs, and J. Mo for fabricating the planar MOSFETs.

This work was supported in part by the Swedish Research Council, in part by the Swedish Foundation for Strategic Research, and in part by the European Union Horizon 2020 Program INSIGHT under grant agreement number 688784.

#### References

- [1] H. Riel, L.-E. Wernersson, M. Hong, J. A. del Alamo, III–V compound semiconductor transistors—from planar to nanowire structures, MRS Bulletin 39 (8) (2014) 668–677, doi:10.1557/mrs.2014.137.

- [2] N. Loubet, T. Hook, P. Montanini, C.-W. Yeung, S. Kanakasabapathy, M. Guillom, T. Yamashita, J. Zhang, X. Miao, J. Wang, A. Young, R. Chao, M. Kang, Z. Liu, S. Fan, B. Hamieh, S. Sieg, Y. Mignot, W. Xu, S.-C. Seo, J. Yoo, S. Mochizuki, M. Sankarapandian, O. Kwon, A. Carr, A. Greene, Y. Park, J. Frougier, R. Galatage, R. Bao, J. Shearer, R. Conti, H. Song, D. Lee, D. Kong, Y. Xu, A. Arceo, Z. Bi, P. Xu, R. Muthinti, J. Li, R. Wong, D. Brown, P. Oldiges, R. Robison, J. Arnold, N. Felix, S. Skordas, J. Gaudiello, T. Standaert, H. Jagannathan, D. Corliss, M.-H. Na, A. Knorr, T. Wu, D. Gupta, S. Lian, R. Divakaruni, T. Gow, C. Labelle, S. Lee, V. Paruchuri, H. Bu, M. Khare, Stacked nanosheet gate-all-around transistor to enable scaling beyond FinFET, in: 2017 Symposium on VLSI Technology, 2017, pp. T230–T231. doi:10.23919/VLSIT.2017.7998183.

- [3] S. Salahuddin, K. Ni, S. Datta, The era of hyper-scaling in electronics, Nature Electronics 1 (8) (2018) 442–450. doi:10.1038/s41928-018-0117-x.

- [4] F. Balestra, M. Graef, B. Huizing, Y. Hayashi, H. Ishiuchi, T. Conte, P. Gargini, The international roadmap for devices and systems 2017 edition, https://irds.ieee.org/roadmap-2017, accessed: 2019-04-12.

- [5] M. M. Shulaker, G. Hills, R. S. Park, R. T. Howe, K. Saraswat, H.-S. P. Wong, S. Mitra, Three-dimensional integration of nanotechnologies for computing and data storage on a single chip, Nature 547 (2017) 74–78. doi:10.1038/nature22994.

- [6] D. Yakimets, G. Eneman, P. Schuddinck, T. H. Bao, M. G. Bardon, P. Raghavan, A. Veloso, N. Collaert, A. Mercha, D. Verkest, A. V. Thean, K. De Meyer, Vertical GAAFETs for the ultimate CMOS scaling, IEEE Transactions on Electron Devices 62 (5) (2015) 1433–1439. doi:10.1109/TED.2015.2414924.

- [7] O. Kilpi, J. Svensson, E. Lind, L. Wernersson, Electrical properties of vertical InAs/InGaAs heterostructure MOSFETs, IEEE Journal of the Electron Devices Society 7 (2019) 70–75. doi:10.1109/JEDS.2018.2878659.

- [8] S. Johansson, E. Memisevic, L.-E. Wernersson, E. Lind, High-frequency gate-all-around vertical InAs nanowire MOSFETs on Si substrates, IEEE Electron Device Letters 35 (5) (2014) 518–520. doi:10.1109/LED.2014.2310119.

- [9] C. B. Zota, F. Lindelow, L.-E. Wernersson, E. Lind, InGaAs tri-gate MOSFETs with record on-current, in: 2016 IEEE International Electron Devices Meeting, 2016, pp. 3.2.1–3.2.4. doi:10.1109/IEDM.2016.7838336.

- [10] C. B. Zota, F. Lindelöw, L.-E. Wernersson, E. Lind, High-frequency InGaAs tri-gate MOSFETs with f<sub>max</sub> of 400 GHz, Electronics Letters 52 (22) (2016) 1869–1871. doi:10.1049/el.2016.3108.

- [11] M. von Haartman, M. Östling, Low-Frequency Noise in Advanced MOS Devices, Springer, 2007. doi:10.1007/978-1-4020-5910-0.

- [12] T. Karatsori, M. Pastorek, C. Theodorou, A. Fadjie, N. Wichmann, L. Desplanque, X. Wallart, S. Bollaert, C. Dimitriadis, G. Ghibaudo, Static and low frequency noise characterization of ultra-thin body InAs MOSFETs, Solid-State Electronics 143 (2018) 56 – 61. doi:https://doi.org/10.1016/j.sse.2017.12.001.

- [13] K.-M. Persson, B. G. Malm, L.-E. Wernersson, Surface and core contribution to 1/f-noise in InAs nanowire metal-oxide-semiconductor field-effect transistors, Applied Physics Letters 103 (3) (2013) 033508-1-033508-4. doi:10.1063/1.4813850.

- [14] O.-P. Kilpi, J. Svensson, J. Wu, A. R. Persson, R. Wallenberg, E. Lind, L.-E. Wernersson, Vertical InAs/InGaAs heterostructure metal-oxide-semiconductor field-effect transistors on Si, Nano Letters 17 (10) (2017) 6006–6010. doi:10.1021/acs.nanolett.7b02251.

- [15] G. Roll, J. Mo, E. Lind, S. Johansson, L.-E. Wernersson, Defect evaluation in InGaAs field effect transistors with HfO<sub>2</sub> or Al<sub>2</sub>O<sub>3</sub> dielectric 106 (20) (2015) 203503. doi:10.1063/1.4921483.

- [16] C. Möhle, C. Zota, M. Hellenbrand, E. Lind, 1/f and RTS noise in InGaAs nanowire MOSFETs, Microelectronic Engineering 178 (2017) 52 55, special issue of Insulating Films on Semiconductors (INFOS 2017). doi:https://doi.org/10.1016/j.mee.2017.04.038.

- [17] C. B. Zota, L.-E. Wernersson, E. Lind, High-performance lateral nanowire InGaAs MOSFETs with improved on-current, IEEE Electron Device Letters 37 (10) (2016) 1264–1267. doi:10.1109/LED.2016.2602841.

- [18] F. Hooge, 1/f noise is no surface effect, Physics Letters A 29 (3) (1969) 139 140. doi:https://doi.org/10.1016/0375-9601(69)90076-0.

- [19] G. Ghibaudo, O. Roux, C. Nguyen-Duc, F. Balestra, J. Brini, Improved analysis of low frequency noise in field-effect MOS transistors, physica status solidi (a) 124 (2) (1991) 571–581. doi:10.1002/pssa.2211240225.

- [20] A. Pacelli, S. Villa, A. L. Lacaita, L. M. Perron, Quantum effects on the extraction of MOS oxide traps by 1/f noise measurements, IEEE Transactions on Electron Devices 46 (5) (1999) 1029–1035. doi:10.1109/16.760413.

- [21] T. Grasser, Stochastic charge trapping in oxides: From random telegraph noise to bias temperature instabilities, Microelectronics Reliability 52 (1) (2012) 39 70, 2011 Reliability of Compound Semiconductors (ROCS) Workshop. doi:https://doi.org/10.1016/j.microrel.2011.09.002.

- [22] J. P. Campbell, J. Qin, K. P. Cheung, L. C. Yu, J. S. Suehle, A. Oates, K. Sheng, Random telegraph noise in highly scaled nMOSFETs, in: 2009 IEEE International Reliability Physics Symposium, 2009, pp. 382–388. doi:10.1109/IRPS.2009.5173283.

- [23] T. Nagumo, K. Takeuchi, T. Hase, Y. Hayashi, Statistical characterization of trap position, energy, amplitude and time constants by RTN measurement of multiple individual traps, in: 2010 International Electron Devices Meeting, 2010, pp. 2831–2834. doi:10.1109/IEDM.2010.5703437.

- [24] V. Putcha, J. Franco, A. Vais, S. Sioncke, B. Kaczer, Q. Xie, P. Calka, F. Tang, X. Jiang, M. Givens, N. Collaert, D. Linten, G. Groeseneken, BTI reliability of InGaAs nMOS gate-stack: On the impact of shallow and deep defect bands on the operating voltage range of III-V technology, in: 2017 IEEE International Reliability Physics Symposium (IRPS), 2017, pp. XT–8.1–XT–8.6. doi:10.1109/IRPS.2017.7936422.

- [25] B. Kaczer, J. Franco, P. Weckx, P. Roussel, V. Putcha, E. Bury, M. Simicic, A. Chasin, D. Linten, B. Parvais, F. Catthoor, G. Rzepa, M. Waltl, T. Grasser, A brief overview of gate oxide defect properties and their relation to MOSFET instabilities and device and circuit time-dependent variability, Microelectronics Reliability 81 (2018) 186 194. doi:https://doi.org/10.1016/j.microrel.2017.11.022.

- [26] G. Brammertz, A. Alian, D. H. Lin, M. Meuris, M. Caymax, W. Wang, A combined interface and border trap model for high-mobility substrate metal-oxide-semiconductor devices applied to In<sub>0.53</sub>Ga<sub>0.47</sub>As and InP capacitors, IEEE Transactions on Electron Devices 58 (11) (2011) 3890–3897. doi:10.1109/TED.2011.2165725.

- [27] S. Johansson, M. Berg, K. M. Persson, E. Lind, A high-frequency transconductance method for characterization of high-κ border traps in III-V MOSFETs 60 (2) (2013) 776–781. doi:10.1109/TED.2012.2231867.

- [28] C. B. Zota, D. Lindgren, L.-E. Wernersson, E. Lind, Quantized conduction and high mobility in selectively grown In<sub>x</sub>Ga<sub>1-x</sub>As nanowires, ACS Nano 9 (10) (2015) 9892–9897. doi:10.1021/acsnano.5b03318.

- [29] J. Jomaah, M. Fadlallah, G. Ghibaudo, Low frequency noise analysis in advanced CMOS devices, in: Advances in Innovative Materials and Applications, Vol. 324 of Advanced Materials Research, Trans Tech Publications, 2011, pp. 441–444. doi:10.4028/www.scientific.net/AMR.324.441.

- [30] D. Lopez, S. Haendler, C. Leyris, G. Bidal, G. Ghibaudo, Low-frequency noise investigation and noise variability analysis in high-k/metal gate 32-nm CMOS transistors, IEEE Transactions on Electron Devices 58 (8) (2011) 2310–2316. doi:10.1109/TED.2011.2141139.

- [31] E. Simoen, A. Veloso, Y. Higuchi, N. Horiguchi, C. Claeys, On the oxide trap density and profiles of 1-nm EOT metal-gate last CMOS transistors assessed by low-frequency noise, IEEE Transactions on Electron Devices 60 (11) (2013) 3849–3855. doi:10.1109/TED.2013.2279892.

- [32] E. G. Ioannidis, S. Haendler, A. Bajolet, T. Pahron, N. Planes, F. Arnaud, R. A. Bianchi, M. Haond, D. Golanski, J. Rosa, C. Fenouillet-Beranger, P. Perreau, C. A. Dimitriadis, G. Ghibaudo, Low frequency noise variability in high-k/metal gate stack 28nm bulk and FD-SOI CMOS transistors, in: 2011 International Electron Devices Meeting, 2011, pp. 18.6.1–18.6.4. doi:10.1109/IEDM.2011.6131581.

- [33] B. K. Esfeh, V. Kilchytska, V. Barral, N. Planes, M. Haond, D. Flandre, J.-P. Raskin, Assessment of 28nm UTBB FD-SOI technology platform for RF applications: Figures of merit and effect of parasitic elements, Solid-State Electronics 117 (2016) 130 137. doi:https://doi.org/10.1016/j.sse.2015.11.020.