# LUND UNIVERSITY

Vertical heterojunction InAs/InGaAs nanowire MOSFETs on Si with I $_{on}$  = 330  $\mu$ a/ $\mu$ m at  $I_{off} = 100 \text{ nA/µm} \text{ and } V_D = 0.5 \text{ v}$

Kilpi, Olli Pekka; Wu, Jun; Svensson, Johannes; Lind, Erik; Wernersson, Lars Erik

2017 Symposium on VLSI Technology, VLSI Technology 2017

10.23919/VLSIT.2017.7998191

2017

# Link to publication

Citation for published version (APA):

Kilpi, O. P., Wu, J., Svensson, J., Lind, E., & Wernersson, L. E. (2017). Vertical heterojunction InAs/InGaAs nanowire MOSFETs on Si with I = 330 μa/μm at I = 100 nA/μm and V = 0.5 v. In *2017 Symposium on VLSI Technology, VLSI Technology 2017* (pp. T36-T37). Article 7998191 IEEE<sup>D</sup> Institute of Electrical and Electronics Engineers Inc.. https://doi.org/10.23919/VLSIT.2017.7998191

Total number of authors:

General rights

Unless other specific re-use rights are stated the following general rights apply: Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights

- Users may download and print one copy of any publication from the public portal for the purpose of private study

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal

Read more about Creative commons licenses: https://creativecommons.org/licenses/

If you believe that this document breaches copyright please contact us providing details, and we will remove access to the work immediately and investigate your claim.

**LUND UNIVERSITY**

PO Box 117 221 00 Lund +46 46-222 00 00

Download date: 21. Dec. 2025

# Vertical Heterojunction InAs/InGaAs Nanowire MOSFETs on Si with $I_{on}=330$ $\mu A/\mu m$ at $I_{off}=100$ nA/ $\mu m$ and $V_D=0.5$ V

Olli-Pekka Kilpi, Jun Wu, Johannes Svensson, Erik Lind and Lars-Erik Wernersson Department of Electrical and Information Technology, Lund University, Box 118, Lund, Sweden E-mail: olli-pekka.kilpi@eit.lth.se

### **Abstract**

We present vertical InAs nanowire MOSFETs on Si with an In<sub>0.7</sub>Ga<sub>0.3</sub>As drain. The devices show  $I_{\rm on}$  and  $g_{\rm m}/SS$  record performance for vertical MOSFETs and  $I_{\rm off}$  below 1 nA/ $\mu$ m at  $V_{\rm D}$  0.5 V. We show a device with  $g_{\rm m}$ =1.4 mS/ $\mu$ m and SS=85 mV/dec, therefore having Q-value ( $g_{\rm m}/SS$ ) of 16. The device has  $I_{\rm on}$ =330  $\mu$ A/ $\mu$ m and 46  $\mu$ A/ $\mu$ m at  $I_{\rm off}$  100 nA/ $\mu$ m and 1 nA/ $\mu$ m, respectively. Furthermore, we show a device with SS=68 mV/dec and  $I_{\rm on}$ =88  $\mu$ A/ $\mu$ m at  $I_{\rm off}$  1 nA/ $\mu$ m and  $V_{\rm D}$  0.5 V.

#### Introduction

Performance evaluations have shown performance advantages for vertical MOSFETs at the 5 nm node, which makes them a viable option for extending the CMOS roadmap [1]. The vertical structure allows decoupling of the footprint from the gate-length and simultaneously reduced  $I_{\text{off}}$  due to the lack of substrate leakage. The III-V compound semiconductors, InAs and InGaAs, have shown improved performance compared to Si [2, 3]. However, III-V MOSFETs are typically not integrated on Si and suffer from comparably high  $I_{\text{off}}$  due to the narrow band gap and parasitic substrate leakage. Previously planar InGaAs MOSFETs on III-V substrates have achieved  $I_{\rm off}$  1 nA/ $\mu$ m by introducing wider band gap on drain side [4, 5]. In this work, we demonstrate vertical III-V nanowire MOSFETs on Si having  $I_{\text{off}}$  below 1 nA/ $\mu$ m by introducing a gate-all-around structure and an InGaAs drain. We further demonstrate a device with  $g_m=1.4$  mS/ $\mu$ m, SS=85 mV/dec and  $I_{\rm on}$ =330  $\mu$ A/ $\mu$ m at  $I_{\rm off}$  100 nA/ $\mu$ m and  $V_{\rm D}$  0.5 V.

# **Fabrication**

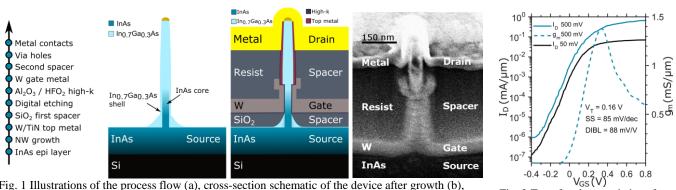

Process flow and schematics of the MOSFETs are shown in fig.1. The fabrication is started by growing a 300-nm-thick InAs n<sup>+</sup> source contact on the Si substrate by Metal Organic Vapor Phase Epitaxy and is followed by fabrication of three differently sized electron beam lithography defined gold particles (diameters 32, 36, and 40 nm). The nanowires are grown by the VLS method and includes 100 nm undoped InAs and a transition to highly doped In<sub>0.7</sub>Ga<sub>0.3</sub>As, which also overgrows the entire nanowire. The core diameter corresponds to the gold particle diameter, while the shell thickness is approximately 5 nm.

The MOSFET processing utilizes a self-aligned gate-last process in order to reduce the access resistance [6]. The process starts by forming a 10-nm-thick W/TiN top-metal contact with a contact length  $L_{\rm c}$ = 200 - 300 nm. A 50-nm-thick SiO<sub>2</sub> bottom spacer is then formed. Using the top metal and the bottom spacer as masks, the channel region is digitally etched by ozone oxidation and HCl wet etching until the highly doped shell is removed. An atomic layer deposited 1 nm / 4 nm Al<sub>2</sub>O<sub>3</sub>/HfO<sub>2</sub> bilayer (EOT ~ 1.5 nm) is deposited before applying 60-nm-thick W gate-metal. The device is finalized by depositing a S1813 resist spacer, formation of via holes and metal contacts.

#### Results

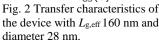

Transfer characteristics of a device with a total gate length ( $L_{\rm g}$ ) of 260 nm (the gate length without contact overlap,  $L_{\rm g,eff}$ , 160 nm) and channel diameter of 28 nm is shown in fig. 2. The device has a  $g_{\rm m}=1.4$  mS/ $\mu$ m and SS=85 mV/dec,

corresponding to the highest Q-value ( $g_{\rm m}/SS=16$ ) and  $I_{\rm on}$  (330  $\mu A/\mu m$ ) at  $I_{\rm off}$  100 nA/ $\mu m$  ( $V_{\rm D}=0.5$  V), reported for vertical MOSFETs. Furthermore, this is the first demonstration of a non-planar, III-V MOSFET on Si achieving  $I_{\rm off}=1$  nA/ $\mu m$ . The output characteristics of the same device, fig. 3, shows good saturation and on-resistance ( $R_{\rm on}$ ) of 690  $\Omega \mu m$ . The device has the same SS at  $V_{\rm D}=50$  mV and  $V_{\rm D}=500$  mV, as shown in fig. 4. The device also shows good electrostatics by having DIBL = 88 mV/V at 1  $\mu A/\mu m$ .

Fig. 5 shows transfer characteristics of a device with a diameter of 35 nm and effective  $L_{\rm g}=145$  nm. The device has SS=68 mV/dec and  $g_{\rm m}=0.58$  mS/ $\mu$ m. The MOSFET in fig. 5 has good  $I_{\rm on}$  at  $I_{\rm off}$  1 nA/ $\mu$ m due to the low SS, showing  $I_{\rm on}$  170  $\mu$ A/ $\mu$ m and 88  $\mu$ A/ $\mu$ m at  $I_{\rm off}$  100 nA/ $\mu$ m and 1 nA/ $\mu$ m, respectively. Fig. 6 shows the transfer characteristics of a device with diameter 24 nm and  $L_{\rm g,eff}=130$  nm at  $V_{\rm D}$  between 0.3 V and 0.8 V. The device has  $I_{\rm off}$  below 100 nA/ $\mu$ m at all measured  $V_{\rm D}$  while  $I_{\rm on}$  increases as a function of  $V_{\rm D}$ .

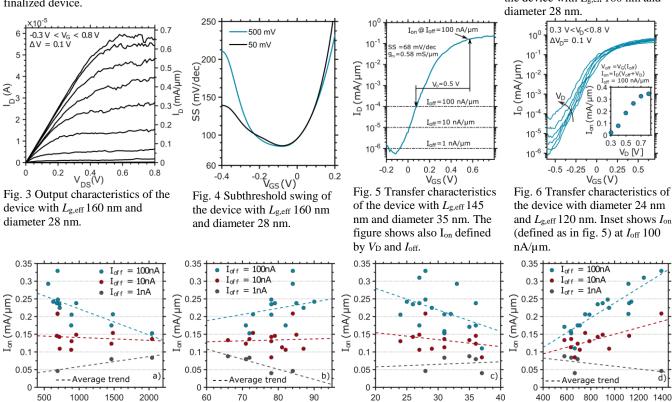

Fig. 7 (a)-(d) show  $I_{\rm on}$  at different  $I_{\rm offs}$  (1, 10, and 100 nA/ $\mu$ m, respectively) for 18 devices fabricated on the same sample plotted versus  $R_{\rm on}$  (a), SS (b), diameter (c), and  $g_{\rm m}$  (d). The statistics demonstrate that  $I_{\rm on}$  at  $I_{\rm off}$  1 nA/ $\mu$ m is limited by SS, hence limited improvements are seen with improved on-state metrics. In contrast,  $I_{\rm on}$  at  $I_{\rm off}$  100 nA/ $\mu$ m is limited by on-state metrics, hence clear improvements are observed with improved  $R_{\rm on}$  and  $g_{\rm m}$ .

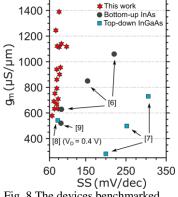

Table 1 summarizes the two most significant devices in the data set, one with the highest  $I_{\rm on}$  and Q-value and one with the lowest SS. Fig. 8 benchmarks the devices versus state-of-the-art vertical MOSFETs. A clear improvement in  $g_{\rm m}/SS$  is demonstrated. Fig. 9 benchmarks  $I_{\rm on}$  of the best devices versus the best III-V MOSFETs demonstrated. Our devices show clear improvement compared to vertical MOSFETs, although state-of-the-art planar/lateral MOSFETs still have higher  $I_{\rm on}$ . This is mainly due to the high contact resistance of the vertical devices.

# **Conclusions**

We have fabricated vertical heterojunction InAs/InGaAs MOSFETs. We have shown a device with  $g_m=1.4$  mS/ $\mu m$  and SS = 85 mV/dec. The device has  $I_{on}$  330  $\mu A/\mu m$  and 46  $\mu A/\mu m$  at  $I_{off}$  100 nA/ $\mu m$  and 1 nA/ $\mu m$  (V $_D$ =0.5), respectively. Furthermore, we have shown a device with  $g_m=0.58$  mS/ $\mu m$ , SS = 68 mV/dec and  $I_{on}$  = 88  $\mu A/\mu m$  at  $I_{off}$  = 1 nA/ $\mu m$ .

This work was supported in part by the Swedish Research Council, in part by the Knut and Alice Wallenberg Foundation, in part by the Swedish Foundation for Strategic Research and in part by the European Union H2020 program INSIGHT (Grant Agreement No. 688784)

[1] D. Yakimets, et al., TED, 62, pp. 1433, (2015). [2] C. B. Zota, et al., VLSI, (2016). [3] S.Lee, et al, VLSI, (2014). [4] C.Y. Huang, et al., IEDM, pp. 25.4.1-25.4.4, (2014) [5] J. Mo, et al., APL 105, pp. 033516 (2014) [6] M. Berg, et al., IEDM, pp. 31.2.1-31.2.4, (2015) [7] X. Zhao, et al., IEDM. pp. 28.4.1-28.4.4, (2013) [8] S. Ramesh, et al., VLSI, (2016) [9] C. Thelander, et al., EDL, 29, pp. 206, (2008)

Fig. 1 Illustrations of the process flow (a), cross-section schematic of the device after growth (b), cross-sectional schematic of the finalized device (c) and scanning electron micrograph of the finalized device.

Fig. 7  $I_{\text{on}}$  of 18 devices at different  $I_{\text{offs}}$  (1, 10 and 100 nA/ $\mu$ m) and  $V_{\text{D}}$ =0.5 V plotted versus  $R_{\text{on}}$  (a), SS (b), diameter (c) and  $g_{\text{m}}$  (d). The statistics shows that  $I_{\text{on}}$  at  $I_{\text{off}}$  100 nA/ $\mu$ m is mostly dependent on  $R_{\text{on}}$  and diameter, while  $I_{\text{on}}$  at  $I_{\text{off}}$  1 nA/ $\mu$ m is mostly dependent on SS. The dashed lines describe the average trend to guide the eye.

SS (mV/dec)

Table 1 Metrics of two devices, one with the best Q-value and one with the best SS.

$R_{on}(\Omega \mu m)$

| Metric (V <sub>d</sub> =0.5V)            | High Ion device | Low SS device |

|------------------------------------------|-----------------|---------------|

| SS                                       | 85 mV/dec       | 68 mV/dec     |

| g <sub>m</sub>                           | 1.40 mS/µm      | 0.58 mS/μm    |

| I <sub>on</sub> at I <sub>off</sub> =100 | 330 μA/μm       | 170 μA/μm     |

| nA/μm                                    | , .             |               |

| I <sub>on</sub> at I <sub>off</sub> =1   | 46 μA/μm        | 88 μA/μm      |

| nA/μm                                    |                 |               |

| diameter                                 | 28 nm           | 35 nm         |

| L <sub>g,eff</sub>                       | 160 nm          | 145 nm        |

diameter (nm)

Fig. 8 The devices benchmarked versus the state-of-the-art vertical III-V MOSFETs.

0.6 0.5 1 This work Vertical 0.4 1 Off = 100 nA/µm VD = 0.5 V 1 Off = 1 nA/µm VD = 0.5 V 1 Off = 1 nA/µm VD = 0.5 V 1 Off = 1 nA/µm VD = 0.5 V

Fig. 9 The best devices benchmarked against state-ofthe-art planar, lateral and vertical III-V MOSFETs.