#### **III-V Nanowires for High-Speed Electronics**

Lindelöw, Fredrik

2020

Document Version: Publisher's PDF, also known as Version of record

Link to publication

Citation for published version (APA):

Lindelöw, F. (2020). III-V Nanowire's for High-Speed Electronics (Series of licentiate and doctoral theses, 1654-790X ed.). Lund University.

Total number of authors:

Creative Commons License: Unspecified

General rights

Unless other specific re-use rights are stated the following general rights apply:

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

• Users may download and print one copy of any publication from the public portal for the purpose of private study

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal

Read more about Creative commons licenses: https://creativecommons.org/licenses/

Take down policy

If you believe that this document breaches copyright please contact us providing details, and we will remove access to the work immediately and investigate your claim.

# III-V Nanowires for High-Speed Electronics

Fredrik Lindelöw

Academic dissertation by due permission of the Faculty of Engineering at Lund University, will be publicly defended on Wednesday May 20<sup>th</sup> 2020 at 09.15 in lecture hall E:1406, Ole Römers väg 3, Lund, Sweden for the degree of Doctor of Philosophy in Electrical Engineering.

Faculty opponent

Dr. Nadine Collaert, IMEC, Leuven, Belgium

| Organization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Document name DOCTORAL THESIS                   |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|--|--|--|

| LUND UNIVERSITY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Sponsoring organizations:                       |  |  |  |

| Department of Electical and Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Swedish Foundation for Strategic Research (SSF) |  |  |  |

| Technology                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | The Swedish Research Council (VR)               |  |  |  |

| Ole Römers Väg 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Knut and Alice Wallenberg Foundation            |  |  |  |

| 223 63 Lunds universitet Sweden                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | European Union H2020 program INSIGHT            |  |  |  |

| Author: Fredrik Lindelöw                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Date of issue: May 2020                         |  |  |  |

| THE STATE OF THE VALUE OF THE STATE OF THE S |                                                 |  |  |  |

Title and subtitle: III-V Nanowires for High-Speed Electronics

#### Abstract

III-V compound materials have long been used in RF applications in high-electron-mobilitytransistors (HEMTs) and bipolar-junction-transistors (BJTs). Now, III-V is also being viewed as a material candidate for replacing silicon in the n-channel in CMOS processes for increased drive currents and reduced power consumption in future nodes. Another alternative to increase the drive current is to use nanowire channels, where the increased electrostatic control can be utilized for scaling the gate length even further. In this thesis, we have characterized III-V nanowires with Hallmeasurements to quantify the carrier concentration and optimize growth parameters. We have fabricated nanowire transistors for both digital and analog applications. Digital transistors made of a single nanowire show state-of-the art performance with low subthreshold slope and simultaneously high transconductance and high on-current. For RF applications, the nanowire technology faces several challenges, mainly due to its inherent higher parasitic capacitance since the filling factor is less than 1. To adapt the DC processing scheme to RF measurements, we have implemented T-gates, two-finger devices, 100 nanowires in parallel with tight pitch and we have developed novel spacer schemes with capacitances almost as low as recessed HEMT devices. These schemes consists of for instance modulation doped InP spacers as well as self-aligned air-spacers. To make the RF nanowire MOSFETs even more competitive, the transoncductance of RF devices needs to be optimized to match that of DC devices.

| Key words Nanowire, MOSFET, Hall, DC, RF       |                                               |                                  |  |  |

|------------------------------------------------|-----------------------------------------------|----------------------------------|--|--|

| Classification system and/or index             | sification system and/or index terms (if any) |                                  |  |  |

| Supplementary bibliographical information      |                                               | ISBN (digital) 978-91-7895-511-4 |  |  |

| ISSN and key title Series of licentiate and do | ctoral theses, 1654-790X; No. 129             | ISBN (print) 978-91-7895-510-7   |  |  |

| Recipient's notes                              | Number of pages 130                           | Price                            |  |  |

|                                                | Security classification                       |                                  |  |  |

I, the undersigned, being the copyright owner of the abstract of the above-mentioned dissertation, hereby grant to all reference sources permission to publish and disseminate the abstract of the above-mentioned dissertation.

Signature Fred Lower Date: 2020-04-21

# III-V Nanowires for High-Speed Electronics

#### Fredrik Lindelöw

Doctoral Thesis

Electrical Engineering

Lund, May 2020

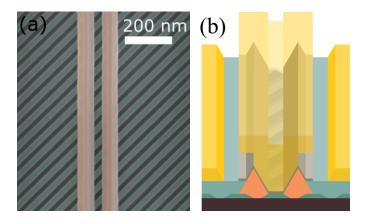

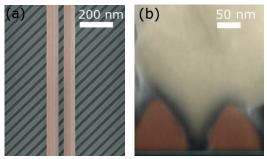

Coverphoto showing 100 lateral nanowires with two  $\Lambda$ -ridge spacers, illustrated by Linus Kandefelt and Fredrik Lindelöw

Fredrik Lindelöw Department of Electrical and Information Technology Lund University Ole Römers väg 3, 223 63 Lund, Sweden

Series of licentiate and doctoral theses ISSN 1654-790X; No. 129 ISBN (digital) 978-91-7895-511-4 ISBN (print) 978-91-7895-510-7

© 2020 Fredrik Lindelöw Printed by Tryckeriet i E-huset, Lund University, Lund, Sweden

No part of this thesis may be reproduced or transmitted in any form or by any means without written permission from the author. Distribution of the original thesis in full, however, is permitted without any restriction.

## **Abstract**

III-V compound materials have long been used in RF applications in high-electronmobility-transistors (HEMTs) and bipolar-junction-transistors (BJTs). Now, III-V is also being viewed as a material candidate for replacing silicon in the n-channel in CMOS processes for increased drive currents and reduced power consumption in future nodes. Another alternative to increase the drive current is to use nanowire channels, where the increased electrostatic control can be utilized for scaling the gate length even further. In this thesis, we have characterized III-V nanowires with Hall-measurements to quantify the carrier concentration and optimize growth parameters. We have fabricated nanowire transistors for both digital and analog applications. Digital transistors made of a single nanowire show state-of-the art subthreshold performance with low slope and simultaneously high transconductance and high on-current. For RF applications, the nanowire technology faces several challenges, mainly due to its inherent higher parasitic capacitance since the filling factor is less than 1. To adapt the DC processing scheme to RF measurements, we have implemented T-gates, two-finger devices, 100 nanowires in parallel with tight pitch and we have developed novel spacer schemes with capacitances almost as low as recessed HEMT devices. These schemes consists of for instance modulation doped InP spacers as well as self-aligned air-spacers. To make the RF nanowire MOSFETs even more competitive, the transoncductance of RF devices needs to be optimized to match that of DC devices.

# Populärvetenskaplig sammanfattning

Mycket av de saker som vi tar för givet i vårt moderna samhälle, så som datorer, smarta mobiltelefoner och internet har möjliggjorts av den enorma utvecklingen av transistorer under de senaste 70 åren. Den första transistorn tillverkades i halvledarmaterialet germanium, men sedan dess har mycket av utvecklingen av transistorer gjorts i kisel. Kisel visade sig vara ett väldigt lämpligt material att använda på grund av dess goda ledningsförmåga samt dess elektriskt isolerande oxid, SiO<sub>2</sub>. Transistorer kan användas både för att stänga av och på strömmar, för att representera 0:or och 1:or i digitala kretsar samt som en förstärkare av signaler i analoga kretsar. Ett exempel på en tidig analog krets var transistorradion som revolutionerade lyssnandet av musik innan modernare portabla koncept var utvecklade. Det visade sig att genom att göra transistorerna mindre och mindre så kunde beräkningarna i datorer utföras snabbare och med mindre energiförbrukning. Denna utveckling har beskrivits av Moores lag där antalet transistorer per yta på ett kretskort dubblas vartannat år. Idag har dock kurvan börjat avta på grund av att energin per ytenhet har blivit enormt hög och det har blivit betydligt mer komplext att tillverka de minsta beståndsdelarna i transistorn som är långt mindre än ljusets våglängd. Ett annat sätt att förbättra transistorn utan att nödvändigtvis göra den mindre är att använda nanotrådar samt andra material än kisel. I halvledarmaterialet indium-gallium-arsenid kan elektronerna färdas snabbare än i kisel, dessutom med en lägre pålagd elektrisk spänning. Genom att minska spänningen, alternativt behålla samma som för kisel, kan antingen energiförbrukningen minskas eller prestandan förbättras.

I denna avhandling har vi studerat hur man kan förbättra nanotrådstransistorer gjorda av InGaAs både för digitala och analoga applikationer, där storleken på nanotrådarna är ungefär i samma storlek som ett coronavirus. Att tillverka en transistor påminner om konsten att laga mat. Det finns säkra recept att följa steg för steg vilket man vet kommer att ge en god måltid. Men vill man skapa något nytt och bättre så måste man våga experimentera och komma på nya tekniker. Ifall resultatet

blir dåligt, får man kasta sin kreation i komposten för att ta nya tag och komma på bättre lösningar. För att förbättra transistorns prestanda har vi utvecklat en teknik där atomernas förmåga att växa i speciella kristallriktningar har utnyttjats, lite liknande hur atomerna i natriumklorid bildar kristaller i flingsalt. Genom att utnyttja olika kristall-riktningar kan transistorns prestanda optimeras och kapacitanser som saktar ner transistorn kan minskas. Just minskning av kapacitanser har varit ett stort fokusområde för avhandlingen, där många nya processtekniker har föreslagits, varav vissa gav bland de lägsta kapacitanserna av alla transistorteknologier i världen. Transistorerna har visat prestanda nära de teoretiska fysikaliska gränserna, och i vissa avseenden presterar de till och med bättre än kisel-transistorer tillverkade av stora miljard-företag. Arbetet kan bli betydelsefullt för framtida utveckling av energieffektiva och prestandakrävande applikationer inom 5G, bilradar, internet of things samt gest-igenkänning.

# Acknowledgments

There have been so many people involved in making this thesis a reality. First, I would like to thank my main supervisor Erik Lind. Erik, it has been a pleasure working with you during these years. We have shared so many great (and maybe not so great) ideas. Your door has always been open and you have guided me through the semiconductor technologies with great enthusiasm. Lars-Erik, you have been a great group leader and shown me how to set-up great research environments and how to initiate collaborations and in giving a broader view on industry and education in general. Mattias, thanks for all the inspiration and for guiding me through all aspects of III-V technology, from atoms to systems.

Cezar, a big thanks for introducing me to the lateral nanowire processing and characterisation, my work wouldn't have been possible without all your efforts. Navya and Lasse, thanks for the countless hours you have spent working in the lab to help our common projects. Stefan, thanks for always being there helping out with processing and setting up RF measurements, and introducing me to all aspects regarding circuits. Anna and Josefine, thanks for help developing the transistor technology, and for your great patience and perseverance. Thanks to Olof and Magnus for introducing me to device technology and to the Lund Nano Lab, which made it possible for me to pursue my career in academia.

Olli-Pekka, Adam, Markus, Sebastian, Elvedin, Karl-Magnus, Lars, Johannes, Aein, Guntrade, Jun, Martin, Kristofer, Patrik, Saketh, Heera, Robin, Anton, Gautham, Zhongyunshen and Abinaya, you have made these years a pleasure and make working with all of you has been a joy.

To all the staff in Lund Nano Lab, thanks for constantly improving, and always contributing to a great atmosphere. Håkan, George and Elsie, you have made all my hours in the clean room so much nicer. You always come with a smile on your faces, providing a joke whenever it's needed.

I would like to thank all personnel at EIT, especially Daniel, Elisabeth, Anne and Linda for always helping out when I am lost.

Mum and dad, thanks for all your support and love. Thanks for always taking the time and answering my questions about how things worked growing up. Eva, thanks for being a great sister and friend in life and for helping your younger brother through school in younger years!

I would like to thank my friends and extended family for always caring and providing good times and laughter. Linus, thank you so much for the help with cover photo and images.

My daughter Alma, you are an inspiration in your daily quest to understand how the world works, and you make time fly. Louise, you are the love of my life and my true inspiration, both in personal life as well as in research. You encourage me to try new things and if it wasn't for you, I wouldn't have had the courage to start my PhD in the first place.

# List of Papers

This thesis is based on the following six papers which are included at the back of the thesis.

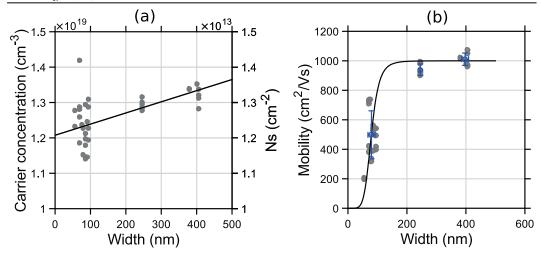

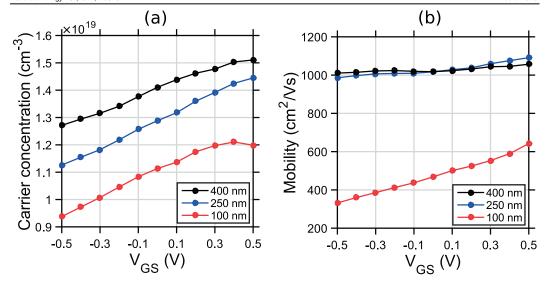

- I <u>F. Lindelöw</u>, C. B. Zota, E. Lind, "Gated Hall effect measurements on selectively grown InGaAs nanowires", *Nanotechnology*, 2017

- I designed the Hall bar structures, performed all fabrication steps except growth, did both Hall measurements and resistivity measurements and analyzed the measured data. Finally, I also wrote the paper.

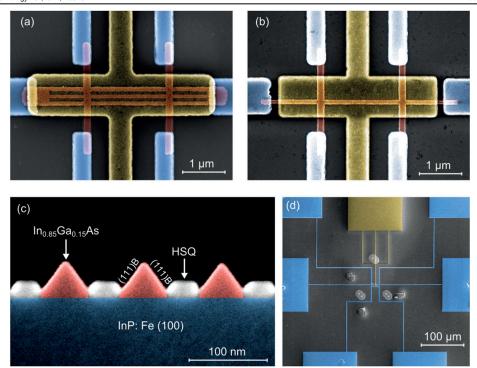

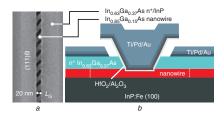

- II <u>F. Lindelöw</u>, N. Sri Garigapati, L. Södergren, M. Borg, E. Lind, "III-V nanowire MOSFETS with novel self-limiting Λ-ridge spacers for RF applications", *Semiconductor science and technology*, 2020

- I developed the novel process of  $\Lambda$ -ridge spacers including fabrication and validation of all involving process steps. I cofabricated the actual device that was published and were involved both in DC and RF measurements. I did the data analysis and wrote the paper.

- III C. B. Zota, <u>F. Lindelöw</u>, L.-E. Wernersson and E. Lind, "High-frequency InGaAs tri-gate MOSFETs with f<sub>max</sub> of 400 GHz", *Electronic Letters*, 2016

- I collaborated in developing processing scheme with a focus on spacer implementation, and co-fabricated devices, as well as contributed to DC and RF measurements and data analysis.

- IV C. B. Zota, <u>F. Lindelöw</u>, L.-E. Wernersson and E. Lind, "InGaAs trigate MOSFETs with record on-current", *2016 IEEE Int. Electron Devices Meetings (IEDM)*, 2016

- I collaborated in device processing, especially in lithography, deposition and digital etching. I also collaborated in electrical characterization and data analysis.

- V C. B. Zota, <u>F. Lindelöw</u>, L.-E. Wernersson and E. Lind, "InGaAs nanowire MOSFETs with  $I_{ON}$ = 555  $\mu$ A/ $\mu$ m at  $I_{OFF}$  = 100 nA/ $\mu$ m and  $V_{DD}$  = 0.5 V", *Symposium on Very Large Scale Integrated Circuits and Technology (VLSI)*", 2016

- I collaborated in developing the process and in the processing of the device itself, especially in digital etching and device passivation. I also collaborated in electrical characterization and data analysis.

- VI <u>F. Lindelöw</u>, M. Heurlin, G. Otnes, V Dagyte, D. Lindgren, O. Hultin, K. Storm, L. Samuelson, M. Borgström, "Doping evaluation of InP nanowires for tandem junction solar cells", *Nanotechnology*, 2016

I performed all device processing of the Hall-contacts on the nanowires. I performed the Hall measurements and resistivity measurements. I did the majority of the data analysis and I wrote the paper.

The following papers are not included in the thesis, but summarize related work that I have contributed to.

- VII <u>F. Lindelöw</u>, C. B. Zota, E. Lind, "Low capacitance InGaAs nanowire MOSFETs for high-frequency applications", *Compound semiconductor week*, 2018

- VIII <u>F. Lindelöw</u>, C. B. Zota, L.-E. Wernersson and E. Lind, "High transconductance InGaAs nanowire MOSFETs", *GigaHertz*, 2016

- IX L. Ohlsson, <u>F. Lindelöw</u>, C. B. Zota, M. Ohlrogge, T. Merkle, L.-E. Wernersson, E. Lind, "First InGaAs lateral nanowire MOSFET RF noise measurements and model", 75<sup>th</sup> Annual Device Research Conference (DRC), 2017

- X S. Andric, L. Ohlsson Fhager, <u>F. Lindelöw</u>, O.-P. Kilpi, L.-E. Wernersson, "Low-temperature back-end-of-line technology compatible with III-V nanowire MOSFETs", *Journal of Vacuum Science & Technology B*, 2019

- XI C. B. Zota, <u>F. Lindelöw</u>, L.-E. Wernersson and E. Lind, "Highperformance field-effect transistors using selectively grown lateral InGaAs nanowires", *Nanowire week*, 2017

- XII T. Haggren, G. Otnes, R. Mourao, V. Dagyte, O. Hultin, <u>F. Lindelöw</u>, M. Borgström, L. Samuelson, "InP nanowire p-type doping via zinc indiffusion", *Journal of crystal growth*, , 2016

- XIII <u>F. Lindelöw</u>, L. Södergren, E. Lind,, "III-V nanowire MOSFETs for high-frequency applications", IVC 21, 2019

# Abbreviations and Symbols

#### **ABBREVIATIONS**

(NH4)<sub>2</sub>S diammonium sulphide

Al aluminum

Al<sub>2</sub>O<sub>3</sub> aluminum oxide

ALD atomic layer deposition

Au gold

**BOE** buffered oxide etch

BCB benzocyclobutene

CMOS complementary metal-oxide-semiconductor

**DOS** density of states

**DUT** device under test

**EOT** effective oxide thickness

FDSOI fully depleted silicon on insulator

FinFET fin field-effect transistor

FET field-effect transistor

**GAA** gate-all-around

GaAs gallium arsenide

H<sub>2</sub>O<sub>2</sub> hydrogen peroxide

H<sub>3</sub>PO<sub>4</sub> phosphoric acid

HCl hydrochloric acid

**HEMT** high-electron-mobility-transistor

HF hydrofluoric acid

HfO<sub>2</sub> hafnium oxide

**HSQ** hydrogen silsesquioxane

InGaAs indium gallium arsenide

InP indium phosphide

**LED** light emitting diode

MAG maximum available gain

MSG maximum stable gain

MOCVD metal organic chemical vapor deposition

MOVPE metal organic vapor phase epitaxy

MOSFET metal-oxide-semiconductor field-effect transistor

Ni nickel

Pd palladium

**PMMA** poly(methyl methacrylate)

QCL quantum capacitance limit

RF radio-frequency

**S.I.** semi-insulating

**S/D** source and drain

Si silicon

SiO<sub>2</sub> silicon dioxide

Sn tin

SS inverse subthreshold slope

TMAH tetramethylammonium hydroxide

Ti titanium

**TiN** titanium nitride

VLS vapor-liquid-solid

VNA vector network analyzer

#### **GREEK SYMBOLS**

$\mu$  mobility

$\lambda$  mean free path

$\kappa$  dielectric constant

$\epsilon(0)$  top of the barrier energy

$\rho$  resistivity

$\sigma$  conductivity

#### **LATIN SYMBOLS**

Cc charge centroid capacitance

Cox oxide capacitance

$C_Q$  quantum capacitance

$D_n$  diffusion constant

$E_F$  Fermi level

| $g_d$ output conductance          |

|-----------------------------------|

| $g_m$ transconductance            |

|                                   |

| <i>Ioff</i> off-state current     |

| Ion on-state current              |

|                                   |

| k wavevector                      |

| k stability factor                |

|                                   |

| $L_{g}$ gate length               |

| m* effective electron mass        |

| m effective effection mass        |

| n carrier density                 |

|                                   |

| q electric charge                 |

|                                   |

| $R_g$ gate resistance             |

| Ron On-resistance                 |

|                                   |

| $T_L$ crystal lattice temperature |

|                                   |

| $V_{DD}$ drive bias               |

| $V_T$ threshold voltage           |

|                                   |

$f_{max}$  maximum oscillation frequency

$f_T$  cut-off frequency

# Table of Contents

| Abs  | stract. |                                 | v   |

|------|---------|---------------------------------|-----|

| Pop  | ulärvo  | etenskaplig sammanfattning      | vii |

| Ack  | knowle  | edgments                        | ix  |

| List | t of Pa | pers                            | xi  |

| Abl  | breviat | tions and Symbols               | xiv |

|      |         | Contents                        |     |

| 1    |         | kground                         |     |

|      | 1.1     | Optical applications            |     |

| 2    | Tra     | nnsistor theory                 | 4   |

|      | 2.1     | Transistor operation            | 4   |

|      | 2.2     | Classical transport             | 5   |

|      | 2.3     | Channel capacitance             | 6   |

|      | 2.4     | Ballistic transport             | 7   |

|      | 2.5     | Two-port measurements           | 10  |

|      | 2.6     | Small signal modeling           | 11  |

|      | 2.7     | RF metrics                      | 12  |

|      | 2.8     | Calibration and de-embedding.   | 15  |

| 3    | Sen     | niconductor crystals and doping | 16  |

|      | 3.1     | Doping                          |     |

|      |         | 3.1.1 Hall measurements         |     |

|      | 2.2     | 3.1.2 Modulation doping         |     |

|      | 3.2     | Ž                               |     |

| 4    |         | transistors                     |     |

|      | 4.1     | HEMTs                           | _   |

|      | 4.2     | MOSHEMTs                        |     |

|      | 4.3     | Planar RF CMOS                  |     |

|      | 4.4     | FDSOI                           | 24  |

|    | 4.5  | RF FinFETs                                                  | 25 |

|----|------|-------------------------------------------------------------|----|

|    | 4.6  | RF Nanowire FETs                                            | 26 |

|    | 4.7  | Spacers                                                     | 26 |

|    |      | 4.7.1 Silicon oxide spacers                                 | 28 |

|    |      | 4.7.2 Silicon nitride spacers                               |    |

|    |      | 4.7.3 Air spacers                                           |    |

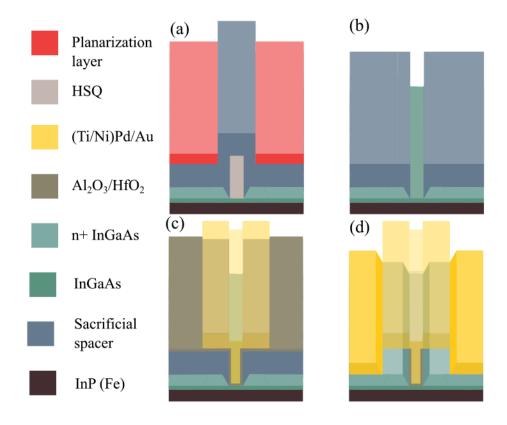

| 5  | Late | eral nanowire transistor fabrication                        | 29 |

|    | 5.1  | Selective area growth and resist masking                    | 29 |

|    | 5.2  | Regrowth of highly doped contacts                           | 30 |

|    | 5.3  | Mesa etching                                                | 30 |

|    | 5.4  | Source and drain metallization                              | 31 |

|    | 5.5  | Insulating gate oxide and gate contact                      | 31 |

|    | 5.6  | High-frequency adapted processing schemes                   | 33 |

|    |      | 5.6.1 Generation I                                          |    |

|    |      | 5.6.2 Generation II                                         |    |

|    |      | 5.6.3 Generation III                                        |    |

|    |      | 5.6.4 Generation IV                                         |    |

|    |      | 5.6.5 Summary of RF process flows                           |    |

| 6  | III- | V device characterization                                   | 40 |

|    | 6.1  | Hall measurements                                           | 40 |

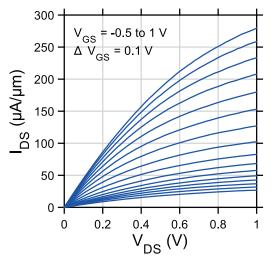

|    | 6.2  | III-V nanowire MOSFETs for low-power digital applications   | 43 |

|    | 6.3  | MOSFETs for high-frequency applications                     | 44 |

|    | 6.4  | Benchmarking of RF performance                              | 48 |

|    | 6.5  | Initial circuit efforts                                     | 51 |

| 7  | Con  | clusions and outlook                                        | 53 |

| Α. | Apr  | endix A                                                     | 55 |

|    |      | Lateral nanowire RF process                                 |    |

|    | 11.1 | A.1.1. Nanowire masking and growth                          |    |

|    |      | A.1.2. HSQ dummy gate mask exposure and contact regrowth    |    |

|    |      | A.1.3. Sacrificial spacer deposition and dummy gate removal |    |

|    |      | A.1.4. Gate dielectric and gate metal deposition            |    |

|    |      | A.1.5. Sacrificial spacer removal and device isolation      |    |

|    |      | A.1.6. Source – drain contacts deposition                   |    |

|    |      | A.1.7 Pad deposition.                                       |    |

|    |      | 7.1.7 I ad deposition                                       |    |

# 1 Background

In 1947, Bell laboratories invented the first point-contact transistor and it was made in the semiconducting material germanium [1]. The transistor allowed a very small signal to control a much larger current flow, effectively turning the transistor on and off as a switch. About a decade later, in 1959, the first experimental demonstration of a metal-organic-semiconductor field-effect transistor (MOSFET) made out of silicon was fabricated. It turned out that the native oxide that naturally forms on silicon, SiO<sub>2</sub>, was a good electrical insulator to use underneath the gate contact in order to achieve small gate leakage currents but also a high capacitive coupling between the gate electrode and the channel. Silicon is also a material with a high density of states and a good electron mobility, which all together made the realization of well performing transistors. In parallel to the evolution of the silicon MOSFET, III-V semiconductor materials were researched due to their direct band gap, enabling optical semiconductor devices and due to the superior electron mobilities. However, these III-V materials do not have as good native oxide as silicon [2], and their superior electron velocity was primarily used for oxide-less high-electron-mobility-transistors (HEMTs) [3] and bipolar-junction-transistors [4]. As the silicon transistor size was scaled down according to the laws of Dennard scaling [5], the speed of the transistor also increased, one reason being a lower resistance in the shorter channel. This allowed for smaller, faster and more energyefficient computing for every new node, which Gordon Moore famously predicted in what is called Moore's law; the transistor density approximately doubles every two years [6]. In order to scale the MOSFET transistor even further, the thickness of the insulating oxide barrier had to be thinner as well to maintain a good electrostatic control of the channel potential. However, this made the gate leakage increase and therefore, research of different oxides than the native SiO2 was conducted and eventually, the SiO<sub>2</sub> was replaced with HfO<sub>2</sub> in Intel's 45 nm node, where the capacitive gate coupling could be high while having a thicker oxide due to the higher  $\kappa$ -value[7]. This eliminated one of the intrinsic benefits that silicon had over III-V materials, as HfO<sub>2</sub> and Al<sub>2</sub>O<sub>3</sub> have been shown to perform well on III-V semiconductors when self-cleaning pulses in atomic layer deposition (ALD) is used

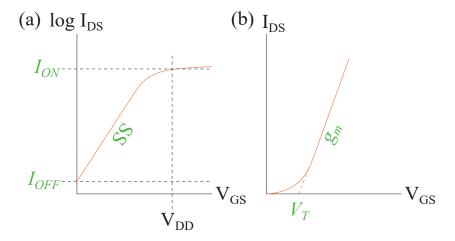

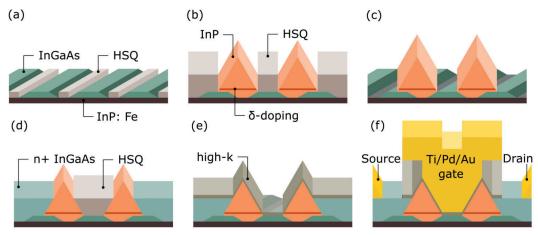

**Figure 1.1:** Schematic illustrations of three important device architectures, planar MOSFET, FinFETs and nanowire MOSFET also called Tri-gate or nanosheet architecture that has been used in this thesis.

to remove native oxide[8-10]. Similar scaling problems also arose for III-V HEMTs, where the scaled devices with thin semiconductor barriers underneath the gate also gives increased gate leakage [11]. Therefore, MOSHEMTs with high-k barriers on top of In<sub>x</sub>Ga<sub>1-x</sub>As channels are currently researched, with expected increase in drive currents and high-frequency performance[12]. However, the reliability of high-k oxides on III-V materials is still a challenge and needs to be solved before III-V transistors with gate oxide will be implemented in commercial devices. After the invention of high-k MOSFETs, another important technology shift was the move to three-dimensional channels rather than planar two-dimensional in high-performance digital circuits [13]. Three dimensional channel transistors as FinFETs and nanowire transistors, as seen in figure 1.1, give a performance boost from increased electrostatic control due to that the gate can control the potential in the channel from multiple sides, reducing the detrimental short channel effects.

The evolution of silicon transistors has in many ways been driven by the digital circuits, where the demand of digital chips have increased many fold since the first silicon MOSFET was invented. However, the demand for RF devices is also large and it is expected to increase as we are transmitting ever more data wirelessly in the modern society. From the 2G and 3G technology, which used only a few frequency bands to transmit signals, to the modern 4G technology which can use up to 40 bands, the amount of analog transistors in a smartphone is increasing and requirements on well-performing amplifiers are high [14]. Future applications in 5G where massive multiple-input multiple-output applications are likely to be implemented, as well as radar applications in the automotive industry, will make the

demand of RF transistors increase even further [15]. Generally, low-noise-amplifiers and power amplifiers in smartphones have been based on GaAs or InP technology, while devices for routing of analog signals, such as switches, have been made in silicon. Chips where analog and digital functions can be combined is expected to decrease delay and energy consumption. There have been a lot of research recently by for instance IBM Zurich and IMEC on how to integrate different semiconductors on silicon to combine for example standard complementary-metal-oxide-semiconductor (CMOS) technology with III-V to be able to take advantage of the improved speed or optical capabilities [16-18].

Up until now, the industry have made many studies on logic performance of silicon nanowires for scaled process nodes, but the RF capabilities are less researched. The work in this thesis have been aimed at improving the field of III-V nanowires with special emphasis on nanowire MOSFETs for high-frequency applications, where spacer technologies for reducing the inherently higher parasitic capacitances has been the main focus.

## 1.1 Optical applications

III-V materials have been used for opto-electronics due to their direct band gap and favorable electron mobility. The direct band gap allows for development of lightemitting diodes (LEDs) and lasers which has led to significant improvements in growth and characterization of III-V semiconductors [19, 20]. GaAs and InP also have a band gap near the optimum for a single junction solar cell for maximum energy conversion [21]. The possibility to fine-tune band gap and lattice constant with composition of ternary III-V compounds, opens up the possibility to do tandem junction solar cells with several different band gaps to absorb more of the incoming energy from the sun. Recently, researchers at NREL demonstrated a GaAs based 6 junction solar cell with world record efficiency of 47.1% under 143 suns concentrated light [22]. The drawback however, is the increased price for III-V semiconductors compared to silicon, especially in such large area applications as solar cells. Research to limit the amount of III-V material needed is currently ongoing by using nanowires with substrate reuse, or by using nanowires grown with aerotaxy without a substrate [23, 24]. If the nanowire array is engineered so that the diameter and pitch of the nanowires are similar to the wavelength of light, the nanowire can actually absorb a larger portion of the incoming light than its own cross section [25].

# 2 Transistor theory

In this section, the most important aspects of electrical transport and characterization, with a focus on transistors, will be presented.

### 2.1 Transistor operation

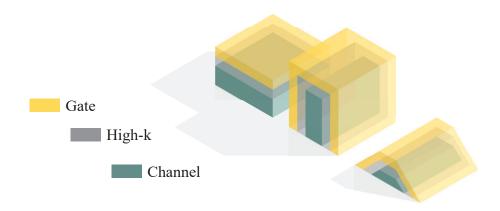

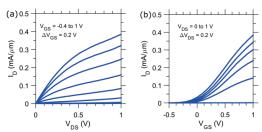

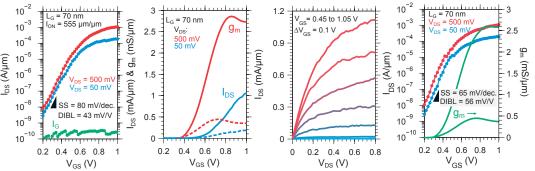

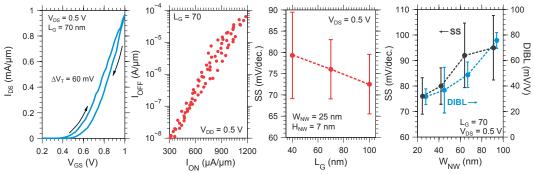

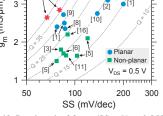

A transistor is a three-terminal device, where a voltage bias is applied between source, gate and drain contacts enabling a current to flow between source and drain. The third terminal, the gate contact, turns this current on or off with applied gate bias. The transistor can either operate as a switch or as an amplifier of applied signals. For a switch, which for instance is used in CMOS technologies that perform the calculations in almost all computers and smartphones, the most important metrics regarding the off-state are off-current  $(I_{OFF})$ , inverse subthreshold slope (SS), drain-induced barrier lowering (DIBL) and threshold voltage  $(V_T)$  while for the on-state important metrics are transconductance  $(g_m)$ , output conductance  $(g_d)$ and on-resistance  $(R_{ON})$  and on-current  $(I_{ON})$ . Transfer characteristics for off-state and on-state can be seen in figure 2.1 with logarithmic and linear scale respectively. For a transistor that is used as an amplifier, the off-state is not as important, since the transistor will in general operate in the on-state. The most important metrics for a transistor in an analog application is all metrics regarding on-state as mentioned before, but also gate capacitance and gate resistance, as well as transistor gain. Compared to planar silicon transistors, III-V nanowire structures can in theory enable steeper inverse subthreshold slope and higher drive currents at the cost of increased parasitic capacitances.

**Figure 2.1:** Off-state(a) and on-state (b) of a MOSFET transistor with a few relevant metrics highlighted.

### 2.2 Classical transport

For semiconductor devices with large dimensions and low electric fields, and low carrier concentration, the transport through the semiconductor can be described with the classical transport of drift and diffusion[26].

$$J = qn\mu\varepsilon + qD_{\rm n}\frac{dn}{dx}$$

(2.1)

The current originating from drift is proportional to the mobility  $\mu$ , carrier concentration n, and the applied electric field  $\epsilon$ . In general, III-V materials have a high electron mobility, since it is inversely proportional to the effective mass  $m^*$ , but a smaller intrinsic carrier concentration than silicon, due to the density of states being smaller, also due to the lower effective mass.

$$\mu = \frac{q\tau_{\rm c}}{m^*} \tag{2.2}$$

As the devices are scaled in dimensions, the applied electric fields become very large, and eventually, the electron velocity is not proportional to the applied electric

field but saturates at a finite value called velocity saturation [27]. The current originating from drift can then be rewritten, by inserting the constant  $\varepsilon_c$  which is the critical electric field

$$J = \frac{qn\mu\varepsilon}{1 + \frac{\varepsilon}{\varepsilon_c}} \tag{2.3}$$

Diffusion current is also proportional to the mobility, but more importantly to the gradient in carrier concentration in the material.

### 2.3 Channel capacitance

As transistor dimensions have been scaled over the years, the short channel effects also increased. According to Dennard scaling, in order to maintain good electrostatic control of the channel, the thickness of the insulating oxide should also decrease[5]. The surface potential at the top of the barrier in the channel is set by the difference between applied gate overdrive voltage and the voltage drop over the oxide. In order to have a high coupling between the gate and the channel, the voltage drop over the oxide should be minimized, which corresponds to an increased gate oxide capacitance according to equation (2.4)

$$C_{\rm ox} = \frac{\varepsilon_o \varepsilon_{ox}}{t_{ox}} \tag{2.4}$$

The total gate capacitance to the channel is three capacitors in series, the oxide capacitance  $C_{\rm ox}$ , the quantum capacitance  $C_{\rm q}$  and the charge centroid capacitance  $C_{\rm c}$  [28].

$$C_{\rm G} = \left(\frac{1}{C_{ox}} + \frac{1}{C_q} + \frac{1}{C_c}\right)^{-1} \tag{2.5}$$

For a two dimensional field effect transistor, the quantum capacitance can be written as

$$C_q = \frac{q^2 m^*}{\pi \hbar^2} \tag{2.6}$$

and is the effect of the limited density of states in the semiconductor, which results in accumulation of electrons in the channel. Once there are carriers inside the channel, this will in turn lead to an upward shift of the energy bands due to repulsive interactions between electrons. This can be described by another capacitance in series with the quantum capacitance, and is called charge centroid capacitance, and can be calculated by quantum mechanical perturbation theory.

$$C_c = \frac{\varepsilon_s \varepsilon_o}{0.36 t_w} \tag{2.7}$$

The quantum capacitance is not fixed for all different channel materials, but it depends on the effective mass of the electron. For a classical silicon transistor, the effective mass and quantum capacitance is relatively large and therefor the  $C_q^{-1}$  can be neglected in equation (2.5) as long as the thickness of the insulating gate oxide is not too small. This is called the MOS limit for gate capacitance. For a III-V transistor, with a very small effective mass and a scaled oxide thickness,  $C_{ox} \gg C_q$  and the term  $C_{ox}^{-1}$  can be neglected in equation (2.5). This limit is called the quantum capacitance limit (QCL) and this means that the applied gate overdrive bias would directly control the potential in the top of the barrier in the channel. In devices where  $C_{ox} \gg C_q$ , the transistor performance would not continue to improve with reduction of oxide thickness, but rather saturate at some finite value.

### 2.4 Ballistic transport

For a nanowire MOSFET with high electron mobility and very narrow dimensions, including width, height and gate length shorter than the mean free path, the transport through the channel can be modelled with 1D ballistic transistor theory. This means that the carriers are confined in two dimensions, and can only propagate in the third dimension. The analysis follows work developed by Lundstrom [29]. First, we use the effective mass approximation and assume simple parabolic band structure, where only the first sub-band is conducting.

$$\varepsilon_1(k) = \varepsilon_1(0) + \frac{\hbar^2 k^2}{2m^*} \tag{2.8}$$

Here  $\varepsilon_1(0)$  is the minimum of the bottom sub-band, also called the top of the barrier, which for a well-designed one dimensional transistor with insignificantly small influence of drain and source bias, is set by

$$\varepsilon_1(0) = -qV_{G}' + \frac{q^2 n_{s,(\varepsilon_1(0))}}{C_{ox}}$$

(2.9)

The electron velocity is proportional to the derivative of the energy,  $v_x = \hbar^{-1} dE/dk$ . The charge can be calculated by integrating the product of the 1D density of states and the probability that each state is occupied, which is described by the Fermi-Dirac distribution.

$$n = \int_{E_c}^{\infty} D(E) f_0(E) dE = \int_{E_c}^{\infty} \frac{D(E) dE}{1 + e^{(E - E_f)/k_B T}}$$

(2.10)

Where the density of states for 1 dimension is:

$$D_{1D}(E) = \frac{\sqrt{2m^*}}{\pi\hbar} \sqrt{\frac{1}{E - E_c}}$$

(2.11)

The charge can be divided into two parts, carriers with positive and negative k-states travelling in opposite directions. The solution to the integral in (2.11) is seen below, where  $N_{ID}$  is the effective density of states and  $F_{-1/2}$  is the Fermi Dirac integral of order -1/2.

$$n_L^+(0) = \frac{N_{1D}}{2} F_{-\frac{1}{2}}(\eta_F) \tag{2.12}$$

With the constant  $\eta_F = \frac{(E-E_C)}{k_B T_L}$ , where  $N_{1D} = \frac{\sqrt{2m^* k_B T_L/\pi}}{\hbar}$  is the effective density of states and  $F_{-\frac{1}{2}}(\eta_F) = \frac{2\eta_F^{1/2}}{\sqrt{\pi}}$  is the Fermi Dirac integral of order -1/2. For negative k-states, the drain bias has shifted the drain fermi-energy downwards, why  $U_D$  is added to the expression.

$$n_L^-(0) = \frac{N_{1D}}{2} F_{-\frac{1}{2}} (\eta_F - U_D)$$

(2.13)

$$U_D = \frac{qV_{DS}}{k_B T_L} \tag{2.14}$$

Next to, obtain the current, we calculate the sum of all k-states and start with the positive k-vectors.

$$I^{+} = \frac{1}{L} \sum_{k>0} qv \, f_0(E_F) \stackrel{\text{def}}{=} q n_L^{+}(0) v^{+}(0)$$

(2.15)

This can be remade into an integral, if taking into account that each k-state occupies a length of  $2\pi/L$ .

$$I^{+} = \frac{2q}{2\pi\hbar} \int \frac{dE}{dk} f_0(E(k), E_F) dk = \frac{2q}{\hbar} \int_{E_C}^{\infty} f_0(E(k), E_F) dE$$

(2.16)

Here it is seen that the ballistic current is not dependent on effective mass, due to that the terms regarding effective mass in the density of states and electron velocity cancels for 1D transport. The solution to the equation is

$$I^{+} = \frac{qk_BT_L}{\pi\hbar}F_0(\eta_F) \tag{2.17}$$

$$F_0(\eta_F) = \ln(1 + e^{\eta_F}) \tag{2.18}$$

By combining equation (2.15) with equation (2.12) we can also get an expression for the velocity for the carriers with positive momentum

$$v^{+}(0) = v_T \frac{F_0(\eta_F)}{F_{-1/2}(\eta_F)}$$

(2.19)

where the  $v_T$  is expressed as:  $v_T = \sqrt{2k_BT_L/\pi m^*}$ . The same reasoning can be done for the negative k-states, and current, with the velocity:

$$v^{-}(0) = v_T \frac{F_0(\eta_F - U_D)}{F_{-1/2}(\eta_F - U_D)}$$

(2.20)

Next we calculate the total current:

$$I = I^{+} - I^{-} = \frac{2qk_{B}T_{L}}{h} \{F_{0}(\eta_{F}) - F_{0}(\eta_{F} - U_{D})\}$$

(2.21)

If we assume that the bands are degenerate,  $\eta_F \gg 1$  as they often are for III-V semiconductors, and the top of the barrier is below the fermi-level on both source and drain side, i.e. small drain biases, the equation above simplifies to

$$I_D = \frac{2q^2}{h} V_{DS} (2.22)$$

In the QCL limit, where  $C_Q \ll C_{ox}$  equation (2.21) turns into equation (2.23) which is independent of material parameters.

$$I_D = \frac{2q^2}{h}(V_{GS} - V_T) \tag{2.23}$$

### 2.5 Two-port measurements

The transistor is a three-terminal device, but when the transistor is biased in common-source configuration, the source terminal is grounded and the transistor can be measured in a two-port measurement with AC-signals supplied to the gate and drain contacts. In an S-parameter measurement, incident electromagnetic power waves  $a_i$  are applied at the two ports and the reflected power waves  $b_i$  are measured. From this, the scattering matrix S consisting of reflection coefficients  $S_{11}$  and  $S_{22}$  and transmission coefficients  $S_{21}$  and  $S_{12}$  can be calculated[30].

The benefit of measuring S-parameters compared to the more intuitive Y- or Z-parameters is that the former only require 50  $\Omega$  termination in the vector network analyzer (VNA) while the two latter requires perfect open and short terminations which is difficult to achieve in a high-frequency environment, effectively reducing the measurement accuracy [31].

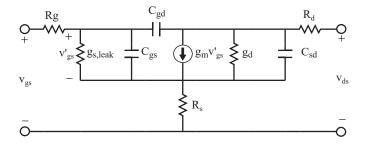

### 2.6 Small signal modeling

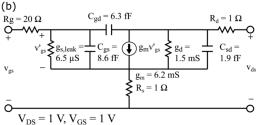

For optimization of the high-frequency performance of a MOSFET, it is very important to be able to quantify the performance limiting aspects of the transistor. A small-signal hybrid- $\pi$  model can be used to make a physical representation of the transistor [32]. To extract the different elements of the model, the measured S-parameters are first deembedded (more information section 2.8) and then transformed into impedance parameters Z. Next, estimated source and drain resistances  $R_s$  and  $R_d$  are subtracted from the Z-parameters before the parameters are transformed to Y-parameters, which is the basis of the parameter extraction. The small signal elements can be extracted according to equations (2.25) to (2.31) and the small-signal model can be seen in figure 2.2.

$$g_m = Re(Y_{21})|_{\omega^2 = 0} (2.25)$$

$$g_{ds} = Re(Y_{22})|_{\omega^2 = 0} \tag{2.26}$$

$$R_g = \frac{Re(Y_{11})}{Im(Y_{11})^2} \tag{2.27}$$

$$C_{gd} = \frac{-Im(Y_{12})}{\omega} \tag{2.28}$$

$$C_{gs} = \frac{Im(Y_{11}) + Im(Y_{12})}{\omega}$$

(2.29)

$$C_{dg} = \frac{-Im(Y_{21})}{\omega} - g_m R_g (C_{gs} + C_{gd})$$

(2.30)

$$C_{sd} = \frac{-Im(Y_{22})}{\omega} - C_{gd} - g_m R_g C_{gd} + \omega^2 C_{gd} C_{dg} (C_{gs} + C_{gd}) R_g^2$$

(2.31)

When all parameters of the model have been extracted, the modeled Y-parameters can be calculated, and subsequently the modeled Z-parameters with added source and drain resistances R<sub>s</sub> and R<sub>d</sub>. This way, the transistor behavior can be modeled up to higher frequencies, based on measurements up to relatively low frequencies. This model agrees with the transistor behavior fairly well, but none ideal effects can be added to make the model match the device under test. For instance, at high drain

**Figure 2.2:** A small signal hybrid- $\pi$  model used to model the RF devices in this thesis. Here Rg is the effective gate resistance with the channel resistance included.

bias, impact ionization and band to band tunneling effects can be added as current sources [33] and time dependent effects as oxide traps can be added as frequency dependent conductance [34].

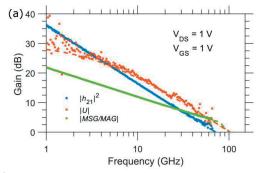

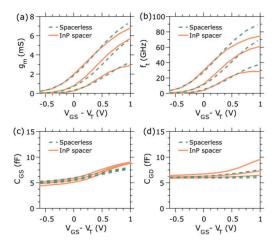

#### 2.7 RF metrics

A transistor working as an analog device to amplify a signal needs to have gain, otherwise the signal on the output would be smaller than the input and noise would be added. Gain can be defined in several ways, where the most common ones are current gain and power gain. The current gain of the device can be calculated from the measured Y-parameters.

$$h_{21} = \frac{i_2}{i_1} \Big|_{V_1 = 0} = \frac{Y_{21}}{Y_{11}} \tag{2.32}$$

Reactance in the transistor will behave as short circuits at very high frequencies, and the transistor will no longer have current gain, leading to that the AC gate leakage current will be as large as the source drain current. The maximum current gain frequency  $f_T$  is defined as the frequency where the ratio of these two currents are unity, and can be estimated by plotting  $|h_{21}|^2$  in a semi-log plot up to the measured frequency limit and then extrapolating with a slope of -20 dB/decade. The other approach is to report the value that the y-parameters from the small-signal model predicts. This can give a slightly higher result, as the small signal modeled gain often deviates from -20 db/decade slope at higher frequencies.

**Figure 2.3:** Maximum stable gain and maximum available gain where the intersection is the k-point for an arbitrary transistor. The gain of the transistor quickly drops after this point.

An approximate value of  $f_T$  can also be obtained from the parameters of the small signal model.

$$f_T \approx \frac{g_m}{2\pi (C_{qs} + C_{qd})} \tag{2.33}$$

Optimizing for large  $f_T$ , which is important for low RF noise, means that the transistor should have a high transconductance and small parasitic capacitances. The other important gain of the transistor is the power gain. Maximum available gain is defined as

$$MAG = \frac{Y_{21}}{Y_{12}}(k - \sqrt{k^2 - 1}) \tag{2.34}$$

Where the stability factor k is defined as.

$$k = \frac{2Re(Y_{11})Re(Y_{22}) - Re(Y_{12}Y_{12})}{|Y_{12}Y_{21}|}$$

(2.35)

When k > 1, the transistor is unconditionally stable and the circuit designer can optimize gain without worrying about the stability. If k < 1, the transistor is conditionally stable and then the maximum stable gain is defined as.

$$MSG = \frac{Y_{21}}{Y_{12}} \tag{2.36}$$

MSG can also be approximated with small signal model elements as seen in equation (2.37).

$$MSG(f) \approx \frac{1}{f} \frac{g_m}{2\pi C_{gd}}$$

(2.37)

When k = 1, MSG = MAG and this frequency is called the k-point. In order to increase the power gain at frequencies below the k-point, for instance at 5 and 20 GHz, where many communication important frequencies are, all aspects of optimizing for  $f_T$  applies, but with special emphasis on low drain capacitance  $C_{gd}$ . At frequencies above the k-point, the gain drops quickly and it can therefore be useful to increase the k-point as much as possible, see figure 2.3. For a transistor with a passive feedback network, the corresponding maximum power gain of the transistor is called Mason's unilateral power gain U and can be calculated as

$$U = \frac{|Y_{21} - Y_{12}|^2}{4(Re(Y_{11})Re(Y_{22}) - Re(Y_{12})Re(Y_{21}))}$$

(2.38)

The frequency at which the power gain U is unity is called maximum oscillation frequency  $f_{max}$  and for small source and drain resistances,  $f_{max}$  can be approximated

$$f_{max} \approx \sqrt{\frac{f_T}{8\pi R_G (C_{gd} + \frac{C_{gg}g_d}{g_m})}}$$

(2.39)

This means that high  $f_T$  usually also leads to a higher  $f_{max}$  but in order to maximize  $f_{max}$ , the gate resistance, output conductance and especially drain capacitance needs to be low. Due to the gate resistance entering the equation, peak  $f_{max}$  typically occurs at smaller device width than peak  $f_T$ .

**Figure 2.4:** Schematic images for device under test as well as short and open deembedding structures.

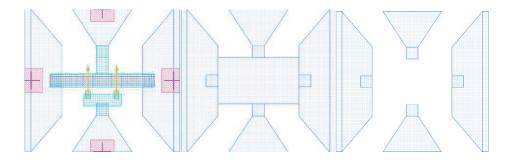

## 2.8 Calibration and de-embedding

In an RF measurement of a transistor, the measured parameters from a VNA is not only dependent on the device under test, but also pads, probes, cables and connectors. However, when designing an amplifier, it is important to know the performance of the device itself, otherwise device modeling will be incorrect and matching networks of the device will be flawed. Therefore two things are necessary to perform in order to know the real performance of the device. First, the VNA must be calibrated to move the reference point from the connectors of the VNA, to the tip of the probes with LRRM calibration (line, reflect, reflect match) using an impedance standard substrate (ISS) [35]. Next, in order to not let admittance and impedance in probes and pads affect the modeling of the device under test, the reference plane must be moved from the probe tips to the edge of the transistor. This is done with open and short deembedding [36]. The open and short reference structures are fabricated simultaneously with the transistor on the substrate and measured with the VNA. Layout of device under test (DUT), open and short deembedding can be seen in figure 2.4. First, the measured S-parameters of open, short and device under test are transformed into Y-parameters. To eliminate the capacitance from the open structure, the measured open Y-parameters,  $Y_0$ , is subtracted from both the short,  $Y_{S-O} = Y_S - Y_O$  and the device under test  $Y_{DUT-O} =$  $Y_{DUT} - Y_0$ . Next, in order to remove the inductances of the short reference, the subtracted Y-parameters are transformed into Z-parameters, and the Z-parameters of the short reference structure is subtracted from the device under test to give the deembedded Z parameters,  $Z_{DE} = Z_{DUT-O} - Z_{S-O}$ . Finally, the de-embedded Zparameters can be transformed into S-parameters again for further analysis.

## 3 Semiconductor crystals and doping

This section covers two important aspects of semiconductor manufacturing that greatly affect the performance and characteristics of III-V electronic devices, namely doping of the semiconductor crystals, and the effect of facets in the crystal lattice.

## 3.1 Doping

Doping of a semiconductor was first realized by John Robert Woodyard in 1950, and has led to a rapid evolution in the semiconductor industry[37]. Doping a semiconductor with very small portions of another material, with either surplus or deficit of valence electrons gives rise to n-type or p-type doping, drastically changing the conductivity of the material. P-n junctions, where both type of doping are used in sequence, is the fundamental building block of most types of solar cells, LEDs, as well as in bipolar junction transistors, in order to create electric fields forcing electrons and holes to either separate or recombine [38]. In CMOS technology, for an n-type and p-type device conducting current with electrons or holes respectively. A few of the most common dopants for III-V semiconductors used in high-speed devices are Si, Sn and S for n-type dopants and Zn for p-type dopants, while Fe is used to insulate III-V substrates. Both silicon and tin are group IV elements. This means that they can act either as donors or acceptors depending on if they occupy the group III or V position in the lattice. N-type doping with group IV atoms can thus autocompensate and saturate at high doping levels due to occupancy of group V sites. This also makes the free carrier concentration levels with group IV atoms dependent on V/III ratios during growth[39].

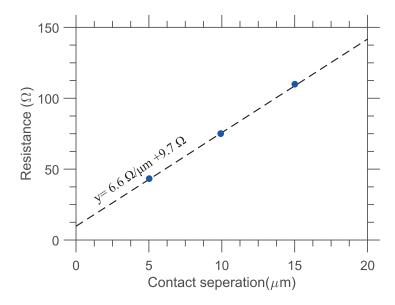

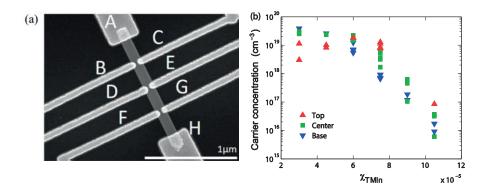

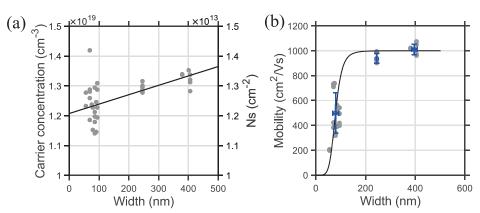

#### 3.1.1 Hall measurements

There are many techniques available to determine the carrier concentration of electron and holes in a nanowire, for instance photoluminescence [40],

cathodoluminescence [41], field-effect measurements as well as recently Hall measurements [42]. Although optical measurements is not inducing any damage in the nanowire, most times it requires that the nanowires are broken off and moved to a specific measurements substrate. This is however difficult if the nanowires are lateral and grown into the substrate itself. Another drawback is the fairly low spatial resolution obtainable. Field-effect measurements does not require that the nanowires are transferred to another substrate, but is difficult to estimate the capacitance between the gate and the channel due to the occurrence of semiconductor capacitance and oxide capacitance, the latter suffering from uncertainties in density of interface traps affecting the capacitance. Hall measurements is another way of determining the carrier concentration in a semiconductor and at the same time obtaining the mobility of the carriers. In 2012 Storm et al published the first spatially resolved Hall measurements on nanowires, where the doping profile along the nanowire could be established [43]. However, evaporating contacts on each side of the nanowire with a sufficient spacing is a challenge for nanowires of small dimensions. The selective area growth of lateral nanowires has the possibility of simultaneous growth of semiconductor contacts to the nanowire in the same growth step as the nanowire itself, which then can be contacted with larger metal contacts in a subsequent step.

An electron moving with a velocity in a simultaneous electric and magnetic field is exposed to a force, called the Lorentz force.

$$F = q(\mathbf{E} + v \times \mathbf{B}) \tag{3.1}$$

In a Hall measurement setup, the electron moves in x-direction due to an applied electric field, and a magnetic field is applied in z-direction. Then equation (3.1) can be simplified.

$$F_{z} = 0 (3.2)$$

$$F_{y} = qv_{x}B_{z} \tag{3.3}$$

$$F_{x} = qE_{x} \tag{3.4}$$

This means that compared to standard drift current, the electrons also exhibits a force in y-direction, causing the electrons path to diverge, giving an accumulation of electrons on one side and a depletion on the other, generating a voltage that is called the Hall voltage. The force from the electric field in y-direction, the Hall field, generated from the Hall voltage will at steady state cancel out the force from the applied magnetic field.

$$\frac{qV_H}{w} = qv_x B_z \tag{3.5}$$

The Hall voltage can then be calculated from the width, velocity in x-direction and the applied magnetic field.

$$V_H = w v_r B_z \tag{3.6}$$

The current in x-direction is also dependent on thickness of the semiconductor and can be written as

$$I_{r} = qtnwv_{r} \tag{3.7}$$

Inserting this into equation (3.6), the Hall voltage can finally be written as equation.

$$V_H = \frac{I_x B_z}{qtn} \tag{3.8}$$

The Hall voltage is thus proportional to the applied magnetic field and current, and inversely proportional to the electron charge, thickness of the semiconductor and importantly the carrier concentration. By also measuring the resistivity of the semiconductor, the mobility of the charged carriers can be calculated as:

$$\mu = \frac{1}{qn\rho} \tag{3.9}$$

For a cylindrical nanowire as in paper VI, with thickness and width being equal to the diameter, with metal contacts directly in contact with the nanowire that cannot be regarded as point contacts, the extracted carrier concentration can differ slightly from the true carrier concentration. We therefore extended the equations to allow for electric fields existing in all three directions, x, y and z, and modeled the electric fields and Hall voltage in a finite element method program called COMSOL Multiphysics. The drift current  $J_{n,drift} = \sigma E$ , can be modeled with the three dimensional conductivity tensor according to

$$\sigma = \sigma_0 \begin{pmatrix} \frac{1}{1 + (\frac{q\tau}{m^*}B)^2} & \frac{\frac{q\tau}{m^*}B}{1 + (\frac{q\tau}{m^*}B)^2} & 0\\ -\frac{q\tau}{m^*}B & \frac{1}{1 + (\frac{q\tau}{m^*}B)^2} & \frac{1}{1 + (\frac{q\tau}{m^*}B)^2} & 0\\ 0 & 0 & 1 \end{pmatrix}$$

(3.10)

where  $\sigma_0 = (\frac{q^2 \tau n}{m^*})$  [26]. More information on Hall measurements on nanowires can be found in [43].

#### 3.1.2 Modulation doping

One way to decrease the resistivity in a semiconductor is to dope it, with very small portions of donor atoms. However, the doping leaves ionized donor atoms behind, which will reduce the electron mobility in the doped material due to increased amount of scattering events. In 1977, Bell labs developed a scheme where the doping was performed in a wide band gap material just next to a narrow band gap material [44]. Due to the difference in band gap, the free carriers will fall into the narrow band gap material, as the electrons strive to lower its potential energy, effectively separating the carriers from its ionized donors. This gives a high amount of carriers in the narrow channel material, while still maintaining a high mobility.

## 3.2 III-V semiconductor crystal

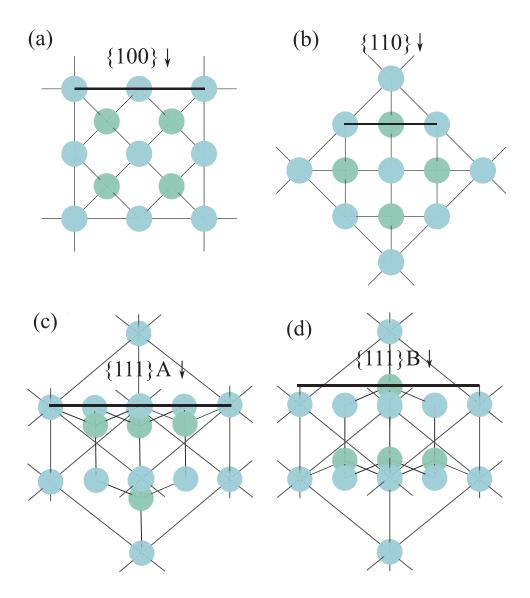

III-V compounds typically forms crystals in zincblende structure, but III-V nanowires can also be wurtzite, where the inclusion of one of them inside the other one is called a stacking fault. One common substrate is the (100) zincblende which

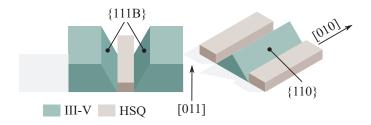

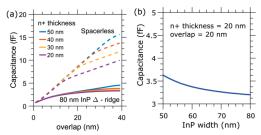

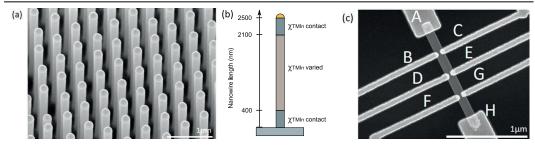

**Figure 3.1:** Depending on alignment of HSQ growth mask in [011] and [010], different facets of the semiconductor is obtained, {111}B or {110} with an angle of 54.7° and 45° towards the top {100} facet respectively.

been used for the selective area growth in this thesis. Depending on the alignment of the SiO<sub>2</sub> growth mask, semiconductor structures bound by {110} and {111} side walls can be obtained which can be seen in figure 3.1. In figure 3.2, the positions of the atoms for four different kind of low order facets is illustrated, {100}, {110}, {111}A and {111}B planes. Each atom in the lattice, has four electrons to bind to neighboring atoms of the other atomic type. {100} facets are consisting of a single group of atoms, either group III or V, and there are two dangling bonds at the surface. Since the crystal is symmetric in this direction, there is no separation between A and B type. {110} planes have equal amount of group III and V atoms at the surface, and there is one dangling bond per atom. {111} planes are however different, as they can be either A or B, depending on if the surface is group III or V terminated respectively. Typically, the growth rate of {111} planes are slower than {100} due to fewer dangling bonds giving rise to an increased diffusion length of ad atoms, making it possible for atoms to diffuse to the (100) top facet during growth. Mask openings aligned in [011] directions give {111}B facets that are especially technologically important as these facets slope away from the growth mask, avoiding mask overgrowth. [01-1] aligned mask openings give {111}A facets that are typically less stable than {111}B facets and grow faster in MOVPE growth which typically leads to upward facing {111}A facets and simultaneously downward facing {111}B facets, overgrowing the growth mask. This effect can also be beneficial, although not used in this thesis, if self-aligned spacer schemes is to be employed, although it requires very careful planning of the thicknesses of epitaxial layers and mask layers. The reason for these growth rates is linked to the fact that MOVPE is usually growth with high V-III ratios, where we have a surplus of group V atoms at the surface, and the growth rate is limited by the supply of group III atoms.

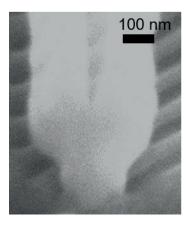

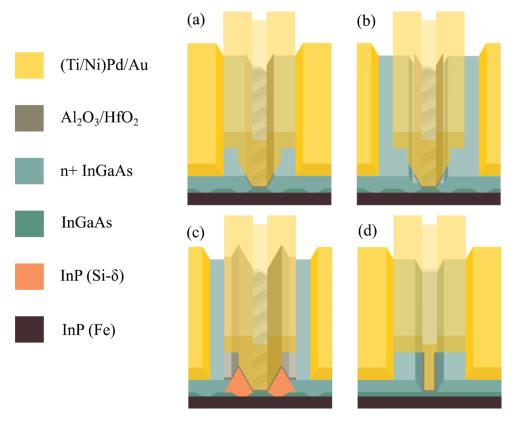

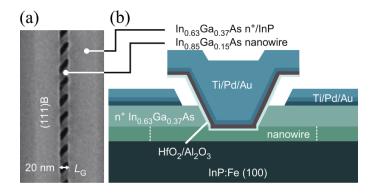

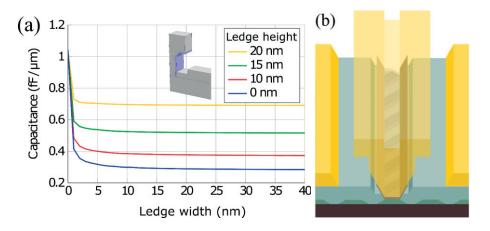

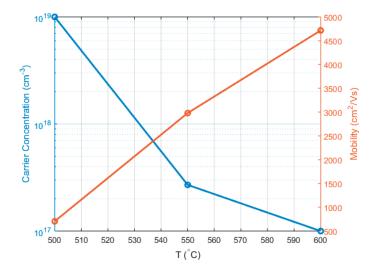

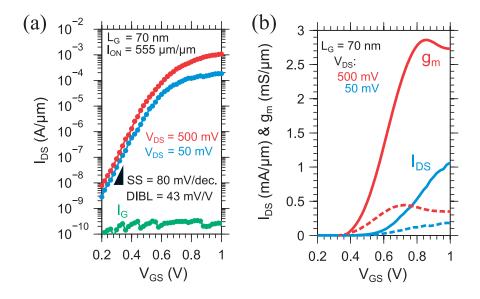

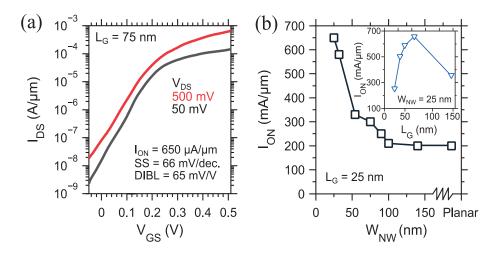

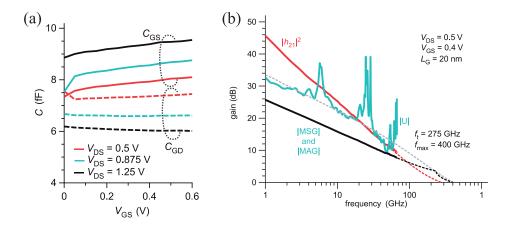

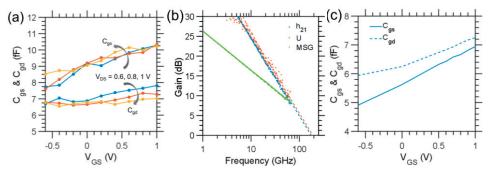

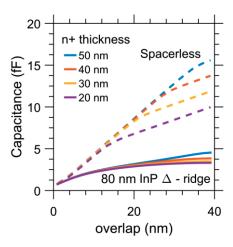

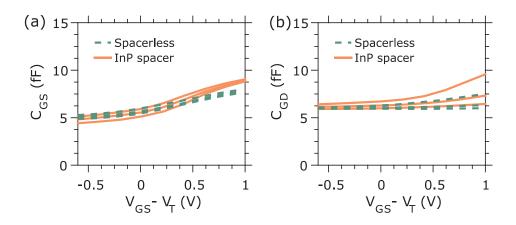

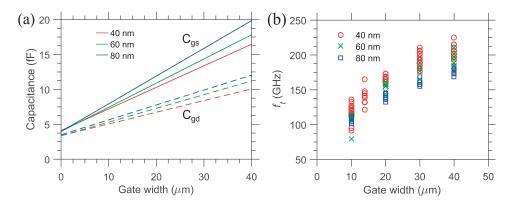

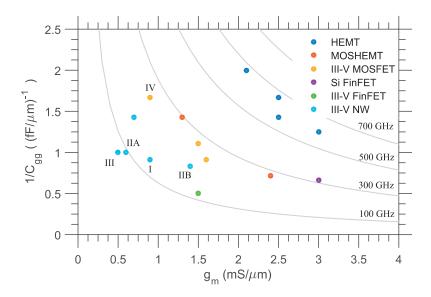

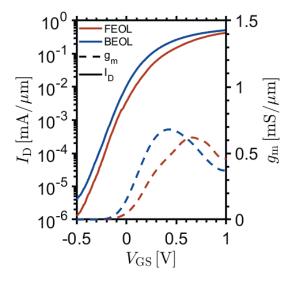

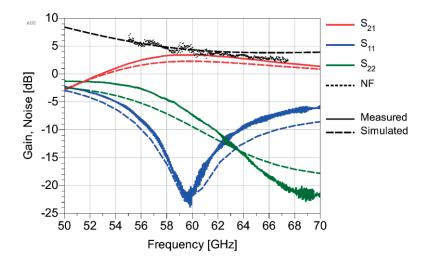

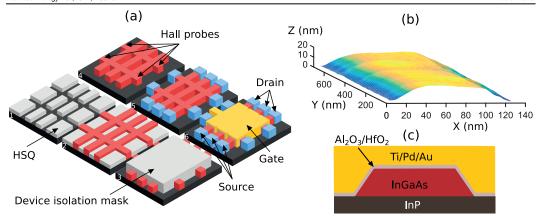

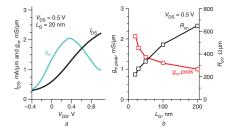

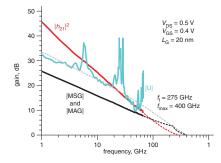

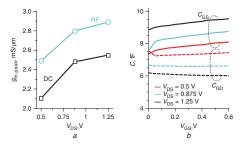

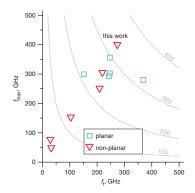

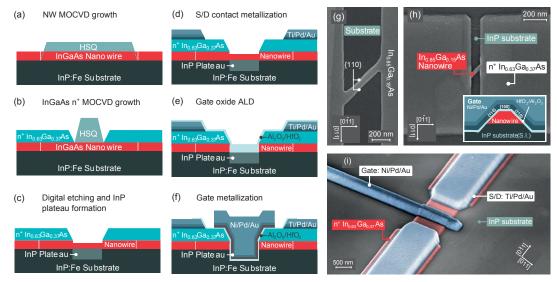

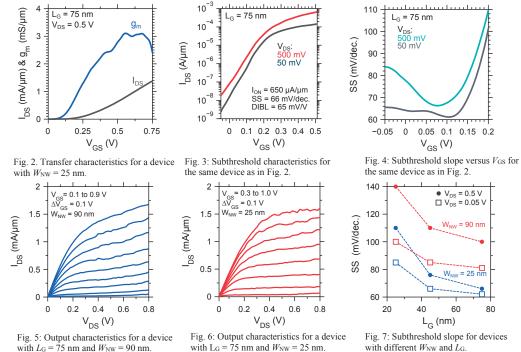

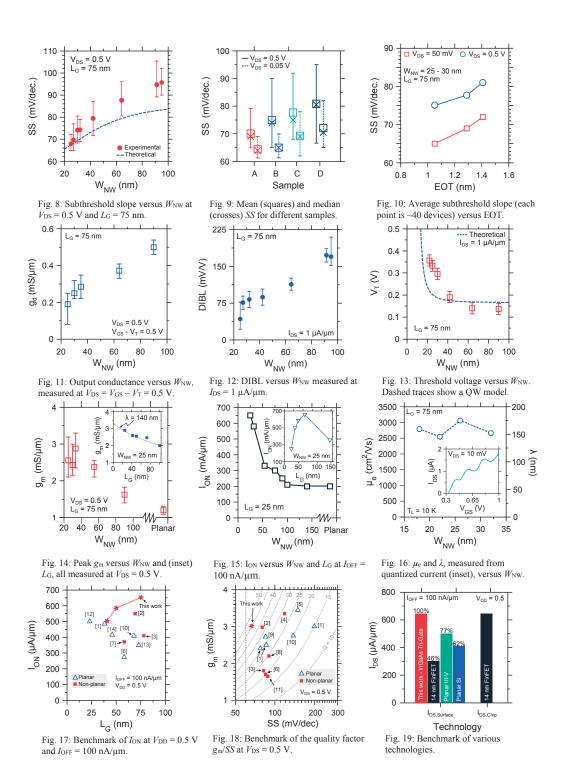

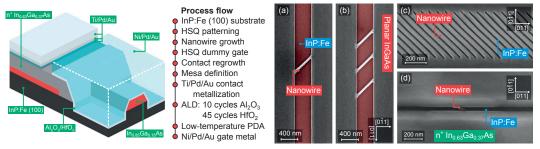

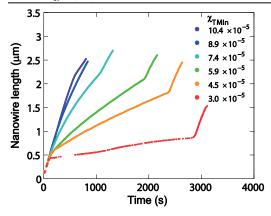

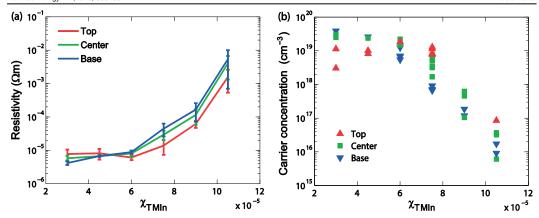

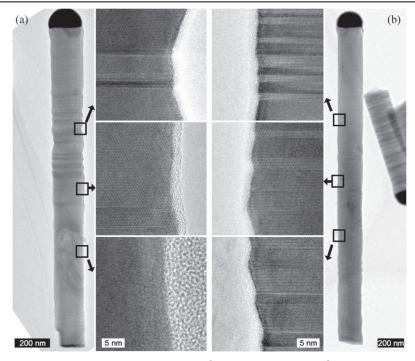

**Figure 3.2:** Unit cube of zincblende atomic structure where each mentioned plane is pointing upwards. The lines between blue atoms outlines the unit cube, and the lines between blue and green atoms indicate atomic bonds. (a) {100} plane consists of a single atom type, (b){110} plane consist of equal amount of group III and V, (c) {111}A and (d) {111}B plane is group III or V terminated respectively.