#### III-V Nanowire MOSFET High-Frequency Technology Platform

Andric, Stefan

2021

Document Version: Publisher's PDF, also known as Version of record

Link to publication

Citation for published version (APA): Andric, S. (2021). III-V Nanowire MOSFET High-Frequency Technology Platform. Department of Electrical and Information Technology, Lund University.

Total number of authors:

General rights

Unless other specific re-use rights are stated the following general rights apply:

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

• Users may download and print one copy of any publication from the public portal for the purpose of private study

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal

Read more about Creative commons licenses: https://creativecommons.org/licenses/

Take down policy

If you believe that this document breaches copyright please contact us providing details, and we will remove access to the work immediately and investigate your claim.

# III-V Nanowire MOSFET High-Frequency Technology Platform

STEFAN ANDRIĆ

DEPARTMENT OF ELECTRICAL AND INFORMATION TECHNOLOGY

FACULTY OF ENGINEERING | LTH | LUND UNIVERSITY

### III-V Nanowire MOSFET High-Frequency Technology Platform

**Doctoral Thesis**

Stefan Andrić

Department of Electrical and Information Technology Lund, May 2021

Academic thesis for the degree of Doctor of Philosophy, which, by due permission of the Faculty of Engineering at Lund University, will be publicly defended on Friday, 28 May, 2021, at 9:15 a.m. in lecture hall E:1406, Department of Electrical and Information Technology, Ole Römers Väg 3, 223 63 Lund, Sweden. The thesis will be defended in English.

The Faculty Opponent will be Prof. Ingmar Kallfass.

| Organisation: LUND UNIVERSITY Department of Electrical and Information Technology Ole Römers Väg 3 223 63 Lund Sweden  Author: Stefan Andrić | Document Type:<br>DOCTORAL THESIS                                                                                           |

|----------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                              | Date of Issue:<br>04 May 2021                                                                                               |

|                                                                                                                                              | Sponsoring Organisation(s): Swedish Foundation for Strategic Research (SS Swedish Research Council (VR) European Union (EU) |

Title.

III-V Nanowrie MOSFET High-Frequency Technology Platform

#### Abstract:

This thesis addresses the main challenges in using III-V nanowire MOSFETs for high-frequency applications by building a III-V vertical nanowire MOSFET technology library. The initial device layout is designed, based on the assessment of the current IIII-V vertical nanowire MOSFET with state-of-the-art performance. The layout provides an option to scale device dimensions for the purpose of designing various high-frequency circuits. The nanowire MOSFET device is described using 1D transport theory, and modeled with a compact virtual source model. Device assessment is performed at high frequencies, where sidewall spacer overlaps have been identified and mitigated in subsequent design iterations. In the final stage of the design, the device is simulated with  $f_T > 500$  GHz, and  $f_{max} > 700$  GHz.

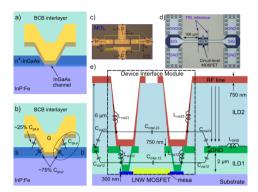

stage of the design, the device is simulated with  $f_T > 500$  GHz, and  $f_{max} > 700$  GHz. Alongside the III-V vertical nanowire device technology platform, a dedicated and adopted RF and mm-wave back-end-of-line (BEOL) has been developed. Investigation into the transmission line parameters reveals a line attenuation of 0.5 dB/mm at 50 GHz, corresponding to state-of-the-art values in many mm-wave integrated circuit technologies. Several key passive components have been characterized and modeled. The device interface module - an interconnect via stack, is one of the prominent components. Additionally, the approach is used to integrate ferroelectric MOS capacitors, in a unique setting where their ferroelectric behavior is captured at RF and mm-wave frequencies.

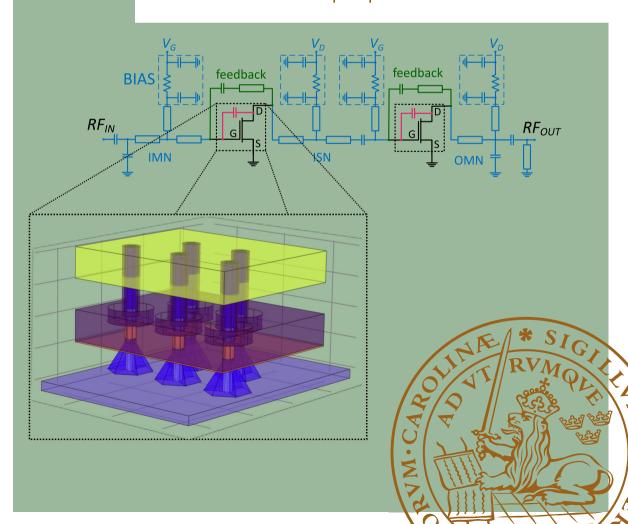

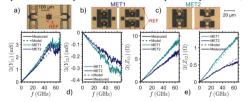

Finally, circuits have been designed. A proof-of-concept circuit, designed and fabricated with III-V lateral nanowire MOS-FETs and mm-wave BEOL, validates the accuracy of the BEOL models, and the circuit design. The device scaling is shown to be reflected into circuit performance, in a unique device characterization through an amplifier noise-matched input stage. Furthermore, vertical-nanowire-MOSFET-based circuits have been designed with passive feedback components that resonate with the device gate-drain capacitance. The concept enables for device unilateralization and gain boosting. The designed low-noise amplifiers have matching points independent on the MOSFET gate length, based on capacitance balance between the intrinsic and extrinsic capacitance contributions, in a vertical geometry. The proposed technology platform offers flexibility in device and circuit design and provides novel III-V vertical nanowire MOSFET devices and circuits as a viable option to future wireless communication systems.

#### Keywords:

MOSFET, III-V, Nanowire, Technology library, Process Monitor Structures, Radio Frequency, Millimeter Wave, Compact Modelling, Circuit Design, Matching Networks, Low Noise Amplifier.

| Classification System and/or Index Terms<br>e.g. Electronic Engineering, Nano Technology | <i>Language:</i><br>English              |                                      |  |

|------------------------------------------------------------------------------------------|------------------------------------------|--------------------------------------|--|

| Supplementary Bibliographical Information: –                                             |                                          | ISBN (printed):<br>978-91-7895-841-2 |  |

| Key title and ISSN:<br>Series of Licentiate and Doctoral Theses; 1654-790X, No. 137      |                                          | ISBN (digital):<br>978-91-7895-842-9 |  |

| Recipient's Notes: Number of Pages: 126                                                  |                                          | Price:                               |  |

|                                                                                          | Security Classification:<br>Unclassified |                                      |  |

General Permissions

Any & Cuta

I, the undersigned, being the copyright owner and author of the above-mentioned thesis and its abstract, hereby grant to all reference sources permission to publish and disseminate said abstract.

Signature:

Date: 04 May 2021

## III-V Nanowire MOSFET High-Frequency Technology Platform

**Doctoral Thesis**

Stefan Andrić

Department of Electrical and Information Technology Lund, May 2021 Stefan Andrić Department of Electrical and Information Technology Lund University Ole Römers Väg 3, 223 63 Lund, Sweden

Series of Licentiate and Doctoral Theses ISSN 1654-790X, No. 137 ISBN 978-91-7895-841-2 (printed) ISBN 978-91-7895-842-9 (digital)

#### © 2021 Stefan Andrić

This thesis is typeset using  $\LaTeX 2_{\varepsilon}$  with the body text in Palatino and Goudy Initials, headings in Helvetica, and text in figures in Arial and Computer Modern.

Frontispiece: Nanowire LNA circuit diagram, with COMSOL structural model of the nanowire MOSFET array.

Printed by Tryckeriet i E-huset, Lund University, Lund, Sweden.

No part of this thesis may be reproduced or transmitted in any form or by any means without written permission from the author. Distribution of the original thesis in full, however, is permitted without restriction.

To You, Who Inspire Me.

- S

### **Abstract**

HIS thesis addresses the main challenges in using III-V nanowire MOSFETs for high-frequency applications by building a III-V vertical nanowire MOSFET technology library. The initial device layout is designed, based on the assessment of the current III-V vertical nanowire MOSFET with state-of-the-art performance. The layout provides an option to scale device dimensions for the purpose of designing various high-frequency circuits. The nanowire MOSFET device is described using 1D transport theory, and modeled with a compact virtual source model. Device assessment is performed at high frequencies, where sidewall spacer overlaps have been identified and mitigated in subsequent design iterations. In the final stage of the design, the device is simulated with  $f_T > 500 \text{ GHz}$ , and  $f_{max} > 700 \text{ GHz}$ .

Alongside the III-V vertical nanowire device technology platform, a dedicated and adopted RF and mm-wave back-end-of-line (BEOL) has been developed. Investigation into the transmission line parameters reveals a line attenuation of 0.5 dB/mm at 50 GHz, corresponding to state-of-the-art values in many mm-wave integrated circuit technologies. Several key passive components have been characterized and modeled. The device interface module - an interconnect via stack, is one of the prominent components. Additionally, the approach is used to integrate ferroelectric MOS capacitors, in a unique setting where their ferroelectric behavior is captured at RF and mm-wave frequencies.

Finally, circuits have been designed. A proof-of-concept circuit, designed and fabricated with III-V lateral nanowire MOSFETs and mm-wave BEOL,

validates the accuracy of the BEOL models, and the circuit design. The device scaling is shown to be reflected into circuit performance, in a unique device characterization through an amplifier noise-matched input stage. Furthermore, vertical-nanowire-MOSFET-based circuits have been designed with passive feedback components that resonate with the device gate-drain capacitance. The concept enables for device unilateralization and gain boosting. The designed low-noise amplifiers have matching points independent on the MOSFET gate length, based on capacitance balance between the intrinsic and extrinsic capacitance contributions, in a vertical geometry. The proposed technology platform offers flexibility in device and circuit design and provides novel III-V vertical nanowire MOSFET devices and circuits as a viable option to future wireless communication systems.

## Popular Science Summary

AVE you ever wondered what is inside your electronic gadgets? Nowadays, we became used to the advanced functionality of mobile phones, the very fast internet in our homes and a great connectivity as we move. All this comes from decades of development in the field of information and computer technology (ICT). And the drive in the field is to make the experience for the users be as seamless as possible. Such end goal forces the ICT systems to be ever-more complex and to handle an increasing amount of data *instantly*. In the core of this data processing lie units that are widely known as *computer chips*.

Looking into those chips, we find something you can imagine as a highway for signals, but on many levels, and some ten thousand times narrower than a strand of hair. We would be observing nanoscale electronic circuits, the greatest engineering achievement of the modern world! Below this interconnect 'highway' lies a nano-engineered surface where tiny electronic transistors are embedded. They are the brain of the chip and they use the 'highway' of interconnections to make complex decisions. These electronic transistors are organized according to their functionality, which allows us to imagine the inside of a chip as an array of smaller blocks executing specific tasks. They are known as electronic circuits. Those that are interesting, from the aspect of this thesis, are those that enable us to communicate with the outside world. The electronic transistors used in these circuits handle radio signals landing onto antennas hidden in our phones, computers, or any other wireless devices.

The challenge in designing these communication systems lies in the internal design of the nano-scale electronic transistor, for the purpose of handling these radio signals. The traditional transistors are limited in their speed of operation, so a novel approach is needed. The transistor presented here has a design that would push this speed limit further. The transistor shape is rather unusual - it is a vertically-standing nanometer-scale wire, or a pillar, as opposed to the ones embedded in the surface of the chip. The choice of such *nanowire* structure is motivated by an increased performance due to a freedom to choose materials and the nanowire shape more easily. The goal is, much like with traditional embedded transistors, to create the same type of circuitry as in the dense computer chips used today.

This thesis ties the investigation of such nanowires to the implementation of specific materials, so that resulting devices perform better than the industry standard in some aspects. The core research is in the organization and efficiency of nanowire transistors, and in the building blocks that enable the nanowire electronic circuits, towards achieving the ever-advancing wireless communication systems. A way forward is created for nanowire transistors, with exploring limits in their design and functionality. This makes them compatible with building complex systems that exceed current wireless standards (up to 6 GHz), going towards the radar, and the very high-speed electronics (10s to 100s of GHz). Hence, the vertically-standing nanowires are an interesting option to investigate, since the future of our society will eventually use those 100s of GHz for the data transfer, and to support the increased inter-connectedness.

### Acknowledgments

HIS pages are dedicated to all that have made this journey more enjoyable. I extend my greatest respect to my supervisors: Lars-Erik Wernersson, Lars Ohlsson, and Erik Lind. To Lars-Erik, I extend my gratitude for the given opportunity within the Nanoelectronics group. I looked into PhD studies only as a steppingstone in the carrier development, but it has now morphed into an ever-increasing wish to know more. I appreciate that spark that you managed to ignite during these years! And for making us all always see the bigger picture, and to look ahead! To Lars, I can only say thank you for the seemingly endless patience with my lack of knowledge that still is. You have thought me almost everything RF, and your critical sense have always made me take a closer look into things. And to Erik, I can proudly say that the most interesting course I have listened to in my long academic upbringing was given by you! I am grateful to the discussions and to be able to learn from you.

I am proud to be a part of the Nanoelectronics group over the last five years. Much has changed, but the experience will remain. I wish to thank Johannes, for always giving a nice word and for support in practical matters. To my fellow PhD students, I wish to acknowledge Fredrik, Olli-Pekka, and Adam, with whom I worked closely over the years and whom I greatly appreciate to have had as work colleagues. Fredrik, thank you for your enthusiasm, especially in the lab! Olli-Pekka, I thank you for the numerous samples (that I ruined) and for the close collaboration that pushed my research forward. Adam, I will always appreciate your humor, as well as your dedication to get the most out of your research. I acknowledge other group members, with whom I have shared (a portion of) my PhD experience: Cezar, Elvedin, Karl-Magnus, Sebastian, Mattias, Abinaya, Heera, Lasse, Saketh, Gautham, Marcus, Anton, Navya, Robin,

Patrik, Zhongyunshen, and Andrea. I greatly value the time we spent pushing boundaries. I appreciate your talent and expertise and I wish the best to all of you in your future endeavors.

Furthermore, I wish to thank the many administrative staff and department colleagues that have helped in making this a positive experience overall. During my time as a PhD student, I had an opportunity to work with *Thomas*, and *Arnulf*, from Fraunhofer Institute in Freiburg, Germany. I am most grateful to your guidance in the beginning of my PhD, a crucial time in my studies.

To combat PhD-induced stress, I thank Jonas and the entire team from Lunds Aikidoklubb. Over the last years, we have trained our body and mind together, in an array of the unforgettable experiences. I thank Thalea, Moa, Simon, Jakob for always being instructive and guiding me towards my inner calm, as well as Sara, Will, Natalie, Sandra, and many others, for their company and partnership in training. Also, to Lars-Göran (Lasse), I thank for unforgettable summers training Aikido up in Värmland! And to many other Aikidokas that I met from all corners of Sweden, you have made this experience a better one!

Finally, my cornerstone. You have made my final years that much more enjoyable, and with whom I wish to share my life with - thank you Samuel, for being my inspiration and for making me a better man! Eu amo, você é o amor da minha vida! I also thank my family that supported me all these years - Хвала вам на безусловној подршци: Мама, Таша, Иване, Ивана, Саро, Лука и Андреје. Без свих вас, цело ово искуство не би било потпуно! Without all of you, this experience would not be complete...

Cшефан Андрић / Stefan Andrić in Lund, May 2021.

## Contents

| Abstract                                | $\mathbf{v}$ |

|-----------------------------------------|--------------|

| Popular Science Summary                 | vii          |

| Acknowledgments                         | ix           |

| Contents                                | xi           |

| Preface                                 | xiii         |

| Structure of the Thesis                 | xiii         |

| Included Papers                         | xiv          |

| Related Work                            | XV           |

| Acronyms and Symbols                    | xvii         |

| Acronyms and Abbreviations              | xvii         |

| Latin Symbols                           | xix          |

| Greek Symbols                           | xxi          |

| Functions and Operators                 | xxii         |

| INTRODUCTION                            | 1            |

| 1 Fundamentals of RF Circuits           | 3            |

| 1.1 About Circuit Design                | 3            |

| 1.2 Nanoscale MOSFET as a Radio Device  | 5            |

| 1.2.1 MOSFET Basic Design and Operation | 5            |

| 1.2.2 Scaling of Radio MOSFETs          | 7            |

| 1.2.3 State-of-the-art Radio MOSFETs    | 9            |

| 2 III-V NW MOSFET Technology Platform   | 11           |

| 2.1 Nanowire MOSFETs - III-V Materials and 1D Transport               | 11         |

|-----------------------------------------------------------------------|------------|

| 2.1.1 Physics of Nanowire MOSFETs                                     | 13         |

| 2.1.2 Compact Modelling of Nanowire MOSFETs                           | 15         |

| 2.2 Layout of Nanowire MOSFET                                         | 16         |

| 2.3 Process Monitor Structure Design                                  | 19         |

| 3 High-Frequency BEOL for III-V NW MOSFETs                            | <b>2</b> 3 |

| 3.1 Transmission Line Theory                                          | 23         |

| 3.2 BEOL for III-V Nanowire MOSFET                                    | 26         |

| 3.2.1 Transmission Line Realizations                                  | 26         |

| 3.2.2 Co-Integrated RF BEOL                                           | 27         |

| 3.2.3 Millimeter-Wave BEOL                                            | 28         |

| 3.3 BEOL Performance Evaluation                                       | 29         |

| $3.3.1~\mathrm{TRL}$ Calibration and Transmission Line Properties     | 30         |

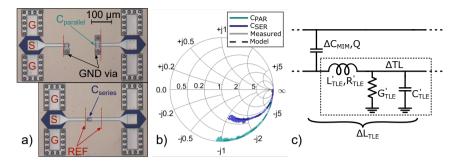

| $3.3.2~\mathrm{RF}$ BEOL Components - Ferroelectric MOS Capacitors $$ | 32         |

| 3.3.3 Millimeter-Wave BEOL Components                                 | 33         |

| 4 III-V NW MOSFET mm-Wave Devices and Circuits                        | 37         |

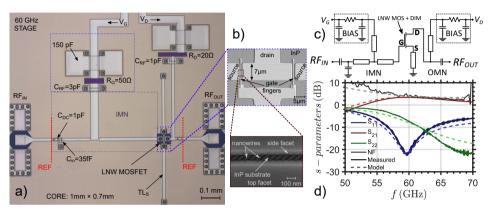

| 4.1 Lateral Nanowire MOSFET 60 GHz LNA Input Stage                    | 37         |

| 4.2 Vertical Nanowire MOSFET mm-Wave Design                           | 40         |

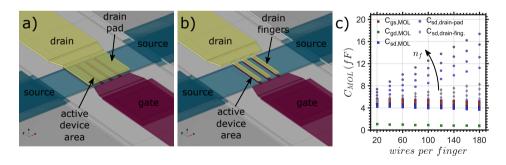

| 4.2.1 Vertical Nanowire MOSFET MOL Design                             | 41         |

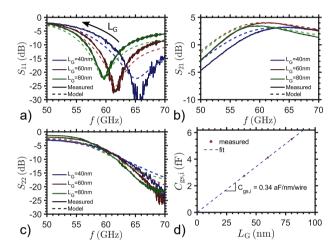

| 4.2.2 Optimization of VNW MOSFET Parasitic Capacitance                | 42         |

| 4.2.3 III-V VNW MOSFET mm-Wave Performance $\dots \dots$              | 45         |

| 4.2.4 III-V VNW MOSFET Device-to-Circuit Co-Design                    | 47         |

| 4.3 Vertical Nanowire MOSFETs Large-Signal Design                     | 49         |

| 4.4 Device and Circuit Benchmarking                                   | 51         |

| 5 Conclusions and Outlook                                             | <b>5</b> 5 |

| Bibliography                                                          | <b>57</b>  |

| APPENDICES                                                            | 71         |

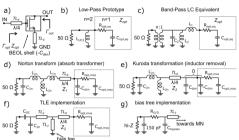

| A Optimum matching network design                                     | <b>7</b> 3 |

| A.1 RF Device in Circuit Design Environment                           | 73         |

| A.2 Optimum Matching Network Transformations                          | 74         |

| PΔPFRS                                                                | 77         |

### Preface

HIS thesis represents nearly five years of work in creating a suitable technology platform for design and simulation of III-V nanowire devices and circuits, at high frequencies. The work also represents a collaboration within the *Nanoelectronics* group at Lund University, supervised by Professor Lars-Erik Wernersson, Professor Erik Lind, and Dr. Lars Ohlsson Fhager.

#### STRUCTURE OF THE THESIS

The thesis is divided into several parts. First, a survey of the field is provided, conveying the message through discussion of circuit design strategies, ending with a performance benchmark for state-of-the-art device technologies. In the following section, a description of the III-V nanowire MOSFET technology platform is given. The focus lies in the device ballistic transport properties and compact modelling, as well as the layout organization of test vehicles, including the integration of structures for process monitoring. The third chapter describes the associated back-endof-line. The most of the experimental work is presented in this chapter, through characterization of different passive components. The final chapter describes the usage of the technology platform and the device design to form a basis for the circuit design and realization, as well as benchmark against established technologies.

#### INTRODUCTION

The Introduction provides a comprehensive and more general view of the thesis topic. The major points are described in detail in the publications related to this thesis. It is written in a way to appeal to

broader audiences and attract interest of students and researchers in this specific field.

#### APPENDICES

#### A Optimum Matching Network Design

Appendix A describes the optimum matching network design procedure, based on theoretical concepts that take into account transistor input and output quality factor and the set matching level, with the aim to maximize the available bandwidth. It forms a basis for circuit simulation and realization.

#### PAPERS

The papers, reproduced in the back of the thesis, are listed in the following. For some of the works, an input, weather as samples or model parameters, have been provided by Olli-Pekka Kilpi, Fredrik Lindelöw, Adam Jönsson, and Anton Persson.

#### **INCLUDED PAPERS**

The following papers form the structure of this thesis. These include journal papers and conference contributions, as well as works in a manuscript form. The respective papers and drafts are included in the back of this thesis.

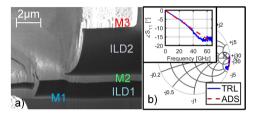

- Paper I: S. Andric, L. Ohlsson Fhager, F. Lindelöw, O.-P. Kilpi, and L.-E. Wernersson, "Low-temperature back-end-of-line technology compatible with III-V nanowire MOSFETs", *Journal of Vac-uum Science and technology B*, vol. 37, art. no. 061204, Oct. 2019, doi: 10.1116/1.5121017.

- ▶ I carried out standalone BEOL fabrication as well as the BEOL fabrication on top of test devices, performed device and test structures measurement and analyses, and wrote the paper.

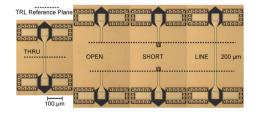

- Paper II: <u>S. Andric</u>, L. Ohlsson, and L.-E. Wernersson, "Low-Temperature Front-Side BEOL Technology with Circuit Level Multiline Thru-Reflect-Line Kit for III–V MOSFETs on Silicon", *92nd Microwave Measurement Conference (ARFTG)*, Orlando, FL, USA, pp. 1–4 Jan. 2019, doi: 10.1109/ARFTG.2019.8637222.

- ▶ I designed BEOL layout, fabricated the BEOL with a TRL kit, performed measurements and data analyses, and wrote the paper.

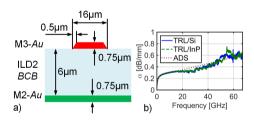

- Paper III: S. Andrić, F. Lindelöw, L. Ohlsson Fhager, E. Lind, and L.-E. Wernersson, "High-Frequency Circuit-Level Characterization of Lateral III-V Nanowire MOSFETs", Manuscript submitted to *IEEE Transaction on Microwave Theory and Techniques*, Mar. 2021.

- ▶ I designed BEOL models, simulated circuits, fabricated the BEOL on the sample, characterized passive components and circuits, carried out data analyses and modelling, and wrote the paper.

- Paper IV: S. Andrić, L. Ohlsson Fhager, and L.-E. Wernersson, "Design of III-V Vertical Nanowire MOSFETs for Near-Unilateral Millimeter-Wave Operation", 2020 15th European Microwave Integrated Circuits Conference (EuMIC), Utrecht, Netherlands, pp. 85–88, Jan. 2021.

- ▶ I simulated the capacitor response, designed and simulated amplifiers, performed data analyses, and wrote the paper.

- Paper V: S. Andrić, L. Ohlsson Fhager, and L.-E. Wernersson, "Millimeter-Wave Vertical III-V Nanowire MOSFET Device-To-Circuit Co-Design", Manuscript submitted to *IEEE Transactions on Nanotechnology*, Jan. 2021.

- ▶ I designed COMSOL models, wrote a Verilog-A code for the device model, carried out all simulations and analyses, and wrote the paper.

- **Paper VI:** A. E. O. Persson, <u>S. Andrić</u>, and L.-E. Wernersson, "MMwave Capacitance Characterization of Ferroelectric MOSCAPs", Manuscript in preparation.

- ▶ I designed the mm-wave MOS capacitor layout, as well as the onchip calibration kit, helped fabricate and measure the sample, analyzed portion of the results, and helped in paper writing.

#### **RELATED WORK**

The following publications are not included in the thesis. It represents the collaborative work within the *Nanoelectronics* group, that I contributed to.

- Paper VII: K.-M. Persson, <u>S. Andrić</u>, S. Ram Mamidala, and L.-E. Wernersson, "Scaling Potential for Vertical ReRAM Crosspoint Arrays", Manuscript in preparation.

- ightharpoonup I designed COMSOL capacitance models, and helped writing the paper.

Paper VIII: O. P. KILPI, <u>S. Andrić</u>, J. Svensson, E. Lind, and L.-E. Wernersson, "High Breakdown Voltage in Vertical Heterostructure III-V Nanowire MOSFETs", Manuscript in preparation. ▶ I analyzed device data, developed COMSOL model and simulated the field-plate response, and wrote part of the paper.

## Acronyms and Symbols

Here, important acronyms, abbreviations, and symbols, which are recurring throughout the thesis, are listed. Some parameters, which only occur in a narrow context, are intentionally omitted; some parameters are used in more than one way, but the context is always explicitly clarified in the corresponding text. Some (compound) units are provided with prefixes to reflect the most commonly encountered notations in the literature.

#### **ACRONYMS AND ABBREVIATIONS**

BCB Benzocyclobutene

BEOL Back-End-Of-Line

CMOS Complementary MOS

CPW Co-Planar Waveguide

CV Capacitance-Voltage

**DC** Direct Current

**DIBL** Drain-Induced Barrier Lowering

**DIM** Device Interface Module

FDSOI Fully Depleted SOI FEOL Front-End-Of-Line

GAA Gate-All-Around

HBT Heterojunction Bipolar TransistorHEMT High Electron Mobility Transistor

**HSQ** Hydrogen Silsesquioxane

ILD Interlayer Dielectric

LNA Low-Noise Amplifier LNW Lateral Nanowire

**LRRM** Line-Reflect-Reflect-Match

MIM Metal-Insulator-Metal

mm-waveMillimeter WaveMNMatching NetworkMOLMiddle(-End)-Of-LineMOMMetal-Oxide-Metal

MOS Metal-Oxide-Semiconductor

MOSCAP MOS Capacitor

MOSFET MOS Field-Effect Transistor

MS Microstrip

mTRL Multiline TRL

RF Radio Frequency

**SOI** Silicon-On-insulator s-parameter Scattering Parameters

**TEM** Transverse Electric-Magnetic

TFR Thin-Film Resistor

TL Transmission Line

TLM Transmission Line Measurement

TRL Thru-Reflect-Line

VNW Vertical Nanowire VS Virtual Source

y-parameter Admittance Parameters

#### LATIN SYMBOLS

| $c$ $C'$ $C_{\rm gx}, C_{\rm gx,p}$ $C_{\rm gx,i}$ $C_{\rm inv}$ $C_{\rm via}$ | $F m^{-1}$ $F, fF \mu m^{-1}, aF/nw$ $F, fF \mu m^{-1}$ $F, aF nm^{-1}$ $F$ | $\approx 3 \times 10^8 \ \mathrm{m  s^{-1}}$ ,speed of light<br>Distributed Line Capacitance<br>Parasitic Gate Capacitance<br>Intrinsic Gate Capacitance<br>Inversion Charge Capacitance<br>Interconnect Via Capacitance |

|--------------------------------------------------------------------------------|-----------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $D_{ m 1D}$                                                                    | ${ m eV^{-1}cm^{-1}}$                                                       | 1D Density-of-States                                                                                                                                                                                                     |

| $E_{\mathrm{G}}$                                                               | eV                                                                          | Energy Band Gap                                                                                                                                                                                                          |

| $f_0$                                                                          | Hz                                                                          | Cut-off Frequency Geometric Mean,<br>Operating Frequency                                                                                                                                                                 |

| f                                                                              | ${ m Hz}$                                                                   | Frequency                                                                                                                                                                                                                |

| $f_{ m FD} \ FoM$                                                              | ${ m HzV^{-1}}$                                                             | Fermi-Dirac Distribution Function<br>Figure-of-Merit of the Transistor                                                                                                                                                   |

| $f_{ m T}$                                                                     | Hz                                                                          | Current Gain Transition Frequency                                                                                                                                                                                        |

| $f_{ m max} \ F_{ m s}$                                                        | ${ m Hz}$                                                                   | Maximum Oscillation Frequency<br>Saturation Factor                                                                                                                                                                       |

| $G, G_T, G_{max}$                                                              | dB                                                                          | Gain, Transducer Gain, Maximum<br>Gain                                                                                                                                                                                   |

| $g_d$                                                                          | $S, mS \mu m^{-1}$                                                          | Output Conductance                                                                                                                                                                                                       |

| $g_m$                                                                          | $S, mS \mu m^{-1}$                                                          | Transconductance                                                                                                                                                                                                         |

| G'                                                                             | ${ m Sm^{-1}}$                                                              | Distributed Line Dielectric Conductance                                                                                                                                                                                  |

| GaN                                                                            |                                                                             | Gallium Nitride                                                                                                                                                                                                          |

| h                                                                              |                                                                             | $\approx 6.626 \times 10^{-34} \text{ J s}, \text{ Planck Constant}$                                                                                                                                                     |

| h<br>HfZrO                                                                     | m                                                                           | Dielectric Layer Height<br>Hafnium-Zirconium Oxide                                                                                                                                                                       |

| $I_{ m D}$ InAs InGaAs InP                                                     | $\rm A,mA\mu m^{-1}$                                                        | Drain Current Indium Arsenide Indium-Gallium Arsenide Indium Phosphide                                                                                                                                                   |

| $k_{ m B}$        |                              | $\approx 1.381 \times 10^{-23} \text{ kg m}^2 \text{ K}^{-1} \text{ s}^{-1},$<br>Boltzmann Constant |

|-------------------|------------------------------|-----------------------------------------------------------------------------------------------------|

| L'                | ${ m Hm^{-1}}$               | Distributed Line Inductance                                                                         |

| $L_{ m eff}$      | $\mathbf{m}$                 | Effective (Reduced) Gate Length                                                                     |

| $L_{ m fp}$       | $\mathbf{m}$                 | Field-Plate Length                                                                                  |

| $L_{ m G}$        | $\mathbf{m}$                 | Gate Length                                                                                         |

| $L_{ m via}$      | Н                            | Interconnect Via Inductance                                                                         |

| $m_0$             |                              | $\approx 9.109 \times 10^{-31}$ kg, Electron Rest Mass                                              |

| $m^*$             |                              | Mass Effective Mass                                                                                 |

| ****              |                              |                                                                                                     |

| $n_{ m f}$        |                              | Number of Gate Fingers                                                                              |

| $n_{ m w}$        |                              | Number of Nanowires                                                                                 |

| NF                |                              | Noise Figure                                                                                        |

| $NF_{ m min}$     |                              | Minimum Noise Figure                                                                                |

| q                 |                              | $\approx 1.602 \times 10^{-19} \mathrm{C}$ , Elemental Charge                                       |

| Q                 |                              | Quality Factor                                                                                      |

| $Q_{\mathrm{x}0}$ | $C, C m^{-2}$                | Channel Inversion Charge                                                                            |

| $R^{\prime}$      | $\Omega\mathrm{m}^{-1}$      | Distributed Line Resistance                                                                         |

| $R_{\mathrm{ON}}$ | $\Omega,\Omega\mu\mathrm{m}$ | On-state resistance                                                                                 |

| $R_{ m S/D}$      | $\Omega,\Omega\mu\mathrm{m}$ | Terminal (Source/Drain) resistance                                                                  |

| s                 |                              | Signal-to-Ground Spacing                                                                            |

| $s_{ m ij}$       |                              | Scattering Parameters                                                                               |

| Si                |                              | Silicon                                                                                             |

| $\mathrm{SiO}_2$  |                              | Silicon Dioxide                                                                                     |

| SiGe              |                              | Silicon-Germanium                                                                                   |

| T                 |                              | Transmission                                                                                        |

| ${ m T}$          | K                            | Temperature                                                                                         |

| $t_{ m b}$        | m                            | Drain Underlap Height                                                                               |

| $t_{ m S}$        | m                            | Vertical Spacer Thickness                                                                           |

| $t_{ m W}$        | m                            | Gate Metal Thickness                                                                                |

| $v_{inj}$         | ${ m ms^{-1}}$               | Injection Velocity, Thermal Velocity                                                                |

| $V_{ m B}$        | V                            | Bias Voltage                                                                                        |

| $V_{ m DS}$       | V                            | Drain-to-Source Voltage                                                                             |

| $V_{ m GS} \ V_{ m T} \ v_{x0}$ | ${\rm V}\\ {\rm V}\\ {\rm ms^{-1}}$ | Gate-to-Source Voltage Threshold Voltage Virtual Source Velocity |

|---------------------------------|-------------------------------------|------------------------------------------------------------------|

| $rac{w}{W_{ m G}}$             | m<br>m                              | Transmission Line Width<br>Gate Width                            |

| $y_{ m ij}, Y_{ m ij}$          | S                                   | Admittance Parameters                                            |

| $Z_0 \ Z_{ m opt}$              | $\Omega \ \Omega$                   | Characteristic Impedance Optimum-Noise Matching Impedance        |

#### **GREEK SYMBOLS**

| $\alpha \\ \alpha$                                                                                                          | $\mathrm{dB}\mathrm{mm}^{-1}$ | Voltage Scaling Factor<br>Transmission Line Attenuation                                                                                                                       |

|-----------------------------------------------------------------------------------------------------------------------------|-------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| eta eta                                                                                                                     | $\rm radmm^{-1}$              | Saturation Factor Fitting Parameter<br>Transmission Line Phase Constant                                                                                                       |

| $egin{array}{l} arepsilon(0) & & & & \ arepsilon_0 & & & \ arepsilon_{ m eff} & & & \ arepsilon_{ m r} & & & \ \end{array}$ | e V                           | Top-Of-the-Barrier Energy $\approx 8.85 \times 10^{-12} \; \mathrm{F  m^{-1}}, \; \mathrm{Vacuum \; Permittivity}$ Effective Dielectric Constant Relative Dielectric Constant |

| $\Gamma \ \Gamma_{ m opt}$                                                                                                  |                               | Reflection Coefficient<br>Noise-Optimum Reflection Coeffi-<br>cient                                                                                                           |

| $\kappa$                                                                                                                    |                               | Relative Permittivity                                                                                                                                                         |

| $\lambda$                                                                                                                   | m                             | Mean-Free Path, Guided Wavelength                                                                                                                                             |

| $\mu,\mu_{\mathrm{e}}$                                                                                                      | $\rm m^2V^{-1}s^{-1}$         | Electron Mobility                                                                                                                                                             |

| $\omega$                                                                                                                    | $\rm rads^{-1}$               | $=2\pi f$ , Angular Frequency                                                                                                                                                 |

| $\pi$ $\gamma$                                                                                                              | $\mathrm{m}^{-1}$             | $\approx 3.14159$ , Mathematical constant Propagation Constant                                                                                                                |

#### **FUNCTIONS AND OPERATORS**

- Im(·) Imaginary part

- $ln(\cdot)$  Natural Logarithm

# **INTRODUCTION**

### Fundamentals of RF Circuits

UR modern world is built around the fundamentals of communication using radio signals. Such communication systems enable us to transfer a large amount of information over vast distances.

The system itself is built from circuits, electronic units with a specialized functionality. The first section of this chapter addresses the perspective of the design of radio signal-handling circuits using an electronic transistor, with a focus on frequency of operation. The next section dives into the core of many modern radio circuits out there - the nanoscale *Metal-Oxide-Semiconductor Field Effect Transistor* (MOSFET). Some of the basic properties are addressed, including transistor's nanoscale geometries. The chapter ends with a transistor state-of-the-art performance benchmark, which also provides a motivation for this thesis.

#### 1.1 ABOUT CIRCUIT DESIGN

The electronic circuit represents a set of electronic components that can control electric impulses, or signals, which are a part of the electromagnetic spectrum, and are described as travelling waves. The spectrum of interest for electronic applications encompasses radio waves and microwaves, typically found at wavelengths between a few hundred km, down to a few µm, and correspond to frequencies ranging from a few kHz up to several hundred GHz. Various materials are used to capture specific properties of these waves, and to process them without distortion, or loss of the information they carry. These materials will, ultimately, build individual electronic components and with them, the electronic circuits and systems.

The core of these electronic circuits is an active component - an electronic transistor. Typically, it is made from a semiconducting material, and allows for transformation of the input electronic signals into the stronger, output signals. The effect is known as signal amplification. It revolutionized the world of electronics since this functionality proved to be an efficient way to transform signals and to manipulate them through integration of many transistor components. Electronic transistors are three- or four-terminal components, where one set of terminals is used as a controlling input, while others are used for the generated desired output. The electronic signals transistors manipulate are electrical current or voltage signals, or power waves at high frequencies. In essence, transistors are behaving like non-ideal current switches, and their non-idealities give rise to a range of effects that have been a subject of study for decades.

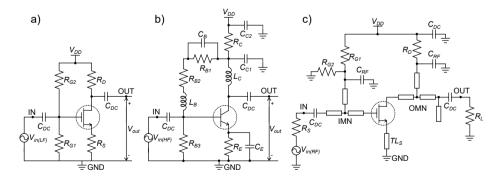

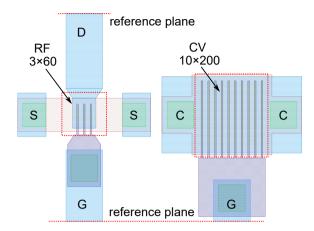

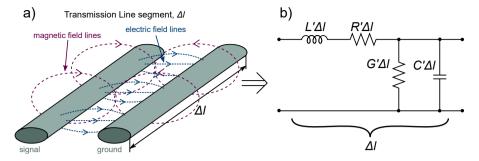

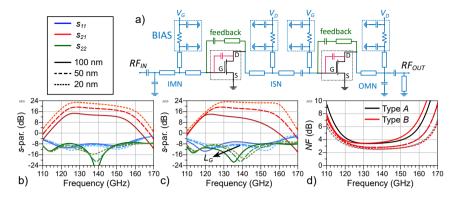

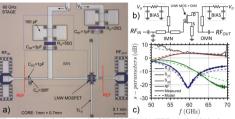

A representative circuit that utilizes electronic transistors will be designed differently based on the application for which the circuit is intended, or at which end of the frequency spectrum it operates. In principle, a combination of active components (electronic transistors), and various passive components (resistors, inductors, capacitors, transformers, and transmission lines), provide a specific functionality to the circuit. Fig. 1.1 shows some typical design examples of signal amplifiers for different frequency ranges, showcasing differences in design procedures at different operation frequencies. Fig. 1.1(a) illustrates the simplest case - a low frequency circuit, where the resistance values control the circuit operation. In the next stage (Fig. 1.1(b)), more reactive components will be needed to suppress the phase shift in the signal, which starts to

**Figure 1.1:** An example of various circuits with an electric transistor: a) low-frequency (kHz range), b) intermediate frequency (MHz range), and c) high frequency (GHz range) circuit. All circuits show arrangement of different components, to achieve signal amplification, with each version being more complex, ultimately resulting in distributed components (transmission line segments).

appear as the frequency of operation increases. Therefore, inductors are used. Additionally, an effort to stabilize and isolate the circuit is made, with added capacitors and a resistive feedback loop. Finally, the high-frequency design is the most interesting, and the most sensitive to the effects addressed in the Fig. 1.1(b). Here, distributed components are used, those that allow for amplitude and phase change along the dimensions of the component. Fig. 1.1(c) shows an implementation with distributed transmission line components. The distributed effects will be addressed in detail in the following chapters.

#### 1.2 NANOSCALE MOSFET AS A RADIO DEVICE

At the core of many modern integrated radio circuits we find the nanoscale MOSFET, a device with some unique properties. Although the device concept was developed almost a century ago, it was brought to life only some 60 years ago with several discoveries following discrete transistor components [1–5]. An integrated version has been introduced to the world in '74, marking an important milestone for scaled devices and circuits, as well as for computing and signal processing [6, 7]. Following these first findings, an industrial development has followed hand-in-hand, enabling our modern society to benefit from the technology ever more. Particularly, mobile, or wireless communication development has come alive with the use of these integrated devices. The basic properties of modern nanoscale MOSFETs are given in the following subsections.

#### 1.2.1 MOSFET BASIC DESIGN AND OPERATION

The nanoscale MOSFET is created by nanoengineering a device structure that contains three, or four terminals named gate, source, drain, and bulk (or body). In the device core is the semiconducting channel. The gate, and the body control the channel electrostatically, through capacitive coupling, and are considered input terminals. The output, that are the source and drain terminals, are resistively coupled, and conduct current based on the state of the input terminals. This significant difference in the coupling behavior of the input and output regions of the device results in a signal manipulation that is heavily based on the properties and dimensions the semiconductor material, as well as on how the material is integrated into a nanoscale device.

The MOSFET operation relies, among other things, on doping of the semiconductor by *impurities*. Introducing atoms of the specific elements into the semiconductor crystal will create an excess of charges that can

contribute to a reduced resistance. Source and drain terminals of the radio MOSFET are typically in excess of electrons, that participate in the electron transport in the device. Such devices are named *n-type* MOSFET, or nMOSFET for short. Fig. 1.2(a) shows such a MOSFET with doped regions integrated into the semiconductor. The capacitive coupling of the input terminals is achieved via a gate insulator, separating the channel and the gate electrode. An alternative approach is to integrate a metal electrode directly on the pure (undoped) semiconductor, creating an energy barrier, arising due to the difference in electron affinity between the materials (Schottky barrier). Both technology options exert an electric field over the channel and thereby control the channel conductivity by attracting or repulsing charges from the gate-semiconductor interface.

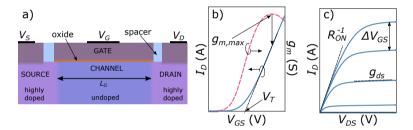

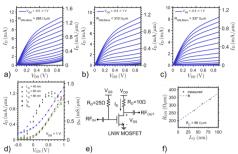

Figure 1.2: Overview of basic MOSFET design and operation: a) device illustration, showing highly doped drain and source region, channel, gate oxide and contact metals. b) Transfer plot of drain current and transconductance, and c) output plot of typical high-performance nanoscale MOSFET, with important parameters noted.

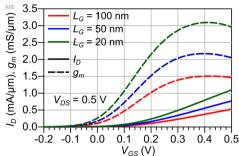

The current flow in the drain terminal, known as drain current  $I_D$ , is used to characterize the device operation. Fig. 1.2(b) depicts such a case, and it is known as a transfer plot, since it shows the dependency of  $I_D$  on the input gate-source voltage  $V_{GS}$ , for a set of drain-source voltage  $V_{DS}$  values. Two different states are identified: the off-state, where the current level is low and has an exponential behavior, and the on-state, where the current has a significant value and changes in a quadratic/linear relation. The border between these two states of operation is characterized by a threshold voltage, or  $V_T$ . The most important metric in radio device is the slope of  $I_D$ , or transconductance  $g_m$ . It is a derivative of the drain current with respect to the gate voltage, or  $g_m = \partial I_d/\partial V_{gs}$ , and is a measure of the amplification capabilities of radio signals in a MOSFET.

If  $I_D$  is measured at different  $V_{DS}$ , while  $V_{GS}$  remains constant, the output characteristics can be obtained, as shown in Fig. 1.2(c). Two distinct regions of operation are identified in this case as well. They

are named the triode (or resistive) region, and the saturation region. The resistive region is observed for small  $V_{DS}$ , where the current-voltage relationship is linear. The value of this resistance, the  $R_{ON}$ , is determined by the gate voltage, and its value will saturate as  $V_{GS}$  increases. In the case of higher  $V_{DS}$ , the current flattens out. The electric field on the drain side pinches off the conduction in the channel and creates a barrier that electrons cannot overcome, thus flattening the current. More prevalent nowadays, in devices with short gate-length, is that the channel pinch-off does not happen since the high electric field causes electrons to scatter in the channel, thus limiting their velocity (velocity saturation). The pinch-off occurs mostly for low  $V_{GS}$ . The ability for current to remain constant is a measure of the gate electrostatic control over the channel. The slope of the current in this region, known as output conductance, or  $g_d = \partial I_d / \partial V_{ds}$ , is also a measure of the quality of the device. The MOSFET intrinsic gain, or self-qain  $q_m/q_d$ , as well as transconductance efficiency, or  $q_m/I_D$ , are also important metrics in the analog and radio MOSFET, and determine the extent of the device operation.

#### 1.2.2 SCALING OF RADIO MOSFETS

To improve on the MOSFET density and performance, reducing the device size is a proven method. The rules for device scaling are known as *Dennard* scaling rules [8]. Together with the now famous Moore's law, they formed a basis for defining scaling trends for future technology nodes, from an economic, as well as technological perspective [9]. According to Dennard scaling rules, the device dimensions and the operating voltages are scaled by a factor, effectively reducing the power consumption, while improving on the device performance [8]. However, the power density in the device would dramatically increase. Therefore, after almost two decades, this original rule has been replaced with an alternative approach that does not scale the device power density [10]. The optimization of the source/drain contacts, a gate insulator dielectric, and spacers was addressed instead. The electrostatic control of the channel is challenged in every iteration of gate length reduction, and eventually, the gate starts losing control over the channel potential due to penetrating electric field from the drain terminal, commonly known as a short-channel effect. This makes the device intrinsic gain, a crucial factor for analog operation, diminish.

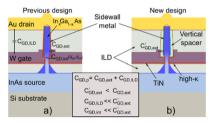

In Fig. 1.3, geometry variations are depicted, showcasing considered approaches to solving scaling and performance bottlenecks of today. MOS-FETs are illustrated with regions consisting of highly-doped semiconductor contacts, the intrinsic channel surrounded by a gate insulator (high- $\kappa$ ), and a patterned gate contact metal cover. Device spacers, drain/source

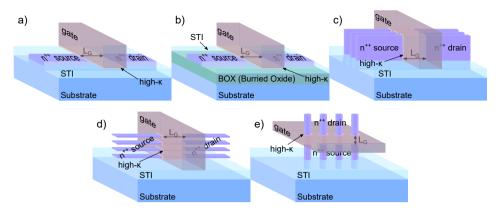

**Figure 1.3:** Illustration of nanoscale MOSFET structure, showing integrated transistor with relation to the substrate, consisting of  $n^+$  contacts, intrinsic channel (marked with gate length  $L_G$ ), high- $\kappa$  insulator and gate metal, isolated with STI. MOSFETs are shown in various geometries: a) bulk, or planar, b) SOI MOSFET, c) FinFET, d) lateral GAA MOSFET, and e) vertical GAA, or nanowire MOSFET.

contact metals and enveloping low- $\kappa$  dielectric (passivation) are omitted, for clarity. The two planar approaches, shown in Fig. 1.3(a-b), are bulk, and Si-On-Insulator (SOI) MOSFET geometry, respectively. They rely on semiconductor having a direct connection to the substrate, or are attached to the substrate with an insulating layer, known as a buried oxide, and isolated with a shallow-trench isolation (STI). The next stage in device geometric development are, among others, lateral devices, which utilize the existing planar technological solutions. They include the FinFET/trigate MOSFET (Fig. 1.3(c)), and lateral gate-all-around MOSFET (stacked nanosheets, Fig. 1.3(d)) [11,12]. The semiconductor channel is shaped as a very thin semiconductor fin and wrapped from more than one side with gate metal. The gate electrostatic control is then greatly improved, enabling further scaling. Recently, the FinFETs/tri-gate MOSFETs further show improvement in the high-frequency performance, which will be discussed in the next subsection.

Finally, the ultimate scaling trend leads to a semiconductor channel formed like a nanowire, possibly shaped from a thick semiconductor layer or grown as a wire on the semiconducting or insulating surface. They are known as vertical gate-all-around (GAA), or nanowire MOSFETs, and are shown in Fig. 1.3(e). The semiconductor material itself consists of a finite number of atoms, and the device operation has a strong influence of quantum effects that improve on performance. The vertical nanowires are

considered as the ultimate device scaling paradigm. They offer additional degrees of freedom, as the height does not limit the size of device contacts, which need to be restricted in planar and lateral device technologies. The vertical geometry should offer improved electrostatic control in extremely scaled devices, which should enable the state-of-the-art high-frequency devices as well. However, the exact path for device design is still under exploration and its performance limits are yet to be discovered. This thesis will consider a specific flavor of these devices and reveal some of their unique capabilities.

#### 1.2.3 STATE-OF-THE-ART RADIO MOSFETS

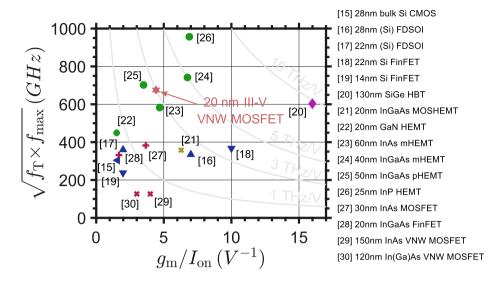

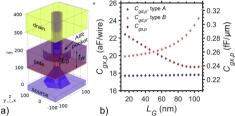

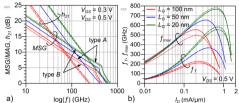

The evaluation of high-frequency MOSFETs and other devices is compared by analyzing and comparing some specific quality-controlling metrics. Regarding the electrostatic control and the material quality, we discuss values of transconductance  $(g_m)$ , output conductance  $(g_d)$ , on-resistance  $(R_{on})$ , and on-current  $(I_{on})$ , among others. Additionally, some highfrequency metrics are considered as well, such as current-gain transition frequency  $(f_T)$ , and maximum oscillation frequency  $(f_{max})$ . Details about derivation of these important metrics are given elsewhere [13, 14].

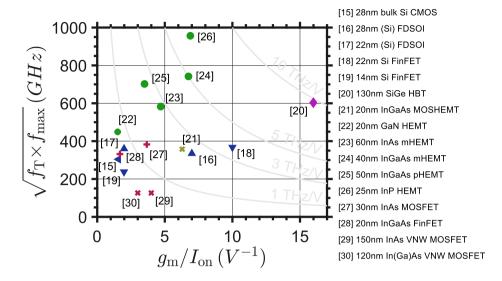

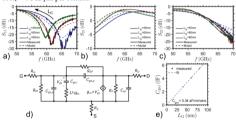

One figure of merit that is provided in most literature is the product of frequency and transconductance efficiency,  $FoM = f_0 \cdot g_m/I_{on}$ , and is given in THz/V. Here, the cut-off frequency geometric mean is taken, or  $f_0 = \sqrt{f_T \cdot f_{max}}$ , instead of individual cut-off frequency contributions. The transconductance efficiency allows for evaluation of the effectiveness of the charge transport in the semiconductor channel, while the cut-off frequencies reflect on device structural design. Fig. 1.4 shows a high quality gate control observed for Si-based materials, which exhibit some of the highest values. Heterojunction bipolar transistors (HBTs) are known for a having high transconductance as a measure of collector current (note that current gain,  $\beta$  is used as a metric in HBTs), hence they exceed all other devices in this particular metric. Their structural design allows them to minimize parasitic capacitances, and achieve high cut-off frequencies, representing the best FoM of nearly 10 THz/V. The RF-optimized Si MOSFET technologies show good FoM as well, going above 3 THz/V.

The III-V materials are very attractive for the transistor implementation, since heterostructure combinations provide flexibility in the device design. Among these, high electron mobility transistors (HEMTs) excel in their high-frequency performance, reaching cut-off frequency values above 1 THz. Their control of electrostatic coupling is not as good as in the Si-based transistors, but they benefit from III-V materials in another way - through high carrier velocity, giving them high currents and  $g_m$  values.

**Figure 1.4:** Different technologies high frequency quality measure - cut-off frequencies geometric mean w.r.t. device efficiency amplification for: Si technology [16–20], represented by blue '+' sign, the representative SiGe HBT technology [21], shown as pink diamond, a III-V MOSHEMT technology [22], shown as brown square, III-V HEMT technology [23–27], shown as green circles, and III-V MOSFET technology [28–31], represented by a red '×' sign. Thin grey lines show performance limit where figure of merit reaches 1, 3, 5, and 10 THz/V.

Therefore, their FoM is significant, even exceeding that of industrial-scale Si devices, with values well above 5 THz/V. Finally, III-V MOSFETs represent an experimental group of devices whose performance limits are vet to be assessed. These devices combine the Si MOSFET superior electrostatic control, with the III-V materials' transport properties and a structural engineering that enables high  $g_m$  and cut-off frequencies. Additionally, the III-V MOSFETs do not suffer from excessive gate leakage when scaled, like HEMTs, or from high DC power consumption, like HBTs. Therefore, a scaled III-V MOSFET is a viable candidate to compete with established technologies in terms of performance. The development of nanowire MOSFETs using III-V materials in scaled geometries have in fact resulted in some of the best individual performance metrics [15]. Their reported high-frequency performance currently is below 1 THz/V and it is challenging to optimize due to complicated device processing. Therefore, a structural optimization is needed to obtain all necessary performance metrics at the same time, and advance their high-frequency performance.

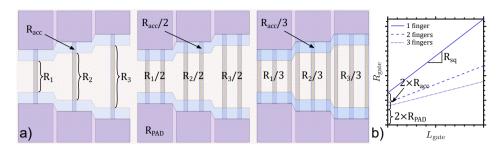

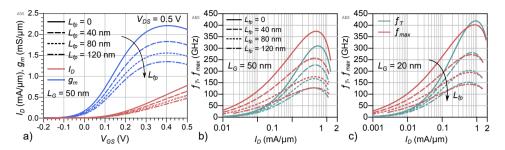

# III-V NW MOSFET Technology Platform

HE effort in creating a novel nanowire MOSFET technology platform requires many aspects of device design to be combined. The main contribution to such a platform is an accurate description the device structure. To support this effort, specific test structures need to be designed and evaluated separately. Such test structures we call process monitor structures. They are essentially semi-completed devices, with an added probing pad or similar, which provide evaluation of a specific device parameter. Typically, we need to know resistances in the source and drain access regions and separate them from the resistance in the MOSFET channel. Or we need an information about the gate metal resistance, in case we need to assess high-frequency data. This information then feeds into a MOSFET compact model, that is the core of the platform. The following chapter contains the description the nanowire MOSFET 1D channel transport and the compact model, as well as individual structures used in the III-V nanowire MOSFET technology platform.

#### 2.1 NANOWIRE MOSFETS - III-V MATERIALS AND 1D TRANSPORT

The assessment and references from Chapter 1 introduce us to the world of the nanoscale MOSFETs. The interest in these structures has developed over about two decades, where the International Roadmap for Devices and Systems (IRDS) is establishing the future device development strategies [32]. The IRDS report states that device scaling can be maintained with nanowire technology and 3D integration of devices. This is motivated by the device electrostatic control, stemming from the GAA approach, as described in Chapter 1. Furthermore, IRDS states that such scaled

structure may be facilitated with alternative III-V materials [33,34]. These include compounds consisting of group III elements (Al, Ga, In), and group V elements (N, P, As, Sb) in the Mendeleev periodic table of elements.

The III-V compounds are attractive based on their electronic properties. A basic set of material parameters that are defined by the crystal structure and electron interactions within the crystal include the effective mass  $m^*$  and energy band gap  $E_g$ . From these, we derive other useful parameters, such as the injection velocity  $v_{inj}$ , the carrier mobility  $\mu$ , and ultimately, the mean-free-path  $\lambda$ . The difference in injection velocity and mean-free-path for III-V materials is quite significant, when compared to more conventional materials with the same  $E_g$ , used in the large-scale industrial processes, such as group IV elements (Si, SiGe). This means that electrons are able to travel large distances in the crystal lattice without interacting with their surroundings (crystal lattice, impurities, other electrons). These material parameters are summarized in Table 2.1.

The presented values clearly show that III-V materials have an intrinsic advantage. Their low effective mass, coupled with a very high electron mobility, and more than twice of the injection velocity, makes them very attractive in electronic devices and circuits. The downside is the relatively low abundance of some materials (i.e. In is a scarce element), and their challenging implementation in industrial process schemes, since they are typically brittle materials. This does not prevent them from finding their place in niche applications, where conventional, Si-based technologies have

**Table 2.1:** Room temperature bulk material parameters for representative semi-conductors and semiconductor compounds [35]. Note that these values represent theoretical values and are typically lower in fabricated devices.

| Materials                                                       | Si   | SiGe <sup>a</sup> | InAs  | InGaAs <sup>b</sup> | InP   | $\mathrm{GaN^c}$ |

|-----------------------------------------------------------------|------|-------------------|-------|---------------------|-------|------------------|

| Effective electron mass $m^*/m_0$                               | 0.26 | ~0.26             | 0.023 | 0.041               | 0.08  | 0.13             |

| Energy band-gap $E_g$ (e V)                                     | 1.12 | 1.005             | 0.354 | 0.74                | 1.344 | 3.2              |

| Electron injection velocity $v_{inj}~(\times 10^5 \text{ m/s})$ | 2.3  | 2.4               | 7.7   | 5.5                 | 3.9   | 2.5              |

| Electron mobility $\mu_e$ $(\text{cm}^2/\text{V s})$            | 1400 | 2600              | 40000 | 12000               | 5400  | 1000             |

$<sup>^{</sup>a}28\%$  Ge [36];  $^{b}In_{0.53}Ga_{0.47}As$ ;  $^{c}zinc$  blende.

not yet shown sufficient performance (such as the high-frequency operation, see Fig. 1.4). Ultimately, one could think about integration, and aligning the III-V materials with a more conventional Si fabrication scheme. Such integration would benefit III-V materials as they rely on the Si platform for stability and large-scale integration, and it would benefit Si technology, on the other hand, by using the advantageous properties of the III-V materials.

# 2.1.1 PHYSICS OF NANOWIRE MOSFETS

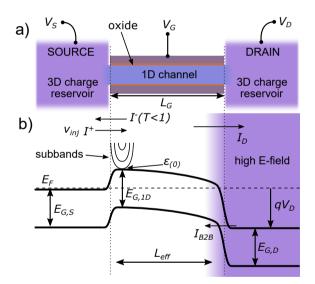

We begin describing nanowire geometry with the evaluation of the channel structure, where we can assume that electrons can traverse without scattering with the crystal lattice, while the total amount of electrons participating in the transport is controlled by raising, or lowering the energy barrier with the gate potential. This effect is known as ballistic transport, and is illustrated in Fig. 2.1. Under such conditions, the drain

Figure 2.1: a) Schematic illustration of GAA nanowire MOSFET core, including 3D source and drain regions (electron reservoirs). The 1D channel is wrapped by an oxide and a gate metal. b) Energy landscape of source, drain, and channel regions, showing position of Fermi level  $E_F$ , conduction bands, and valence bands for all semiconductor regions, including the high electric field drain region penetrating the channel. Subband splitting is shown as well, together with top-of-the-barrier energy level  $\varepsilon_{(0)}$ . Drain current  $I_D$  is a combination of incident  $I^+$  and reflected  $I^-$  current, due to finite transmission probability T. The band-to-band tunneling current  $I_{\rm B2B}$  is shown as well, and can be suppressed with larger bandgap material on the drain side.

current of the barrier-controlled device can then be expressed as [13, 37]:

$$I_D = T(I^+ - I^-) = \frac{2q}{h} \int_E T(E)M(E)[f_{FD,s}(E) - f_{FD,d}(E)] dE, \quad (2.1)$$

where  $f_{FD}(E)$  is the Fermi-Dirac distribution function of the source and drain regions, and q and h are physical constants. The term T(E) is known as transmission and describes how ballistic the device is, and is directly related to the scattering rate. It depends on the carrier mean-free path  $\lambda$ , and is described by:

$$T = \frac{\lambda(E)}{\lambda(E) + L_{eff}} \quad (2.2a) \quad \text{where } L_{eff} = \begin{cases} L_G, & \text{small } V_{DS} \\ \frac{k_B T}{q V_{DS}} L_G, & \text{large } V_{DS}. \end{cases} \quad (2.2b)$$

where  $L_{eff}$  is the gate length correction for high drain bias, and represents the portion of the channel where scattering reflection can still occur. The transmission changes with  $V_{DS}$  since electrons are not able to back-scatter under the presence of the high electric field in the channel region close to the drain area. Even if they scatter, they still constitute a current since they are not able to return to the source region, as shown by high electric field area and bent energy bands close to the drain reservoir, in Fig. 2.1. The mean-free-path will change as well, but is typically assumed as energy-independent. The transmission relation will be close to unity in a case where  $\lambda >> L_{eff}$ , while in quasi-ballistic devices,  $\lambda \approx L_{eff}$ , and transmission has values between 0.3 and 0.8.

The M(E) term in (2.1) represents the number of available charge energy states that can participate in the transport, and is directly proportional to 1D density of states (DoS). It is given by [37,38]:

$$M(E) = L_G \frac{h}{4} v_{inj} D_{1D}(E),$$

(2.3)

where  $L_G$  is the MOSFET gate length, and  $D_{1D}(E)$  represents the 1D density-of-states (DoS), given as:

$$D_{1D}(E) = \frac{1}{\pi \hbar} \sqrt{\frac{2m^*}{E - \varepsilon_{(0)}}}, \qquad (2.4)$$

where  $\hbar = h/2\pi$  is the reduced Planck constant, and  $\varepsilon_{(0)}$  is a lowest subband energy level or top of the barrier. From (2.3) and (2.4), M(E) gives us 1 for a single occupied subband in a scaled nanowire (few nm

in diameter) at zero temperature, while for a typical nanowire (10s of nm), the bands are positioned closer together, and smeared in values due to temperature dependence of the Fermi-Dirac distribution function, thus making this number larger. Note that the expression (2.4) is based on parabolic band approximation, which is typically correct only for a small energies and wave vectors. A more rigorous treatment of these expressions would include corrections or even numerical solutions, but it is outside of the scope of this thesis.

#### 2.1.2 COMPACT MODELLING OF NANOWIRE MOSFETS

For the purpose of device evaluation and circuit design, a device compact model is developed, instead of rigorously evaluating MOSFET operation based on physical expressions. The strategy behind compact modelling should always be to enable use of a device model in a variety of simulation environments. It needs to represent the semiconductor behavior in a sufficiently accurate manner, as well as to account for the environment surrounding the device. Furthermore, the compact models are verified in circuit design and implementation, where feedback is provided to both device design and to the compact modelling. There are many models that consider the physical aspects of device behavior, and they rely on many parameters to describe this behavior accurately (i.e. SPICE models). Therefore, the selection of compact modelling environment is essential in understanding the device operation and should be related to the physical device description.

The compact model used to describe nanowire MOSFETs in this thesis is based on physical parameters described in the previous subsection. It takes into account all the aspects of the ballistic transport as well as dimensioning the device channel, and is known in the literature as *virtual-source model* (VS model) [39–42]. The current description is similar to the relation (2.1):

$$I_D = W_G Q_{ix0}(V_{GS}, V_{DS}) v_{x0} F_s,$$

(2.5)

where  $W_G$  is gate width,  $Q_{ix0}$  is total voltage-dependent channel inversion charge,  $v_{x0}$  is the carrier velocity at the 'virtual source', and  $F_s$  is the smoothing transition function from linear region to saturation region. Comparing (2.1) to (2.5), we can easily come to the conclusion that the virtual source velocity is the injection velocity,  $v_{inj}$ , scaled by the transmission factor T, while channel inversion charge will be given as:

$$Q_{ix0} = -q \int_{E} D_{1D}(E) f_{FD}(E) dE \approx n C_{inv} (V_{GS} - V_{T})^{\alpha}, \qquad (2.6)$$

where n is a subthreshold slope dependent parameter,  $C_{inv}$  is on-state (strong inversion) gate capacitance, and  $\alpha$  is a parameter that has value close to 1 in device on-state, in case of most short-channel devices. The channel inversion charge  $Q_{ix0}$  depends on  $V_{DS}$ , through threshold voltage,  $V_T = V_{T0} - DIBL \cdot V_{DS}$ . Finally, the smoothing function  $F_s$  is a saturation- and mobility-dependent function that describes transition between different regimes of operation:

$$F_s = \frac{V'_{DS}/V_{Dsat}}{(1 + (V'_{DS}/V_{Dsat})^{\beta})^{1/\beta}},$$

(2.7)

where  $V_{Dsat} \sim v_{x0}L_G/\mu$  is a gate length and mobility dependent function that scales the saturation velocity. Here, the mobility  $\mu$  is not related to the material-based parameter  $\mu_e$ , as in a classical diffusive transport, but should be seen as a fitting parameter. The voltage  $V_{DS}^{'}$  is intrinsic drain-source voltage, excluding the device access resistances ( $V_{DS}^{'} = V_{DS} - I_D \cdot (R_S + R_D)$ ), while  $\beta$  is another fitting factor that sets the shape of the device output characteristic. Using these simple expressions, the device complex characteristics are easily described, using only a few fitting parameters. Such a model implementation in circuit environment becomes rather straightforward.

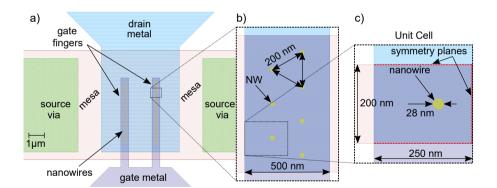

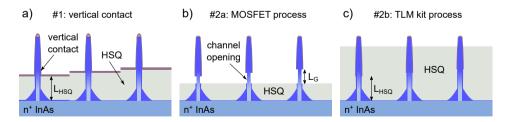

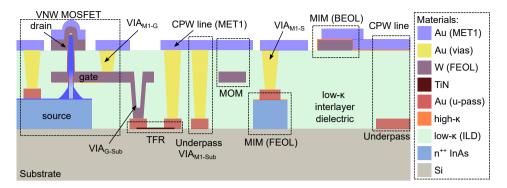

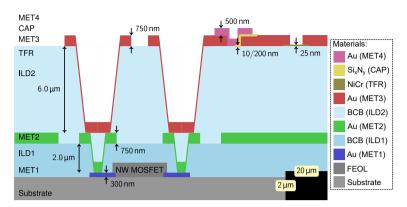

# 2.2 LAYOUT OF NANOWIRE MOSFET

A very important segment in building the technology platform, aside from the compact modelling of the device, is the layout design of the device itself. A standalone device layout with electrical contacts is known as front-end-of-line (FEOL), while the interconnect stack that is used to realize circuit functionality is named back-end-of-line (BEOL). The smart use, and scaling of these layouts has always been an advantage of Si CMOS process. [43,44]. The density rules are introduced, to limit device variability and increase yield. However, these density rules drive the reduction in the contact area in FEOL, and increased parasitics in scaled BEOL, which may negatively impact the device high-frequency performance. High-frequency MOSFETs therefore require less stringent density rules to achieve optimum high-frequency operation. Here, a specific process flow and layout of III-V vertical nanowire (VNW) MOSFETs is discussed, being a rather unique approach to device design.

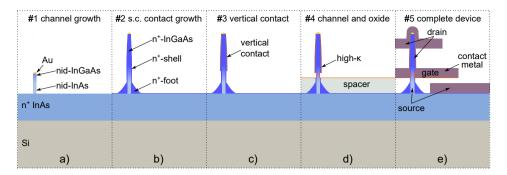

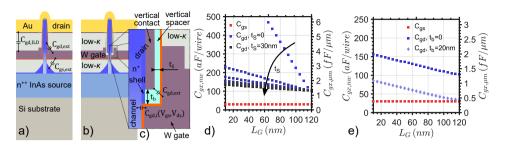

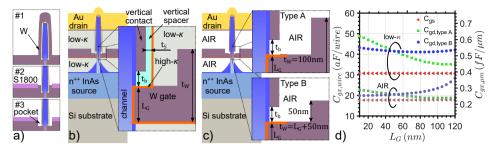

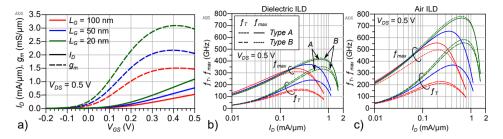

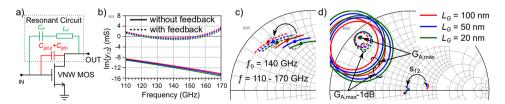

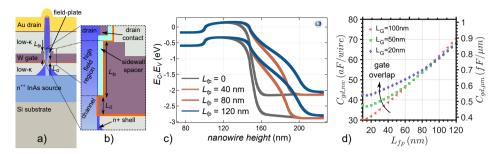

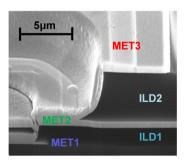

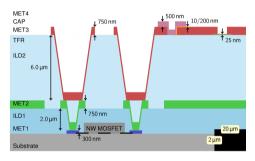

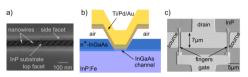

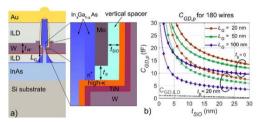

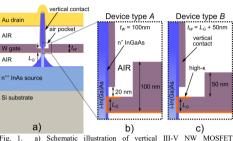

The III-V VNW MOSFET process flow starts with an epitaxial growth facilitated by a catalyst (Au). The intrinsic nanowire segment grows from underneath the Au island, while the catalyst size determines the diameter

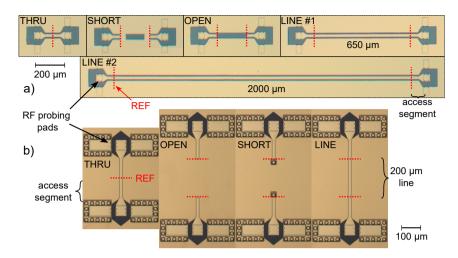

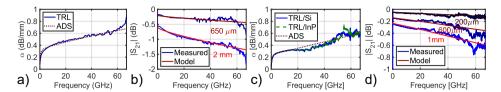

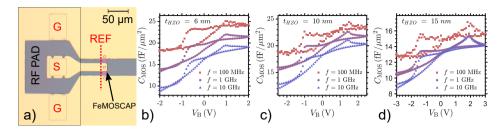

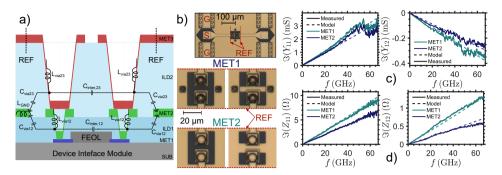

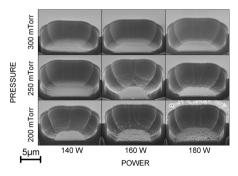

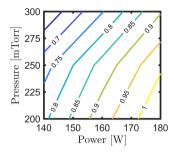

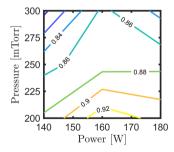

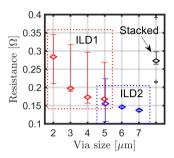

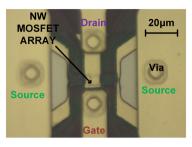

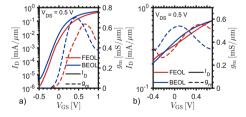

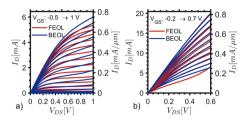

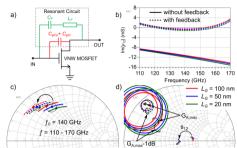

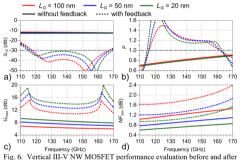

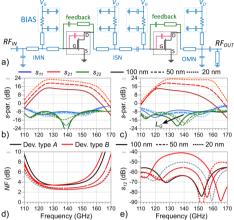

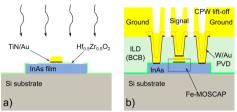

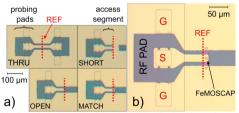

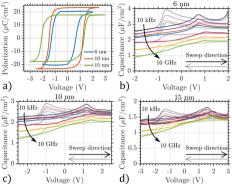

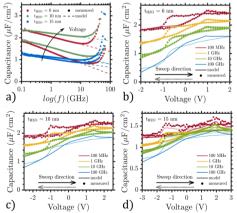

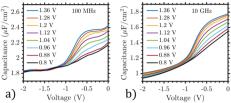

Figure 2.2: A general process flow of III-V VNW MOSFETs: a) formation of InAs and graded InAs/InGaAs segment, b) semiconductor contact overgrowth (Sn-doped InGaAs) - formation of the shell and nanowire foot, c) deposition of vertical contact (improved contact resistance), d) removal of highly-doped shell from channel region and gate dielectric deposition, and e) metallization, and complete outlook of device with terminal contacts.