# LUND UNIVERSITY

#### Semiconductor Nanoelectronic Devices Based on Ballistic and Quantum Effects

Sun, Jie

2009

#### Link to publication

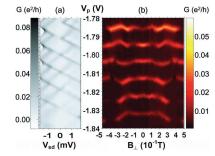

Citation for published version (APA):

Sun, J. (2009). Semiconductor Nanoelectronic Devices Based on Ballistic and Quantum Effects. [Doctoral Thesis (monograph), Solid State Physics]. Lund University (Media-Tryck).

Total number of authors:

#### General rights

Unless other specific re-use rights are stated the following general rights apply:

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights. • Users may download and print one copy of any publication from the public portal for the purpose of private study

or research.

You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal

Read more about Creative commons licenses: https://creativecommons.org/licenses/

#### Take down policy

If you believe that this document breaches copyright please contact us providing details, and we will remove access to the work immediately and investigate your claim.

LUND UNIVERSITY

**PO Box 117** 221 00 Lund +46 46-222 00 00

# Semiconductor Nanoelectronic Devices Based on Ballistic and Quantum Effects

Jie Sun 孙 捷

**Doctoral Thesis**

Division of Solid State Physics Department of Physics Lund Institute of Technology Lund University

### Semiconductor Nanoelectronic Devices Based on Ballistic and Quantum Effects

Jie Sun

孙 捷

Principal Supervisor: Prof. Hongqi Xu

Division of Solid State Physics Department of Physics Lund Institute of Technology Lund University Sweden 2009

Akademisk avhandling som för avläggande av teknisk doktorsexamen vid tekniska fakulteten vid Lunds Universitet kommer att offentligen försvaras vid Fysiska Institutionen, hörsal B, måndagen den 25 september 2009 kl. 13.15. Fakultetsopponent: Prof. Jonathan Bird, Electrical Engineering Department, University at Buffalo, NY, USA.

Division of Solid State Physics Department of Physics Lund Institute of Technology Lund University P.O. Box 118 S-22100 Lund Sweden

Copyright © Jie Sun, 2009 ISBN 978-91-628-7850-4 Printed in Sweden by Media-Tryck, Lund July 2009

To my wife ——Chunli Yan

### Abstract

As current silicon-based microelectronic devices and circuits are approaching their fundamental limits, the research field of nanoelectronics is emerging worldwide. With this background, the present thesis focuses on semiconductor nanoelectronic devices based on ballistic and quantum effects. The main material studied was a modulation doped  $In_{0.75}Ga_{0.25}As/InP$  semiconductor two-dimensional electron gas grown by metal-organic vapor phase epitaxy. The thesis covers mainly three types of devices and their twofold integration: in-plane gate transistors, three-terminal ballistic junctions and quantum dots. Various advanced nanofabrication tools were used to realize the devices, such as electron beam lithography, focused ion beam lithography and atomic layer deposition. The theories behind the analysis of the experimental data include principles of field effect transistors, the Landauer-Büttiker formalism, the constant interaction model, etc.

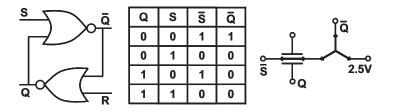

The principles of in-plane gate transistors can be explained by a classical theory. The source, drain, one-dimensional channel and two side gates were in the same plane; a setup that can be obtained by single step lithography. The gating efficiency of the two independent gates was voltage-dependent, which resulted in a simplified circuitry for implementing a logic function. At room temperature, an SR latch with a signal gain of  $\sim 4$  was realized by the integration of two in-plane gate transistors.

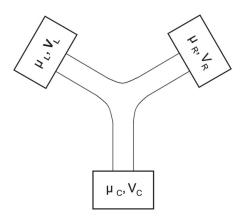

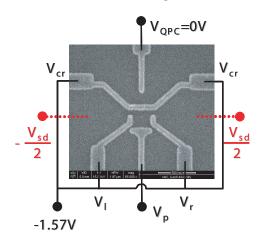

Three-terminal ballistic junctions are nonlinear devices based on ballistic electron transport. When two terminals are applied with voltages, the third terminal will output a voltage close to the more negative voltage in the two inputs, as opposed to a simple average of the two. From numerical calculations, this ballistic effect persists up to room temperature. Three-terminal ballistic junctions are so robust that nonlinearity is observable in asymmetric devices and relatively large devices. They can be fabricated on several materials by assorted techniques. The junctions find their applications in analogue frequency mixers, phase detectors and digital SR latches and the circuits are simpler than conventional designs. The intrinsic speed of the devices is in the GHz or THz regime by virtue of the ballistic transport. It is believed that as-built junctions have a potential as building blocks in future nanoelectronics.

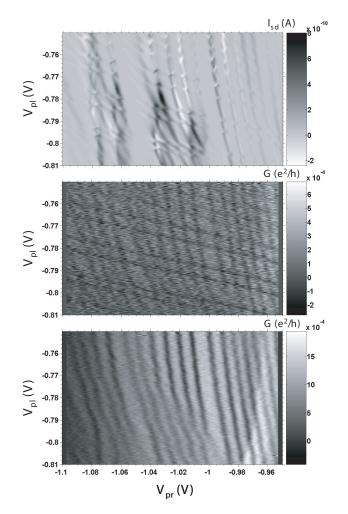

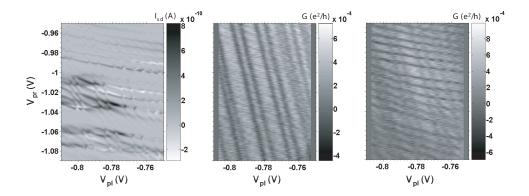

Quantum dots are zero-dimensional boxes for electrons with a decent resemblance to natural atoms. Due to their nanoscale size, numerous interesting quantum effects can be observed. Gate-defined quantum dots were fabricated in InGaAs/InP by incorporating a high-k HfO<sub>2</sub> (20-30 nm thick, grown by atomic layer deposition) as the gate dielectric. The gate leakage was suppressed and the gating efficiency improved. At 300 mK, charge stability diagrams of single and double quantum dots were measured and studied in detail. Zeeman splitting in a parallel magnetic field and charge sensing by nearby quantum point contacts were also investigated. The single and double quantum dots are expected to be useful in fields including single electron logic, stochastic resonance, spintronics, quantum computing, etc.

### List of papers

This thesis is based on the following papers, referred to in the text by their Roman numerals.

### I. A sequential logic device realized by integration of in-plane gate transistors in $\rm InGaAs/InP$

Jie Sun, Daniel Wallin, Yuhui He, Ivan Maximov, and Hongqi Xu Applied Physics Letters **92**, 012116 (2008)

# II. Transport properties of three-terminal ballistic junctions realized by focused ion beam enhanced etching in InGaAs/InP

Martin Frimmer, Jie Sun, Ivan Maximov, and Hongqi Xu Applied Physics Letters **93**, 133110 (2008)

## III. Frequency mixing and phase detection functionalities of three-terminal ballistic junctions

Jie Sun, Daniel Wallin, Patrik Brusheim, Ivan Maximov, Zhanguo Wang, and Hongqi Xu Nanotechnology 18, 195205 (2007)

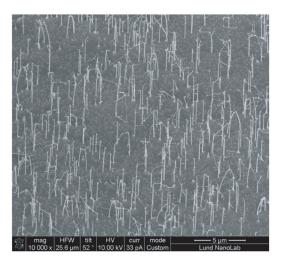

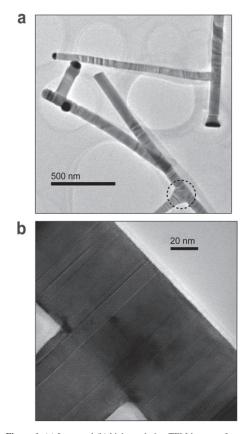

## IV. Electrical properties of self-assembled branched InAs nanowire junctions

Dmitry B. Suyatin, Jie Sun, Andreas Fuhrer, Daniel Wallin, Linus E. Fröberg, Lisa S. Karlsson, Ivan Maximov, L. Reine Wallenberg, Lars Samuelson, and Hongqi Xu Nano Letters 8, 1100 (2008)

### V. A novel SR latch device realized by integration of three-terminal

ballistic junctions in InGaAs/InP

Jie Sun, Daniel Wallin, Ivan Maximov, and Hongqi Xu IEEE Electron Device Letters **29**, 540 (2008)

# VI. Gate-defined quantum-dot devices realized in InGaAs/InP by incorporating a $\rm HfO_2$ layer as gate dielectric

Jie Sun, Marcus Larsson, Ivan Maximov, Hilde Hardtdegen, and Hongqi Xu Applied Physics Letters **94**, 042114 (2009)

The following publications, describing research that has also been carried out at Lund University, are not included in the thesis due to their content overlapping with that of other publications.

#### VII. Novel nanoelectronic device applications based on the nonlinearity of three-terminal ballistic junctions

Jie Sun, Daniel Wallin, Patrik Brusheim, Ivan Maximov, Zhanguo Wang, and Hongqi Xu

AIP Conference Proceedings 893, 1471 (2007)

#### VIII. Novel room-temperature functional analogue and digital nanoelectronic circuits based on three-terminal ballistic junctions and planar quantum-wire transistors

Jie Sun, Daniel Wallin, Patrik Brusheim, Ivan Maximov, and Hongqi Xu Journal of Physics: Conference Series **100**, 052073 (2008)

# IX. Gate-defined quantum devices realized on an InGaAs/InP heterostructure by incorporating a high- $\kappa$ dielectric material

Jie Sun, Marcus Larsson, Ivan Maximov, and Hongqi Xu Proceedings of the 2009 IEEE Nanotechnology Materials and Devices Conference, 183 (2009)

### Acknowledgments

I came to the Solid State Physics Division of Lund University on August 23, 2005, for my PhD studies. Prof. Hongqi Xu offered me this opportunity to improve my research, and provided me with much scientific guidance and spiritual encouragement. Coincidentally, we discovered that we had obtained bachelor degrees from the same university: the Dalian University of Technology. I would like to take this opportunity to express my warmest gratitude to him. My cosupervisor Dr. Ivan Maximov has given me plenty of practical help in experiments, which has been crucial for my work. I am very thankful to these two supervisors. I would also like to thank Prof. Zhanguo Wang at Institute of Semiconductors, Chinese Academy of Sciences, where I am originally from, for sending me to this department where he worked as a visiting scholar from 1980 to 1983.

I express my deepest gratitude to Dr. Daniel Wallin who has helped me with many practical issues in my day-to-day experiments. I want to thank Dr. Patrik Brusheim, Dr. Patrick Carlberg, Dr. Ruisheng Liu, Gang Luo, Marcus Larsson, Henrik Nilsson, Dmitry Suyatin, Dr. Andreas Fuhrer, Dr. Stefano Roddaro, Dr. Claes Thelander, Nicklas Anttu, Mariusz Graczyk, Dr. Alline Ribayrol, David Adolph, Dr. Philippe Caroff, Yuhui He, Dr. Niklas Sköld, Carl Ellström, Gvidas Astromskas, Martin Frimmer, Anil Dey, Gabriela Conache, Dr. Zhaoxia Bi, Dr. Yingtao Zhang, Dr. Kailiang Zhang, Fantao Meng and Dr. Jianing Chen for their help in both science and life. Cordial thanks go to Profs. Lars Samuelson, Knut Deppert, Lars-Erik Wernersson for their guidance and help. Many thanks to everyone at Fasta Tillståndets Fysik (FTF) whose names are not mentioned here.

I am grateful to my family for their continuous support. My beloved wife Chunli Yan has been with me in Sweden during my years as a PhD student, initially quitting her decent job in Beijing. Our son Yitian Sun, who was born in Lund, introduces happiness into our lives. Thanks also to my parents, parents-in-law and grandfathers for their unwavering love.

This thesis would not have been possible without the support of the abovementioned people.

> Jie Sun Lund, Sweden, July 2009

### Contents

| 1  | Introduction                                                                                                                                                                     |          |  |  |  |  |

|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--|--|--|--|

| 2  | Materials and Device Fabrication         2.1       InGaAs/InP two-dimensional electron gas         2.2       Processing of planar nanodevices                                    |          |  |  |  |  |

| 3  | Discrete and Integrated In-Plane Gate Transistors3.1In-plane gate transistors in InGaAs/InP3.2Integrated device: SR latch                                                        |          |  |  |  |  |

| 4  | Discrete and Integrated Three-Terminal Ballistic Junctions4.1Three-terminal ballistic junctions in InGaAs/InP4.2Frequency mixer and phase detector4.3Integrated device: SR latch | 31<br>35 |  |  |  |  |

| 5  | Single and Double Quantum Dots5.1Single electron charging5.2Single quantum dots5.3Double quantum dots                                                                            | 49       |  |  |  |  |

| 6  | 5 Future Outlook                                                                                                                                                                 |          |  |  |  |  |

| Re | References                                                                                                                                                                       |          |  |  |  |  |

# Chapter 1 Introduction

$\gamma$ OMPLEMENTARY metal-oxide-semiconductor (CMOS) technology is the basis of modern integrated circuits (ICs). Moore's law, which has been the guiding principle for the semiconductor industry for over 40 years, predicts that the number of transistors per IC doubles every 2 years [1]. The stringent demand on speed and portability of electronic devices requires metal-oxide-semiconductor field effect transistor (MOSFET) scaling in verylarge-scale integration (VLSI). For example, in the 65-nm technology node (which is related to half the metal pitch of a dynamic random access memory (DRAM) device) of microprocessors, the transistor has a physical gate length of 35 nm and a gate oxide thickness of 1.2 nm [2]. In 2007, researchers at Intel used high-k (dielectric constant) Hf-based gate dielectric and dual work function metal gate electrodes to replace  $SiO_2$ /polysilicon as the gate stacks in the 45-nm technology node [3]. Currently, work is focused toward the 22nm technology node and beyond. With technological innovations, Moore's law is expected to continue at least through the next decade. MOSFETs with gate lengths down to 6 nm and silicon on insulator (SOI) channels as thin as 4 nm have been achieved at IBM [4]. However, when the device dimensions reach the nanometer scale, scaling faces numerous challenges such as gate oxide leakage, leakage between source and drain, high source-drain access resistance, mobility degradation from large field and device-to-device variations. In 2005, Gordon Moore stated in an interview that Moore's law cannot be indefinitely sustained and that the transistors would eventually reach the limits of miniaturization at atomic levels [5]. Therefore, intensive research is being carried out to explore electronic materials other than Si, as well as novel device principles beyond CMOS. An introduction to nanoelectronics can be found in Ref. [6]. Recently, much interest is devoted to the research of low band gap III-V compound semiconductors as the future transistor channel material. For instance, InGaAs and InSb quantum well FETs show

significantly improved energy-delay products, which is representative of the energy efficiency of transistors [7]. This thesis describes the detailed study of nanoelectronic devices made in InGaAs/InP based on ballistic and quantum effects. We begin with some basic concepts and theories, and then move on to in-plane gate transistors, three-terminal ballistic junctions (TBJs), quantum dots (QDs) in InGaAs/InP and their further integration.

There exist three important characteristic lengths in mesoscopic transport: the de Broglie wavelength, the mean free path and the phase relaxation length. Conductors usually demonstrate an ohmic behavior if their dimensions are much larger than the characteristic lengths [8]. At low temperatures, the current is mainly carried by electrons near the Fermi level  $E_F$ , and therefore the Fermi wavelength constitutes the relevant de Broglie wavelength. In a perfect crystal, electrons will not be scattered. They move as if they were in vacuum, but with an effective mass  $m^*$ . Any deviation from perfect crystallinity, such as impurities, lattice vibrations (phonons) or other electrons, leads to a scattering event during which the electron changes its momentum. The mean free path  $l_{mfp}$  is the distance that an electron travels before its initial momentum is destroyed:  $l_{mfp} = v_F \tau$ , where  $v_F$  is the Fermi velocity and  $\tau$  the momentum relaxation time. If the electron is only scattered by a small angle, very little momentum is lost and therefore  $l_{mfp}$ is not determined by such a scattering event. The phase relaxation length  $l_{\phi}$ is the distance that an electron travels without losing its initial phase, where the transport is coherent. Inelastic scattering such as electron-electron and phonon scattering are mainly responsible for the loss of the phase memory. Note that  $l_{mfp}$  is not affected by electron-electron scattering since it does not give rise to any loss in the net momentum. Boundary and impurity scattering processes are usually constituted by elastic scattering and do not change the phase of an electron, provided that the scatterer is rigid without internal degrees of freedom so that it can change its state.

If the device dimensions are much larger than  $l_{mfp}$ , the transport is diffusive where the Drude model is applicable [8]. In an electric field E, the electron will drift with velocity  $v_d$ . At the steady state, the rate at which the electron receives momentum from the external field is equal to the rate at which it loses momentum through scattering. Therefore, we have  $m^*v_d = eE\tau$  and the electron mobility is defined as  $\mu_e \equiv v_d/E = e\tau/m^*$ . In a homogeneous conductor, the current density is expressed as  $J = env_d$ , where n is the electron density. It is easy to derive  $J = en\mu_e E$ .  $\sigma = en\mu_e$  is called the conductivity of the conductor.  $J = \sigma E$  is the familiar ohmic law.

However, when the device dimensions are reduced to the mesoscopic scale, the ohmic law breaks down. The Landauer-Büttiker formalism [9] is a very useful tool for understanding the mesoscopic transport. The current flow through a conductor is proportional to a transmission function describing the ease with which electrons can transmit through it. Supposing that we have a coherent transport conductor connecting to several terminals (reflectionless contacts) via leads that are assumed to be ballistic conductors, the current at terminal p is an integration over energy:

$$I_p = \int i_p(E)dE,\tag{1.1}$$

where

$$i_p(E) = \frac{2e}{h} \sum_q T_{pq}(E) [f_q(E) - f_p(E)].$$

(1.2)

$f_p(E)$  is the Fermi function for terminal p

$$f_p(E) = \frac{1}{e^{\frac{E-\mu_p}{k_B T}} + 1}$$

(1.3)

and  $T_{pq}(E)$  is the total transmission (average transmission probability per mode times the number of modes in lead q) of electrons from lead q to lead p at energy E. The transmission obeys the sum rule

$$\sum_{q} T_{qp}(E) = \sum_{q} T_{pq}(E).$$

(1.4)

Here,  $I_p$  and  $i_p$  are positive if the electrons flow into terminal p. Particularly, if the bias is so small that the Fermi level difference between two terminals  $\Delta \mu \ll \epsilon_c + a \text{ few } k_B T$ , where  $\epsilon_c$  is the energy range over which the transmission function is nearly constant, Eqs. (1.1) and (1.2) can be linearized to

$$I_{p} = \sum_{q} G_{pq}(V_{p} - V_{q}), \qquad (1.5)$$

where  $V_p = -\mu_p/e$  and

$$G_{pq} = \frac{2e^2}{h} \int T_{pq}(E) \left(-\frac{\partial f_0}{\partial E}\right) dE.$$

(1.6)

Here,  $f_0(E)$  is the Fermi function at thermal equilibrium. Eqs. (1.5) and (1.6) describe the so-called linear response regime of transport. At low temperatures  $(k_BT \ll \epsilon_c)$ , the conductance

$$G_{pq} = \frac{2e^2}{h} T_{pq}(\mu_F),$$

(1.7)

which explains the quantized conductance in a narrow ballistic conductor [10]. A detailed discussion of the Landauer-Büttiker formalism can be found in Ref. [11]. The Landauer-Büttiker formalism provides a rigorous description of mesoscopic coherent transport. It is a terminal description in terms of measured currents and voltages, bypassing any questions regarding the spatial potential variation inside a device. The transmission function  $T_{pq}(E)$ describes the probability of an electron with energy E and +k state (k is the wave vector) incident in lead q to be transmitted into lead p. Assuming reflectionless contact, the incoming states in each lead are in thermal equilibrium with the corresponding electron reservoir even when a bias is applied. We can therefore calculate the conductance between two leads while giving the total conductance as measured between two contacts [11]. The Landauer-Büttiker formalism has a wide range of applicability, including high temperatures and a large bias. Even if the transport is noncoherent, it remains valid as long as the transport does not involve the "vertical" flow of electrons from one energy to another.

The present thesis mainly discusses semiconductor nanoelectronic devices based on ballistic and quantum effects. Such devices are expected to have small sizes, high speeds, low power consumptions, novel properties and are believed to play important roles in future nanoelectronics. Currently, decananometer MOSFETs are already in full production and further downsizing will be achieved within the near future. Since the mean free path of a carrier in the silicon devices is estimated to be on the order of 10 nm, the probability for a carrier to encounter scattering events in the channel rapidly decreases. Ballistic transport signifies that the magnitude of the device is smaller than  $l_{mfp}$ , where almost no scattering processes except the boundary scattering are present in the device. If the device size is comparable to  $l_{mfp}$ , we usually talk about a quasi-ballistic transport.  $l_{mfp}$  can be elongated under large bias conditions (hot electron effect). In ballistic or quasi-ballistic transport, the device current is controlled only by the carrier injection from the source into the channel, and the conventional mobility concept and theory no longer describe the transport properly. Generally, the Landauer-Büttiker formalism is used to study the ballistic effect. An example of the ballistic/quasi-ballistic MOSFET theory can be found in Ref. [12]. Due to there existing almost no scattering events in the channel, the ballistic limit implies the high performance limit of the MOSFET in a given structure. This thesis describes the fabrication of ballistic junction devices on III-V semiconductors which have longer  $l_{mfp}$  and, therefore, relax the requirement on the device size shrinking.

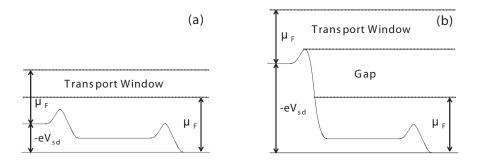

In ballistic or quasi-ballistic junctions, there is almost no scattering in the conducting channel. However, does this mean that the current will go to infinity when applying a large bias? Figure 1.1 shows the channel of a ballistic

Figure 1.1: The energy landscape of a ballistic cavity connected to two electron reservoirs through two QPCs under (a) small and (b) large bias conditions. It is assumed that there was no potential drop inside the ballistic channel [13]. When  $V_{sd}$  is large as compared to  $\mu_F$ , a gap opens up and the transport window ceases to increase, leading to a saturation of the current.

junction connecting to the source and drain via two QPCs. Under a small bias (Figure 1.1(a)), the current roughly displays a linear increase with the applied voltage. At a high bias, e.g., a large value as compared to the Fermi energy  $\mu_F$ , a gap in the electron distribution inside the sample opens, leading to a current saturation [14] (see Figure 1.1(b)). Now, the total injected current depends only on  $\mu_F$  and the height of the saddle point potential. In fact, in ballistic devices, the current is determined by the injected carrier density and the injection velocity  $v_{inj}$ . The current saturates because the injected carrier number stops increasing and  $v_{inj}$  is almost independent of the bias [12].

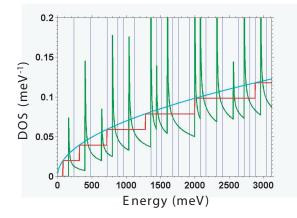

A quantum effect appears when the size of a device is reduced to certain values. Bulk semiconductors are known as 3D materials due to electrons being free to move in three dimensions. In a 2D system, the electrons are constrained to move only within two dimensions of a thin film (quantum well). Similarly, 1D quantum wires and 0D quantum dots can be obtained by further reducing the dimensions. If we take a bulk solid with parabolic isotropic dispersion relation  $E_{3D} = \frac{\hbar^2 (k_x^2 + k_y^2 + k_z^2)}{2m^*}$  (k is the wave vector) as an example, a reduction of the dimensions (assuming an infinite square potential well), leads to the energy being written as:  $E_{2D} = E_n + \frac{\hbar^2 (k_x^2 + k_y^2)}{2m^*}$ , where  $E_n = \frac{n^2 \pi^2 \hbar^2}{2m^* L_z^2}$ ;  $E_{1D} = E_{m,n} + \frac{\hbar^2 k_x^2}{2m^*}$ , where  $E_{m,n} = \frac{m^2 \pi^2 \hbar^2}{2m^* L_z^2} + \frac{n^2 \pi^2 \hbar^2}{2m^* L_z^2}$ ; and  $E_{0D} = E_{l,m,n} = \frac{l^2 \pi^2 \hbar^2}{2m^* L_x^2} + \frac{m^2 \pi^2 \hbar^2}{2m^* L_z^2}$ . Accordingly, the densities of states (DOS) are expressed by  $D_{3D} = \frac{g_s g_v V m^*}{\pi^2 \hbar^3} \sqrt{\frac{m^* E_{3D}}{2}}$ ,  $D_{2D} = \sum_n \frac{g_s g_v S m^*}{2\pi \hbar^2} \Theta(E_{2D} - E_n)$ ,

Figure 1.2: Electron density of states calculated for a 10 nm×10 nm×10 nm  $In_{0.75}Ga_{0.25}As$  material when regarded as a 3D, 2D, 1D or 0D system, using the formulae discussed in the text.

$D_{1D} = \sum_{m,n} \frac{g_s g_v L}{\pi \hbar} \sqrt{\frac{m^*}{2(E_{1D} - E_{m,n})}} \Theta(E_{1D} - E_{m,n})$  and  $D_{0D} = \sum_{l,m,n} \delta(E_{0D} - E_l - E_m - E_n)$ , where  $g_s$  and  $g_v$  respectively stand for spin degeneracy and valley degeneracy, and V, S, L are the volume, area, length of the material.  $l, m, n = 1, 2, 3, \ldots$  are the quantum numbers of the energy levels.

Because of the energy quantization effect, low-dimensional nanostructures have a very different DOS from that of the bulk material, giving rise to several remarkable physical properties of the devices. Figure 1.2 shows the electron DOS in materials of various dimensions. In the calculation, the material geometry is 10 nm×10 nm×10 nm with  $m^* = 0.047m_e$  (corresponding to In<sub>0.75</sub>Ga<sub>0.25</sub>As). The parabola corresponds to the case where the material is treated as a bulk, and the stair represents the case where it is treated as 2D. Furthermore, the sawtooth is the 1D case, and finally the  $\delta$ -function corresponds to 0D. It can be seen that, as the dimensions are reduced, electrons are constrained in narrower energy ranges and are moved to higher energies due to the quantum confinement effect.

This thesis covers several topics of planar nanoelectronic devices in In-GaAs/InP based on ballistic and quantum effects. Chapter 1 introduces the topic and presents the motivation of the research as well as some basic concepts and theories. Chapter 2 describes the aspects of the modulation doped  $In_{0.75}Ga_{0.25}As/InP$  two-dimensional electron gas (2DEG) material used throughout the study. Advanced technologies for the fabrication of planar nanodevices, including electron beam lithography (EBL), metalization, etching and gating through high-k dielectrics are discussed in detail.

Chapter 3 focuses on in-plane gate transistors and their possible applications in nanoelectronic ICs through the analysis of a model device SR flip-flop. Although they are new devices, the main principles can be understood by classical physics and electronics. Chapter 4 introduces three-terminal ballistic junctions which can be explained using the Landauer-Büttiker formalism. In combination with the in-plane gate technology, it is demonstrated that TBJs can be possible candidates for building blocks in future nanoelectronics. Chapter 5 switches to low-temperature devices, where single and double quantum dots are illustrated. These devices are interesting not only in nanoelectronics for single electron transistors (SETs) and stochastic resonance applications, but also in spintronics and quantum information science and technologies. Chapter 6 summarizes several possible directions of the future work. It is our hope that the results presented in this thesis be a valuable contribution to the nanoelectronic research on InP-based semiconductors.

# Chapter 2 Materials and Device Fabrication

$\mathbf{I}^{\mathrm{NP}}$  and related compounds are key semiconductor materials for radio frequency (RF) electronics [15] as well as 1.3- and 1.5- $\mu$ m spectral region optical fiber communications [16]. The work described in this thesis is based on a modulation doped In<sub>0.75</sub>Ga<sub>0.25</sub>As/InP 2DEG grown by metal-organic vapor phase epitaxy (MOVPE). The properties of the material and the fabrication of the nanodevices are discussed in this chapter.

#### 2.1 InGaAs/InP two-dimensional electron gas

Indium phosphide has a zinc blend crystal structure with the lattice constant of 5.869 Å. The density is 4.787 g/cm<sup>3</sup> and the melting point is 1335 K. The dielectric constant is 12.5 and the band gap is 1.35 eV. At room temperature, the electron and hole mobilities are 0.45 m<sup>2</sup>/Vs and 0.015 m<sup>2</sup>/Vs, respectively. The drift velocity of InP under large electric fields is larger than those of GaAs and Si, which is promising for RF devices [17]. Other properties of bulk InP can be found in Ref. [18].

With the progress in epitaxial growth based on molecular beam epitaxy (MBE) and MOVPE, it is possible to grow extremely thin layers with sharp interfaces between adjacent layers. As a result, the use of heterostructures in high speed devices was materialized in the 1970s. Researchers at Bell Labs reported on an enhancement of electron mobility at the interface of a GaAs/AlGaAs heterojunction [19]. Shortly thereafter, the first high electron mobility transistor (HEMT) was invented at Fujitsu [20]. The first modulation doped 2DEG was realized in GaAs/AlGaAs heterojunctions, where the different band gaps of GaAs and AlGaAs give rise to offsets  $\Delta E_c$  and  $\Delta E_v$  in the conduction and valence bands, respectively. In such structures, a large  $\Delta E_c$  is desired since this stimulates the transfer of electrons from the n-doped

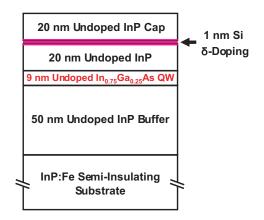

Figure 2.1: The epitaxial layer structure of the pseudomorphic  $In_{0.75}Ga_{0.25}As/InP$  2DEG on semi-insulating InP substrate.

AlGaAs (wider band gap) to the undoped GaAs (narrower band gap). The transferred electrons are in a triangular-shaped quantum well (QW) at the GaAs side of the GaAs/AlGaAs interface. Since the QW is only a few nm thick, the electrons are confined in the material growth direction and only free to move in the plane of the interface, forming a 2DEG. Due to the 2DEG being spatially separated from the donor impurities, scattering is suppressed and the electron mobility is increased, which can be seen in the formula  $\sigma = en\mu_e$ . To obtain a large  $\sigma$ , an increased doping is required in the channel so as to obtain a large n, but that will introduce more scattering and pull down  $\mu_e$ . Modulation doping successfully bypasses this contradiction and channels with high  $\sigma$  can thus be achieved in HEMTs [21].

GaAs/AlGaAs is a lattice-matched heterojunction. Another lattice-matched system, grown on InP substrates, is  $In_{0.52}Al_{0.48}As/In_{0.53}Ga_{0.47}As/InP$ . In the latter, it is possible to obtain larger  $\Delta E_c$  values than the GaAs/AlGaAs counterpart. Also, InGaAs has a low effective mass, resulting in a high lowfield electron mobility and a high peak electron velocity, since the increased energy quantization reduces the inter-subband scattering. The energy difference between the  $\Gamma$  point and the X valley is larger in InGaAs, which further improves the peak electron velocity. Particularly, InGaAs/InP has a low defect density after etching, where the depletion width at the etched sidewalls [22] is small, rendering it a good candidate for etched nanodevices.

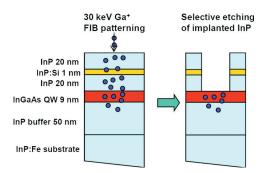

In the present work, the indium concentration was increased to 75% to form a pseudomorphic structure with InP. The heterostructure was grown by MOVPE, and the layer sequences are shown in Figure 2.1. On a semiinsulating InP:Fe substrate, a 50-nm undoped buffer layer, a 9-nm undoped

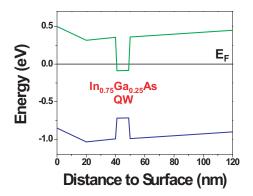

Figure 2.2: The calculated conduction and valence band diagram of the  $In_{0.75}Ga_{0.25}As/InP$  modulation doped heterostructure illustrated in Figure 2.1.

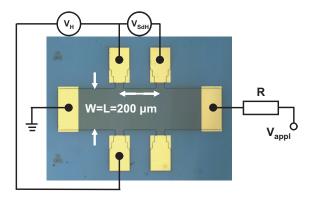

Figure 2.3: A Hall bar made by EBL and wet etching together with a schematic diagram of the measurement circuit.

In<sub>0.75</sub>Ga<sub>0.25</sub>As quantum well, 20 nm of undoped InP, 1 nm of Si  $\delta$ -doped InP and a 20-nm undoped InP cap were successively grown. In contrast to the GaAs/AlGaAs, the 2DEG is not formed at the interface of the heterostructure, but at the InGaAs square quantum well. InP was chosen over InAlAs as the barrier layers due to it having a superior chemical stability and the fact that it was difficult to achieve high-quality Al-based layers in MOVPE. By solving the 1D Poisson equation at room temperature, the estimated band diagram of the material system could be plotted in Figure 2.2. The reference point of the energy was selected to be at the Fermi level. It was seen that only the QW was below the Fermi energy, indicating the absence of any other parallel conducting layers.

Regarding wafer 4113, at room temperature, the sheet electron concen-

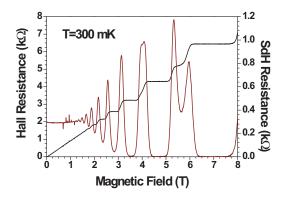

Figure 2.4: A typical result of a Hall measurement: longitudinal and transversal resistances of the 2DEG in wafer 4113 as functions of the perpendicular magnetic field. The data was recorded at 300 mK with a lock-in technique, where the applied current I was 10 nA oscillating at 37 Hz.

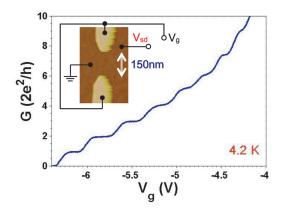

tration, mobility and mean free path were  $5 \times 10^{15}$  m<sup>-2</sup>, 1.3 m<sup>2</sup>/Vs and 150 nm, respectively. At 300 mK,  $n_s,~\mu_e$  and  $l_{mfp}$  were  $4{\times}10^{15}$  m^-2, 50 m^2/Vs and 5  $\mu$ m. For wafer 4057, at room temperature,  $n_s$ ,  $\mu_e$  and  $l_{mfp}$  were  $4 \times 10^{15}$ m<sup>-2</sup>, 0.9 m<sup>2</sup>/Vs and 100 nm. At 300 mK,  $n_s$ ,  $\mu_e$  and  $l_{mfp}$  were 4×10<sup>15</sup> m<sup>-2</sup>,  $6.8 \text{ m}^2/\text{Vs}$  and 730 nm. These parameters were obtained through Hall measurements in the dark. Details of classical and quantum Hall effects can be found in Ref. [23]. Here, only a brief description and summary of the calculation methods are provided. Figure 2.3 shows an optical micrograph of a Hall bar, together with the measurement circuits. For the convenience of the calculation, the width W and length L of the Hall bar were designed to be identical. The ohmic bonding pads were slightly wider than the contact areas on the mesa in order for the edge states to have little influence on the contacts. A small bias  $V_{appl}$  was applied to the drain and the source was grounded. Since the 2DEG resistance was much smaller than the series resistor R, a constant current I was flowing in the Hall bar. A magnetic field B was applied perpendicular to the 2DEG plane. The Landau levels were formed at energies  $E_n = (n - 1/2)\hbar\omega_c$ , where  $\omega_c$  is the cyclotron energy and  $n=1, 2, 3, \dots$  The energy reference point was selected at the lowest quantized level in the material growth direction. The filling factor  $\nu$  denotes the number of occupied Landau levels (in general  $\nu$  is not an integer), where the two spins are counted as separate levels. The Hall voltage  $V_H$  and Shubnikov-de Haas voltage  $V_{SdH}$  were measured according to Figure 2.3.

A typical result of the Hall measurement on wafer 4113 is shown in Figure 2.4, where the Hall and Shubnikov-de Haas resistances ( $V_H$  and  $V_{SdH}$  divided

by I) are plotted against the magnetic field B. For a sample with an even higher mobility we refer to Ref. [24]. As can be seen in the figure, at small B, known as the classical Hall effect regime,  $R_H$  increases linearly with B.  $R_{SdH}$  oscillates with the magnetic field (when B is close to zero the oscillation is too small to be detected), since the Landau levels are pushed upwards at increasing B (the Fermi level remains unchanged). The transport is diffusive. The relationship of the electric field, magnetic field and drift velocity is E = $v_d B$ . The sheet electron density and mobility can be calculated from  $n_s =$  $IB/eV_H$  and  $\mu_e = LI/(en_sWV_{SdH}|_{B=0})$ . At higher B, the energy distance between two Landau levels becomes further increased. If the difference is so large that there exists a region in between two Landau levels where the DOS reaches zero, the device functions in the quantum Hall effect regime. Several plateaux appear in the  $R_H$ -B curve, and the valleys in the SdH oscillation decrease to zero. The transport is equivalent to ballistic transport at the plateaux, whereas it remains diffusive at rising edges. It can further be seen from Figure 2.4 that spin splitting is observed at sufficiently large B. Before the Zeeman splitting takes place, minima occur in the SdH oscillation when  $E_F$  lies in the middle of two Landau levels, namely  $E_F = n\hbar\omega_c$ . Thus,  $n = n_s \pi \hbar/(eB)$ , and  $n_s$  can be obtained from the n-1/B plot. However, the  $n_s$  given here is usually somewhat smaller than its counterpart from the classical Hall effect. The absolute value of n can be extracted from  $G_H = 1/R_H = \nu e^2/h.$

Some of the most frequently used formulae in 2DEG systems are summarized in Table 2.1. For GaAs/AlGaAs and InGaAs/InP,  $g_s = 2$  and  $g_v = 1$ .

#### 2.2 Processing of planar nanodevices

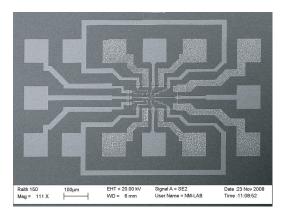

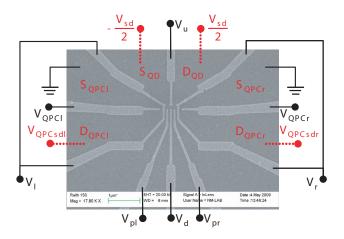

Planar nanoelectronic devices (either etched or gated) can be fabricated by multiple step lithography on InGaAs/InP. A typical double dot device is shown in Figure 2.5, where the mesa, ohmic contact and top gate can be recognized in the scanning electron microscope (SEM) picture. Each processing step is relatively sensitive and this section describes the technique in detail.

The fabrication of devices begins with mesas. On the semi-insulating substrate, the purpose of fabricating mesas is to create electrically separate islands for device isolation. Mesas can be made by lithography and etching, and their design should be as small as possible, provided that there are enough areas for ohmic contacts and fine structures. Small mesas offer a larger device packaging density, a higher operation speed and a smaller gate line leakage. From an industrial point of view, photolithography is ideal

| Item                                       | Formula                                                                                                                                                                         |

|--------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Current                                    | $I = en_s w v_d$                                                                                                                                                                |

| Current density                            | $J = en_s v_d$                                                                                                                                                                  |

| Cyclotron energy                           | $J = en_s v_d$ $E_{cycl} = \hbar \omega_c = \frac{e\hbar B}{m^*}$                                                                                                               |

| Cyclotron radius                           | $l_{cycl} = \frac{m^* v_F}{eB} = \frac{2\hbar}{eB} \sqrt{\frac{\pi n_s}{g_s g_v}}$                                                                                              |

| Density of states                          | $DOS(E) = \frac{g_s g_v m^*}{2\pi\hbar^2}$                                                                                                                                      |

| Diffusion constant                         | $DOS(E) = \frac{g_s g_v m^*}{2\pi \hbar^2}$ $D = \frac{v_F^2 \tau}{2} = \frac{2\pi \hbar n_s \mu_e}{em^* g_s g_v}$                                                              |

| Electron mobility                          | $\mu_e = \frac{e\tau}{m^*}$                                                                                                                                                     |

| Fermi energy                               | $E_F = \frac{n_s}{DOS(E)} = \frac{(\hbar k_F)^2}{2m^*} = \frac{2\pi\hbar^2 n_s}{g_s g_v m^*}$ $v_F = \frac{\hbar k_F}{m^*} = \frac{2\hbar}{m^*} \sqrt{\frac{\pi n_s}{g_s g_v}}$ |

| Fermi velocity                             | $v_F = \frac{\hbar k_F}{m^*} = \frac{2\hbar}{m^*} \sqrt{\frac{\pi n_s}{g_s g_v}}$                                                                                               |

| Fermi wavelength                           | $\lambda_F = \frac{2\pi}{k_F} = \sqrt{\frac{\pi g_s g_v}{n_s}}$                                                                                                                 |

| Fermi wave vector                          | $k_F = \sqrt{\frac{2m^* E_F}{\hbar^2}} = 2\sqrt{\frac{\pi n_s}{g_s g_v}}$                                                                                                       |

| Magnetic length                            | $l_m = \sqrt{\frac{\hbar}{eB}}$                                                                                                                                                 |

| Mean free path                             | $l_{mfp} = v_F \tau = \frac{2\hbar\mu_e}{e} \sqrt{\frac{\pi n_s}{g_s g_v}}$                                                                                                     |

| Momentum relaxation time (scattering time) |                                                                                                                                                                                 |

| Ohmic law (diffusive transport)            | $\tau = \frac{m^* \mu_e}{e}$ $I = \frac{V}{R}, \ J = \frac{E}{\rho}$ $R = \rho \frac{L}{W}$                                                                                     |

| Resistance in diffusive transport          |                                                                                                                                                                                 |

| Thermal energy                             | $E_{th} = k_B T$                                                                                                                                                                |

| Thermal length                             | $l_{th} = \sqrt{\frac{\hbar D}{k_B T}}$                                                                                                                                         |

| 2DEG resistivity in diffusive transport    | $\rho = \frac{1}{\sigma} = \frac{1}{e n_s \mu_e}$                                                                                                                               |

Table 2.1: Commonly used 2DEG formulae.

Figure 2.5: An SEM image providing an overview of a ready-made double quantum dot device in InGaAs/InP. The gate dielectric, HfO<sub>2</sub>, has no contrast in this picture due to it covering the entire sample beneath the top metal layer. The size of the 14 bonding pads are 100  $\mu$ m×100  $\mu$ m.

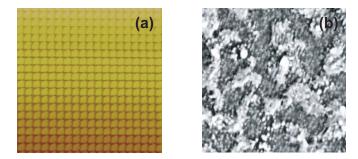

for mesa fabrication. However, since the present study involves very small samples (4 mm×5 mm), EBL is more convenient. A double layer negative resist ma-N 2403 was used in the EBL with the consideration that it has a large endurance time in strong acids as well as a decent adhesion to the samples. In order to save exposure time, an extremely large beam step size was used, i.e., 0.5  $\mu$ m, along with an aperture of 120  $\mu$ m. The optimal dose was 80  $\mu$ C/cm<sup>2</sup>. After development in ma-D 532 for 0.5 min, the resist morphology was observed by atomic force microscopy (AFM), as shown in Figure 2.6(a). The period of the pattern corresponded to the step size of the EBL. Although the step size was large, the proximity effect connected all the exposed points together, keeping the exposed resist as a continuous film protecting the mesa surface during etching.

Dry etching is generally more anisotropic than wet etching and thus provides sharper mesa edges. This is, however, a disadvantage rather than an advantage in the present case, since steep mesa edges could prevent the top gate metal lines from climbing up to the mesa surfaces. Therefore, wet etching was utilized to define mesas. There exists a number of chemicals serving as etchants of InP-based semiconductors [25], but unfortunately almost all of them are volatile, which reduces the reproducibility of the etching process. HCl : HNO<sub>3</sub> : H<sub>2</sub>O = 1 : 1 : 2 can be used for mesa etching. HCl can selectively etch InP and HNO<sub>3</sub> can selectively etch InGaAs. Nevertheless, the etching speed is a little too high (~400 nm/min) and if the concentration is not properly adjusted, the mesa edge slope will be dependent on crystal directions. In the presented experiments, attempts were made to use another

Figure 2.6: (a) A 10  $\mu$ m×10  $\mu$ m AFM image of the ma-N 2403 resist after development. It was exposed to an electron beam with a 0.5  $\mu$ m step size. (b) A 20  $\mu$ m×20  $\mu$ m SEM image of the Au/Ge ohmic contact after annealing at 370 °C during 2 min.

bromine-based etchant. 300 ml of saturated bromine water was added to 5 ml of HBr acid, diluted with 25 ml of deionized (DI) water, to which 5 ml of HNO<sub>3</sub> was added. The solution was then ready for use. In 5 min, the etching depth was found to be  $\geq 200$  nm, down to the semi-insulating substrate. The rake angle at the mesa edge was about 45 ° for all crystal directions.

The ohmic contacts were made by EBL and thermal evaporation followed by lift-off. The EBL procedures were similar to the previous ones, with the exception of a change to a double layer positive resist ZEP 520A to save the exposure time. The optimal dose was 90  $\mu$ C/cm<sup>2</sup>. The development was carried out in O-xylene for 5-10 min. A survey of the ohmic contacts to III-V compound semiconductors can be found in Ref. [26]. Au/Ge/Ni or Au/Ge are standard recipes for ohmic contact metals on n-InP. The eutectic temperature of the AuGe alloy is 361 °C and, thus, the annealing temperature should be within the same range. 20 nm Au/60 nm Ge/120 nm Au were grown on InGaAs/InP and annealed at 370 °C for 2 min. Figure 2.6(b) shows a SEM micrograph of the annealed ohmic contacts. The surface of the metal became rough and slightly balled up. At room temperature, the typical ohmic contact resistance of the materials was a few  $k\Omega$ , and the resistance between two neighboring mesas was on the order of  $10^8 \Omega$ . If the annealing temperature was too high, the metal would melt too much, resulting in a destroyed ohmic contact (not transparent). It is furthermore worth noting that the InP surface was very sensitive and the sample should always be kept in vacuum if there is no encapsulation. Any inappropriate processing could induce surface conducting channels and destroy the mesa isolation. Such processes include electron or ion bombardment, plasma preen, ozone cleaning, an insufficiently thorough removal of the resist, etc.

| Material                         | Permittivity (k) | Band gap (eV) | $\Delta E_c$ (eV) to Si |

|----------------------------------|------------------|---------------|-------------------------|

| Al <sub>2</sub> O <sub>3</sub>   | 9                | 8.7           | 2.3                     |

| $Ce_2O_3$                        | 26               | 5.5           |                         |

| HfO <sub>2</sub>                 | 15-40            | 5.7           | 1.5                     |

| HfSi <sub>x</sub> O <sub>y</sub> | 15-25            | ~6            | 1.5                     |

| La <sub>2</sub> O <sub>3</sub>   | 30               | 4             | 2.3                     |

| Si <sub>3</sub> N <sub>4</sub>   | 7                | 5.1           | 2                       |

| SiO <sub>2</sub>                 | 3.9              | 8.9           | 3.2                     |

| Ta <sub>2</sub> O <sub>5</sub>   | 26               | 4.5           | 1-1.5                   |

| TiO <sub>2</sub>                 | 80               | 3.5           | 1.2                     |

| Y <sub>2</sub> O <sub>3</sub>    | 15               | 5.6           | 2.3                     |

| ZrO <sub>2</sub>                 | 25               | 7.8           | 1.4                     |

| ZrSi <sub>x</sub> O <sub>y</sub> | 12-25            | 6.5           | 1.5                     |

**Table 2.2:** A summary of the physical properties of various high-k materials. SiO<sub>2</sub> is also listed for the sake of comparison.

Fine structures of nanodevices can be fabricated by wet chemical etching, top metal gating or a combination of the two. For etching, ZEP 520A7 was used in EBL. The step size was 10 nm for area exposure and 2 nm for line exposure. The optimized area dose was  $\sim 30 \ \mu\text{C/cm}^2$  whereas it was  $\sim 300 \ \mu\text{C/cm}$  for the line dose. The etching solution was similar to before, but the amounts of HBr, HNO<sub>3</sub> and DI water were changed to 3 ml, 3 ml and 60 ml, respectively, and the etching time was reduced to 30 s. The etching was isotropic with respect to the crystal directions, with an etching depth of more than 100 nm. For gating, PMMA 950A4 was used. The optimized area dose was  $\sim 200 \ \mu\text{C/cm}^2$  and for the line dose it was  $\sim 2000 \ \mu\text{C/cm}$ . Although ZEP 520A7 can also be used for this purpose, it would become more easily burnt during metal evaporation. The metals for the top gates consisted of 5 nm Ti/45 nm Au. Moreover, the gate dielectric could be either cross-linked PMMA 950A [27], produced by exposure to an extremely high dose (20000-40000  $\mu$ C/cm<sup>2</sup>), or hafnium dioxide, as discussed below.

A scaling down of CMOS in the VLSI fabrication is essential to obtain a better performance and a higher packaging density of the devices and circuits. However, when the thickness of the gate oxide is thinned to below  $\sim 3$ nm, tunneling through the silicon dioxide introduces a leakage current that increases exponentially with a decreasing oxide thickness. The gate leakage current gives rise to a low on-off ratio of the MOSFETs and a high power

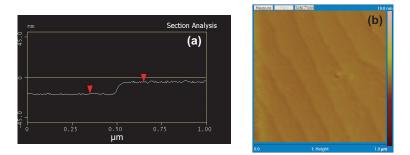

Figure 2.7: (a) The profile of 12-nm HfO<sub>2</sub> after the lift-off process on InGaAs/InP, measured by cross-sectional AFM. (b) A 1  $\mu$ m×1  $\mu$ m AFM image of an area where the HfO<sub>2</sub> film had been removed. The atomic steps on the InGaAs/InP single crystal were clearly resolved, indicating the lack of residuals of resist or hafnium dioxide after the lift-off in 140 °C-remover 1165.

consumption. In order to solve the problem, high-k materials were employed to replace  $SiO_2$  in the gate stack. The characteristics of some of the oxides are summarized in Table 2.2. HfO<sub>2</sub> has a high k value in combination with large band offsets to semiconductors, and is thermodynamically stable. Thus, hafnium-based dielectrics are the most promising candidates for the replacement of SiO<sub>2</sub>.

Although an extensive effort has been made regarding the development of high-k gate dielectrics on silicon [28], the incorporation of high-k materials in III-V devices is still at an early stage [29]. It is known that the Schottky barrier height of metal/indium-based III-V semiconductor materials is too low to suppress the leakage current to the gate. For example, the Schottky barrier height of metal/n-InP is  $\leq 0.5$  eV [30, 31]. For the present experiments, a thin HfO<sub>2</sub> film was inserted between the Ti/Au and InGaAs/InP as a gate dielectric, reducing the leakage current and improving the gating efficiency [32]. Hafnium tetrakis(dimethylamide) Hf[N(CH<sub>3</sub>)<sub>2</sub>]<sub>4</sub> and water [33] were used to grow HfO<sub>2</sub> in the atomic layer deposition (ALD) system. The film could be grown at 300 °C. N<sub>2</sub> was employed as the carrier gas. The pulse times for the precursor Hf[N(CH<sub>3</sub>)<sub>2</sub>]<sub>4</sub> and water were 0.1 s and 0.025 s, respectively, and the purge times for Hf[N(CH<sub>3</sub>)<sub>2</sub>]<sub>4</sub> and water were both 5 s. The chemical reaction can be written as

$$Hf[N(CH_3)_2]_4 + 2H_2O = HfO_2 + 4NH(CH_3)_2.$$

(2.1)

The growth was started with the Hf precursor pulse. The water adsorbed on the surface of the semiconductor provided OH groups that were needed for ALD. The reaction was self-limited, and one monolayer of  $HfO_2$  was deposited in each growth cycle. The growth rate was approximately 0.8 Å/cycle. Asgrown films could be etched in hydrofluoric acid, but unfortunately most EBL resists were unable to survive in HF. If the growth temperature was lowered to 100 °C, patterning by lithography and lift-off of HfO<sub>2</sub> became possible [34]. At 100 °C, the growth conditions were almost the same as those at 300 °C, except that the purge time was increased to 80 s for Hf[N(CH<sub>3</sub>)<sub>2</sub>]<sub>4</sub> and H<sub>2</sub>O. The deposition rate was as high as ~1.2 Å/cycle, probably due to an insufficient cracking of the precursors. Figure 2.7(a) shows a cross-sectional AFM image of the lift-off result of 12-nm HfO<sub>2</sub> on InGaAs/InP, and one can clearly see the sharp step edge. Figure 2.7(b) is a 2D AFM image of an area where the hafnium dioxide was lifted-off. Atomic steps on the InP epi-layer are resolved, indicating that there were no residuals of resist or HfO<sub>2</sub> left on the surface.

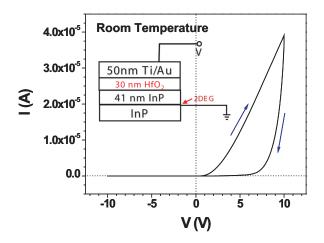

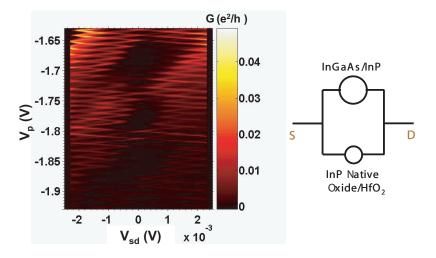

As-grown  $HfO_2$  thin films are known to display excellent dielectric properties: the k value is ~15 [35], the break down field is  $\geq 4 \text{ MV/cm}$  and, under normal device operating conditions, the gate leakage current density is on the order of  $10^{-8}$ - $10^{-7}$  A/cm<sup>2</sup>. HfO<sub>2</sub> grown at 100 °C has a larger breakdown field and a smaller leakage current as opposed to films grown at 300 <sup>o</sup>C. The reason for this is because of it being amorphous rather than polycrystalline. Figure 2.8 displays the I-V curve of a diode fabricated on 100 <sup>o</sup>C-grown HfO<sub>2</sub>/InP/InGaAs. A schematic diagram of the device is shown in the inset. The active area of the device was  $\sim 80 \ \mu m^2$ . At room temperature, the rectification behavior was observed. A very strong hysteresis effect was also seen, which could be useful in memory devices [36]. The rectification and hysteresis were ascribed to the parasitic conducting layer at the InP native oxide. It is known that the interface between InP and insulators is electrically unstable [37]. In the present case, at the interface, there was a parallel conductance at the InP native oxide, which probably had the same origin as the recently discovered 2DEGs at the interfaces between different oxides [38]. The conduction band offset for  $HfO_2$  on InP was calculated to be 1.74 eV [39]. At the forward bias, the electrons trapped at the InP native oxide caused Fermi level pinning at this layer, thereby reducing the effective barrier height and results in the current rectification. As a result of many electrons being captured by the traps at the interface during transport, the current at positive voltages was at a low state when the voltage sweep began from large positive values. On the other hand, while the sweep started from large negative bias, the trapped electrons were somewhat depleted, and the current at positive voltages was at a high state. The rectification and hysteresis existed also at 300 mK, where the loop was much smaller due to a reduced number of trapped electrons.

Current rectification and hysteresis effects are troublesome in device fab-

Figure 2.8: An I-V curve of a metal/HfO<sub>2</sub>/InP/InGaAs diode. At room temperature, rectification and hysteresis effects are observed, indicating a large density of trap states at the dielectric-semiconductor interface. The voltage sweep began from -10 V. Inset: a scheme for the diode with voltage configuration.

rication. The resistance between neighboring mesas decreased from  $\geq 250$  $M\Omega$  down to below a few  $M\Omega$  and the mesa isolation was destroyed. After a systematic study, two solutions to this problem were found. The first one was to grow  $HfO_2$  at elevated temperature (e.g., at 300 °C) with a proper pretreatment of the InP surface [40, 41, 42] prior to ALD. The employed recipe for surface preparation involved first etching the sample with annealed ohmic contacts on mesas in diluted HF acid (HF: $H_2O=1:4$ ) for 20 min and then sulphur passivating the surface in a solution of  $(NH_4)_2S_x$ :  $H_2O=1:9$  at 60 °C for 20-60 min. The sample was kept in DI water during the transfer to the ALD chamber to avoid reoxidization in air. The interface states could thus be eliminated and the mesa isolation was protected. Nevertheless, patterning in the  $HfO_2$  could not be easily carried out. Fortunately, although the ohmic contacts were covered by the hafnium dioxide, the force generated by a standard thermosonic wire bonder allowed metal to penetrate the film and connect the ohmic bonding pads to the outside electrodes. Another solution was to use a cross-linked PMMA 950A bridge. After baking, the interface between the PMMA 950A resist and InGaAs/InP became insulating. Therefore, PMMA 950A cross-linked locally at the 100 °C-grown HfO<sub>2</sub> pattern edge, the Ti/Au gate line will, when it climbs up this bridge, not have any electrical contact to the leaking  $HfO_2/III-V$  interface. Note that at a growth temperature of 100 °C, the above-mentioned surface pretreatment did not

work and, thus, the PMMA 950A bridge was necessary. Based on these two technologies, gate defined quantum devices (cf. Chapter 5) could be realized in InGaAs/InP with the gate dielectric  $HfO_2$ .

### Chapter 3

### Discrete and Integrated In-Plane Gate Transistors

$\mathbf{F}^{\text{IELD}}$  effect transistors are the most important semiconductor devices in VLSI. They are unipolar since only one type of carrier predominantly participates in the conduction process. This chapter describes a new type of FET with two in-plane gates in a InGaAs/InP 2DEG material. Proof is also given, by way of the device principle, that such transistors can be used in future nanoelectronic integrated circuits.

#### 3.1 In-plane gate transistors in InGaAs/InP

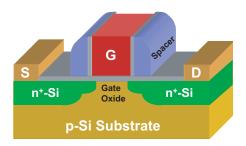

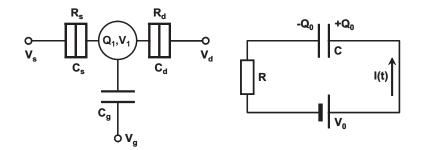

Let us first review the basic characteristics of MOSFETs. A typical MOS-FET is illustrated in Figure 3.1. On a p-Si substrate (or p-well), the source and drain regions are  $n^+$ -doped by junction implants. On a thin oxide film, the gate is formed (usually by polysilicon or metal). There are spacers (e.g., nitride) between the gate and the source and drain, and in such a structure, when the gate voltage is sufficiently large, there is an inversion layer at the surface of the p-Si below the gate oxide. The conducting channel for electrons is formed in this layer, which can be controlled by the gate. If the gate voltage  $V_G$  is above the threshold voltage  $V_T$ , the channel is conducting. When the voltage on the drain contact  $V_D$  is small (for convenience, the source potential is set to be the ground), the drain current  $I_D$  will increase almost linearly with  $V_D$ . The channel resembles a normal resistor and the transistor operates at the linear region. When  $V_D$  is further increased to a value equal to  $V_G - V_T$ , the channel begins to pinch off. The channel width becomes reduced to zero at the place where the channel connects to the drain. The corresponding drain voltage is denoted  $V_{Dsat}$ , and beyond  $V_{Dsat}$ , the channel

Figure 3.1: A 3D schematic diagram of a MOSFET. The device has 4 electrodes: source, drain, gate and substrate. Moreover, pn junctions are formed near the source and drain regions.

current  $I_D$  remains essentially unchanged, with the device operating at the saturation region. The output properties of the transistor are described by a group of  $I_D$ - $V_D$  curves at various  $V_G$  values. In the saturation regime, the transfer properties of the transistor are modeled by

$$g_m = \frac{\partial I_D}{\partial V_G} |_{V_D = const} = \frac{Z\mu_e k_{ox}}{dL} (V_G - V_T), \qquad (3.1)$$

where  $Z, \mu_e, k_{ox}, d$ , and L are the channel width, channel electron mobility, gate oxide permittivity, gate oxide thickness and channel length, respectively [43, 44].

The search for novel nanoelectronic devices has triggered intensive research activities in quantum wire transistors [45]. 1D quantum wire structures are considered to be promising devices in nanoelectronics [46]. Inplane gate transistors are also known as planar quantum wire transistors. They were first introduced and realized in GaAs/AlGaAs 2DEG in the 1990s [47, 48, 49]. The gates are capacitively coupled to the channel through etched trenches or insulation lines written by a focused ion beam (FIB). In contrast to the MOSFET presented in Figure 3.1, the source, drain, current channel, and two 2DEG gates of in-plane gate transistors lie in the same plane. Therefore, in-plane gate transistors can be fabricated by a single step lithography. Moreover, a high transconductance can be achieved [49, 50]. Most importantly, the channel conductance can be controlled by two gates where the voltages can be applied separately. This is equivalent to a combination of a top and a bottom gate in a conventional double-gate FET, naturally resulting in a simplified circuitry for implementing a given logic function. To date, the device principles of in-plane gate transistors are receiving much attention and they have been realized in numerous material systems such as GaAs/AlGaAs [47, 48, 49], GaN/AlGaN [51], SiGe/Si [52], silicon on insulator [53], diamond [54], etc.

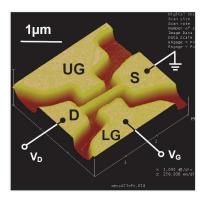

Figure 3.2: A 3D AFM picture of an in-plane gate transistor fabricated by EBL and wet etching in an InGaAs/InP wafer 4113. The circuit configuration for the measurements in Figures 3.3 and 3.4 is also given.

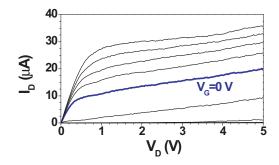

However, so far no in-plane gate transistors in InGaAs/InP have been reported. Paper I describes the fabrication of in-plane gate transistors on wafer 4113 by EBL and a wet etching technology, which were presented in the previous chapter. Figure 3.2 shows an AFM image of such a transistor and the corresponding measurement circuit. The channel was lithographically defined to be 1.1  $\mu$ m long and 200 nm wide. From the measurements of other devices, it was determined that the transistor was not conducting when the channel width  $\leq \sim 100$  nm, and thus the electrical width of the channel in Figure 3.2 was estimated to be approximately 100 nm. This was a consequence of the etching-induced surface depletion [22]. The upper and lower gates, denoted UG and LG, were 750 nm wide, covering most of the channel length. Figure 3.3 shows the room-temperature output current-voltage properties of the device, where the source was grounded and  $V_D$  was applied to the drain. The drain current increased with an increasing gate voltage (-2 V to 2 V with 0.5 V step), which is typical for n-channel FETs. In this measurement,  $V_G$  was applied to LG, and UG was left floating (see Figure 3.2).

At negative  $V_G$ , the gating efficiency was higher than that at positive  $V_G$ . To study this phenomenon quantitatively, as presented in Figure 2 of Paper I, the square root of the channel current  $\sqrt{I_D}$  in the saturation regime  $V_D = 1.5$ V was plotted against  $V_G$ . Although in-plane gate transistors have a different mechanism as opposed to that of MOSFETs, the transfer characteristics at  $V_T \leq V_G \leq 0$  V can still be approximately described by Eq. (3.1), where  $Z\mu_e k_{ox}/dL$  is replaced by a gain factor k ( $k = 1.922 \times 10^{-5}$  AV<sup>-2</sup> for the device in Figure 3.2). The peak transconductance was at  $V_G = 0$  V.  $g_m$

Figure 3.3: Output current-voltage characteristics at various gate voltages changing from -2 V to 2 V with 0.5 V steps of the in-plane gate transistor shown in Figure 3.2. The thicker curve corresponds to  $V_G = 0$  V, which signifies that the device is normally-on.

decreased linearly with a decreasing  $V_G$  until the transistor was completely turned off. The threshold voltage was determined to occur at  $V_T = -1.323$ V, as illustrated in Paper I. A detailed review of various methods to extract the threshold voltage in a MOSFET can be found in Ref. [55]. In contrast to traditional MOSFETs, at  $V_G>0$  V, the transconductance was reduced. This was due to the device being a depletion-mode transistor and the 1D channel having a finite physical width, leaving very little space for positive gate voltage tuning of the conducting channel.

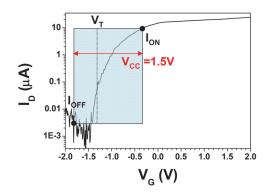

In transistors, the  $I_{ON}/I_{OFF}$  is usually called the on-off ratio. An appropriate  $I_{ON}/I_{OFF}$  can improve the speed and minimize the leakage in a circuit. In the case of optimized silicon devices, the supply voltage  $V_{CC}$  is applied between the source and drain, namely  $V_{CC} = V_D$ .  $V_G$  ranges from 0 V to  $V_{CC}$ . Historically,  $V_T$  occurs at roughly 30% of  $V_{CC}$  such that 70% of the  $V_G$  swing above  $V_T$  is used for obtaining  $I_{ON}$  while 30% of the  $V_G$  swing below  $V_T$  is used for attaining  $I_{OFF}$ . In the case of emerging nanoelectronic devices,  $V_T$ is not targeted and the I-V output is not optimized, leading to the choice of  $V_{CC}$  being somewhat arbitrary. The next section presents a sequential logic device with integrated in-plane gate transistors in InGaAs/InP (the same as that in Figure 3.2). In this circuit, the maximum possible source-drain voltage was 1.5 V during operation. Following the benchmarking methodology described in Ref. [56],  $V_{CC} = 1.5$  V was chosen. In Figure 3.4,  $I_D$  is plotted against  $V_G$  in a logarithm scale.  $V_T$ ,  $V_{CC}$ ,  $I_{ON}$ , and  $I_{OFF}$  are indicated in the figure. Using values  $I_{ON} = 9.95 \ \mu A$  and  $I_{OFF} = 5.5 \ nA$ , the on-off ratio of the device was approximately  $1.8 \times 10^3$ . In the off state, the drain current consisted mainly of the leakage current to the gate. Therefore, the on-off ratio demonstrated a strong dependence on the insulating properties of the

Figure 3.4: Transfer properties on a logarithmic scale for the in-plane gate transistor shown in Figure 3.2. The channel current  $I_D$  is plotted as a function of the gate voltages  $V_G$ . The rectangle superimposed on the curve was used to calculate the on-off ratio.

substrate.

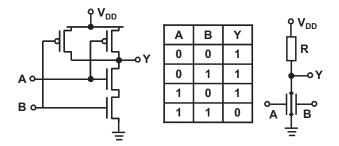

#### 3.2 Integrated device: SR latch

The CMOS technology is widely used in microprocessors and semiconductor memories, due to the circuit having a substantially lower power consumption as compared to bipolar and NMOS (n-channel MOSFET) circuits. As an example of CMOS applications in digital electronics, a CMOS NAND logic gate is depicted in Figure 3.5, together with the truth table. In CMOS logic gates, n-MOSFETs are used (when they are turned on) to pull down the output voltage to GND, whereas p-MOSFETs are employed (when they are turned on) to pull up the output voltage to  $V_{DD}$ . One may wonder what advantage can be obtained from using in-plane gate transistors to build logic gates? Apart from simple device processes, the most obvious advantage is the reduced circuitry complexity. Figure 3.5 displays a design of a NAND gate made of an in-plane gate transistor and a series resistor [57]. As discussed previously, the gating efficiency was much larger when the gate voltage was negative as opposed to for the case  $V_G > 0$  in an in-plane gate transistor. Therefore, for an in-plane gate transistor operating in an asymmetric mode where two voltages are simultaneously applied to the two gates, the conductance of the 1D channel is determined by the more negative gate voltage. As demonstrated in Figure 3.5, the transistor is turned on only when two inputs A and B are both at high states, generating an output logic 0. When one or two of the inputs are at the low state, the transistor is shut off and the

Figure 3.5: Left: a CMOS NAND gate consisting of 4 transistors. Middle: the truth table of a NAND gate, where A, B are the two inputs and Y is the output. Right: a compact NAND gate based on an in-plane gate transistor.

output is pulled up to a voltage close to  $V_{DD}$ . A compact logic NAND gate with a signal gain can thereby be realized based on a single in-plane gate transistor.

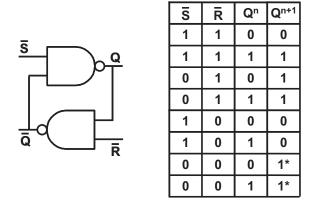

An interesting question is whether it is possible to build integrated circuits based on in-plane gate transistors with reduced circuitry complexity. The present section discusses this issue in detail. A natural idea would be to try to connect the two NAND gates shown in the right part of Figure 3.5 to form an SR latch device. A latch is an electronic circuit with two stable states rendering it capable of serving as one bit of memory. The outputs can be set to logic 0 or 1 depending on the status of the input signals. Clocked or edgetriggered latch devices are often referred to as flip-flops. However, in most cases, the two words are used interchangeably. The SR latch, where S and R respectively stand for set and reset, is fundamental. It can be constructed from a pair of cross-coupled NAND or NOR gates. The stored bit is present on the output Q and  $\overline{Q}$ . During device operations, in the storage mode, the S and R inputs are both low, and the feedback maintains the Q and  $\overline{Q}$ outputs in a constant state. If S is pulsed high while R is held low, the Qoutput is forced high, and stays high even after S returns low. Similarly, if Ris pulsed high while S is held low, the Q output is forced low, and stays low even after R returns low. Figure 3.6 displays a sketch of the SR latch device and the corresponding truth table. Note that  $\overline{S}$  and  $\overline{R}$  are the complements of S and R. Since it is a sequential logic circuit, the next state  $Q^{n+1}$  is not only determined by  $\overline{S}$  and  $\overline{R}$ , but also by the current state  $Q^n$ , signifying that the latch has a memory function.

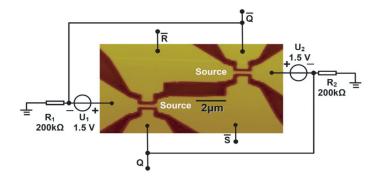

Figure 3.7 shows an AFM image of the fine structure part of an SR latch made of integrated in-plane gate transistors on InGaAs/InP, together with an illustration of the circuit configuration. The dark regions in the photograph correspond to etched trenches with a depth of  $\sim$ 120 nm. The

**Figure 3.6:** A schematic diagram showing the device principle of an SR flip-flop. The truth table is given, where  $\overline{S}$ ,  $\overline{R}$  are the inputs and Q,  $\overline{Q}$  are the outputs. \*: the logic states are uncertain when the logic 0 states of  $\overline{S}$  and  $\overline{R}$  disappear simultaneously.

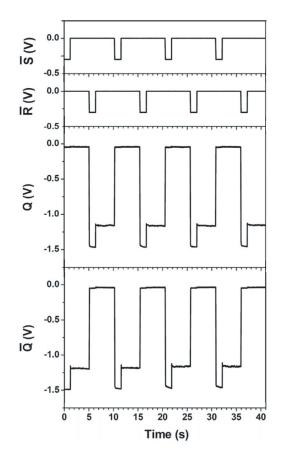

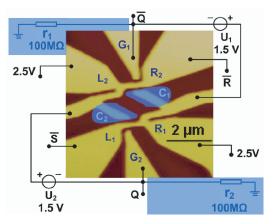

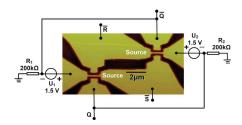

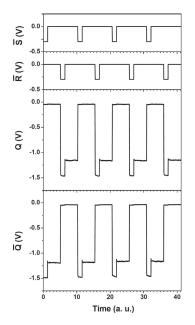

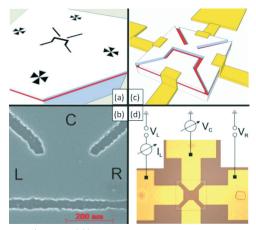

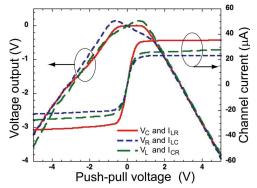

main structure contains two in-plane gate transistors with the source of one transistor connected to one in-plane gate of the other transistor and thus capacitively coupled to the channel of the other transistor. The definition of the two sources of the transistors are indicated with white text. The supplementary elements in the latch are two resistors  $R_1 = R_2 = 200 \text{ k}\Omega$  and two voltage shift units  $U_1 = U_2 = 1.5 \text{ V}$ .  $\overline{S}$  and  $\overline{R}$  are applied to the source contacts of the transistors, and  $\overline{S}$  ( $\overline{R}$ ) is also connected to the lower (upper) side gate of the upper (lower) transistor. Q and  $\overline{Q}$  are recorded from the two negative poles of the voltage shift units, and Q ( $\overline{Q}$ ) is also connected to the lower (upper) side gate of the lower (upper) transistor as a feedback. Figure 3.8 presents the logic function of the latch at room temperature. Level 0 is defined as -0.3 V for  $\overline{S}$  and  $\overline{R}$ , and  $\leq -1.2 \text{ V}$  for Q and  $\overline{Q}$ . Level 1 is 0 V for  $\overline{S}$  and  $\overline{R}$ , and -0.04 V for Q and  $\overline{Q}$ . As can be seen, Figure 3.8 exhibits a good agreement with the truth table in Figure 3.6. The input logic swing is magnified almost fourfold in the latch, showing a large signal gain.

The mechanism of the latch operation can be explained as follows. If we suppose that  $\overline{S} = \overline{R} = 0$  V and the outputs are kept at  $Q \approx -1.2$  V,  $\overline{Q} \approx 0$  V. In the lower in-plane gate transistor,  $Q \approx V_T$  (see Figure 3.4) and the transistor is (almost) closed. The upper transistor is open since both gate voltages are approximately 0 V. When the set signal  $\overline{S} = -0.3$  V comes ( $\overline{R}$  is still 0 V),  $Q - \overline{S}$  becomes much higher than  $V_T$ . At the same time, in the upper transistor, both gate voltages are lowered and the channel resistance is increased as compared to the case  $\overline{S} = 0$  V and  $\overline{Q} \approx 0$  V. The output Q is

**Figure 3.7:** An AFM image of the integrated SR latch device made on an In-GaAs/InP wafer 4113, where the dark parts correspond to wet etched trenches. A schematic diagram of the measurement circuit for the latch is also shown. The sources of the two in-plane gate transistors are marked with white text.

thus pulled up toward the ground point 0 V, and the lower transistor is more and more open. As the feedback loop drives,  $\overline{Q}$  is pulled down until it is below  $V_T$ , closing the upper transistor. Finally, the channel resistance in the lower transistor is reduced to ~40 kΩ, which is much smaller than  $R_1 = 200$ k $\Omega$ . The outputs of the latch are switched to  $\overline{Q} \approx -1.5$  V and  $Q \approx 0$  V. If the set signal disappears, i.e.,  $\overline{S}$  returns to 0 V, the gate voltage  $\overline{Q}$  is also slightly increased ( $\overline{Q} \approx -1.2$  V), as can be seen in Figure 3.8. This value, however, is approximately equal to  $V_T$  and maintains the upper transistor (almost) closed. Consequently, Q remains unchanged. These logic states will hold on until the reset signal  $\overline{R} = -0.3$  V comes. The channel resistance in the lower transistor is increased and the upper transistor is turned on. The two outputs Q and  $\overline{Q}$  are forced to jump to their opposite states, which can be analyzed in the same way as discussed above. Thus, the set, reset and storage of a logic bit in the flip-flop can all be explained based on the properties of single in-plane gate transistors. Note that it is always the case that if one transistor is closed (or almost closed), the other transistor is automatically opened. This ensures that Q and  $\overline{Q}$  always stay at two contrary states.

By fabricating an SR latch, the principle for building integrated circuits from in-plane gate transistors with simplified techniques and designs could be proven. However, several challenges remain. It is argued that these are not fundamental limits and that they can be solved by further optimizing the integrated circuit. First, the floating  $U_1$  and  $U_2$  are a consequence of the negative  $V_T$  in the transistors. If enhancement-mode [58] in-plane gate transistors can be realized, the voltage shift units are unnecessary. Second,

during operation, one of the two transistors is turned on, giving rise to a static power consumption. This can be solved by designing and building a complementary in-plane gate transistor circuitry with both n- and p-type devices [59]. Third, the device area in Figure 3.7 can be further reduced in future designs. There is evidence showing that the voltage on an in-plane gate can influence a 2DEG area of several  $\mu m$  in diameter by a capacitive coupling to the controlled area through the substrate. Therefore, in the present study, the two transistors were designed to be far from each other to eliminate the cross-talking effect. Furthermore, relatively long channels were created to remove the effect from ballistic electrons. However, in the end, it turned out that such considerations were unnecessary. In Figure 3.7, the low voltage of  $Q(\overline{Q})$  was unable to affect the upper (lower) transistor channel. This was due to the non-negative voltages on the source, channel and drain of the lower (upper) transistor providing an excellent screening. Even if the channel was shorter than the effective  $l_{mfp}$ , experiment (Paper II) and theory [14] showed that the shape of the  $I_D$ - $V_D$  curves remained basically unaltered, and therefore the device principles discussed previously still held true for short channel transistors.

The device speed could be improved by further integration of nanostructures. Generally, nanoelectronic devices present high resistances on the order of the resistance quantum  $R_Q = h/e^2$ . However, the capacitances are small due to the size effect. This gives rise to a very small RC constant, typically leading to THz alternating current (AC) performances. In other words, integrated circuits with nanodevices and nano-interconnects are much faster than traditional microelectronic ICs. Nevertheless, problems occur while connecting the nanosystem to the outside world (with 50  $\Omega$  reference impedance) due to an impedance mismatch. This explains why the latch in the present study was slow (another reason was the unpassivated surface states of the etched InGaAs/InP). Although one can put the nanodevice in an impedancematching network while driving the device by a high frequency signal [60], or extract the high frequency response by measuring the direct current (DC) average output of the nanodevice [61], the ultimate solution to the speed problem consisted in an integration of nanoelectronic systems [62].

Figure 3.8: Inputs and outputs of an as-fabricated SR flip-flop measured at room temperature. An amplification of the signal swing was observed (gain of  $\sim$ 4).

### Chapter 4

## Discrete and Integrated Three-Terminal Ballistic Junctions

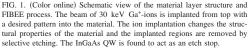

THIS chapter discusses three-terminal ballistic junctions in InGaAs/InP. TBJs are emerging nanoelectronic devices that exhibit new electrical properties such as nonlinearity [63]. On this basis, TBJs can be useful in mesoscopic analogue and digital circuits. The following provides a demonstration of a TBJ SR latch showing that TBJs can be employed as novel building blocks in nanoelectronics.

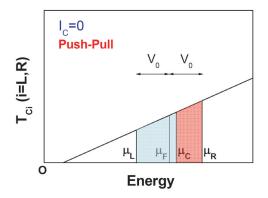

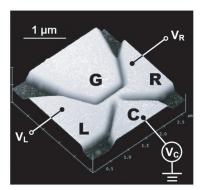

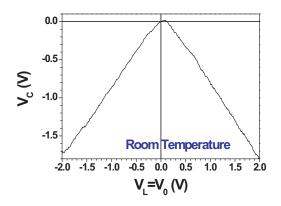

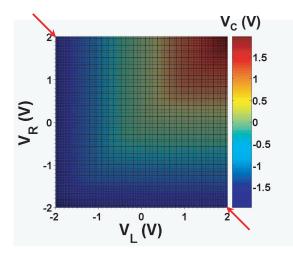

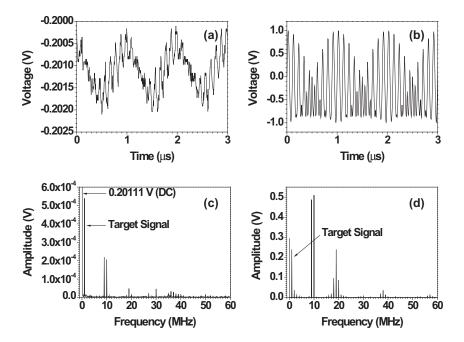

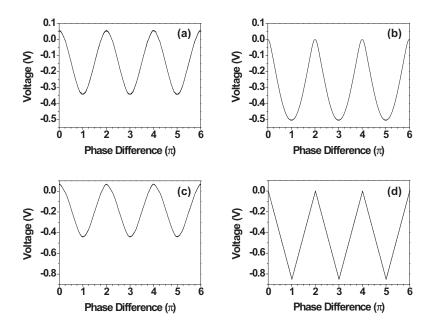

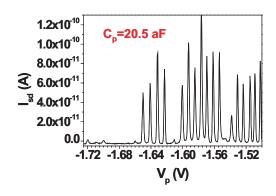

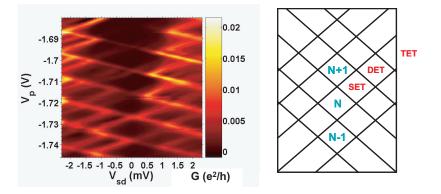

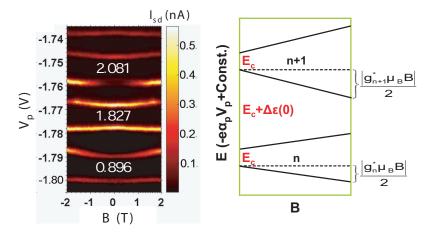

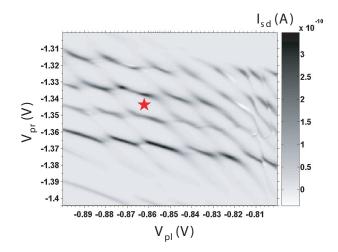

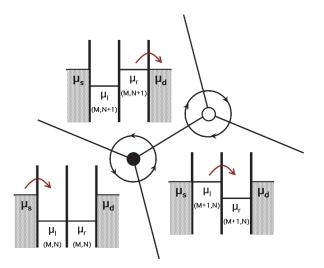

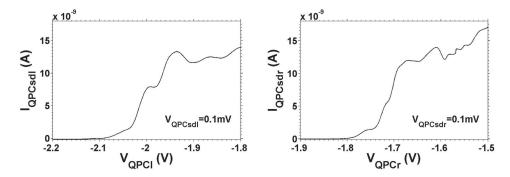

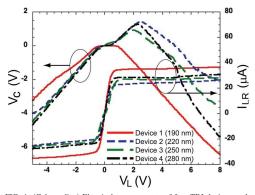

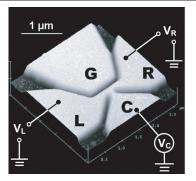

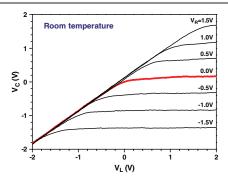

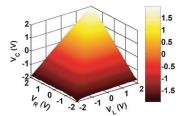

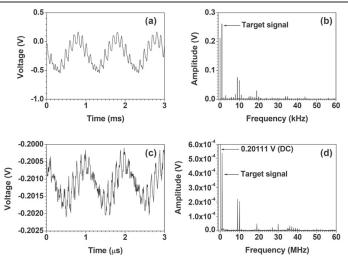

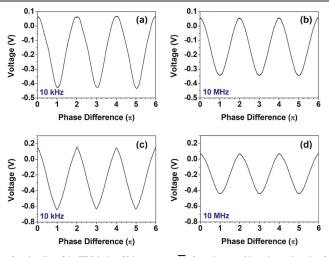

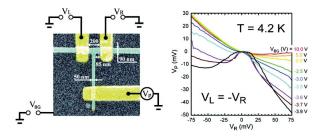

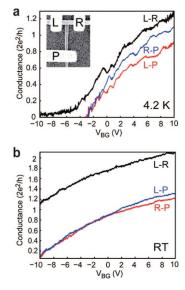

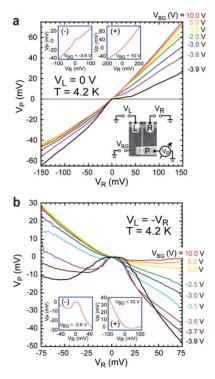

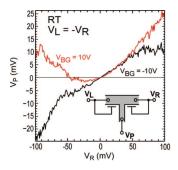

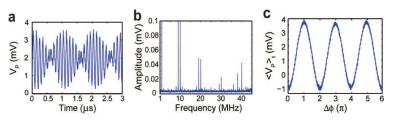

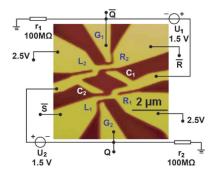

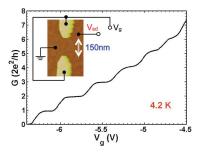

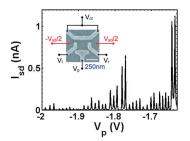

#### 4.1 Three-terminal ballistic junctions in InGaAs/InP