Integrated Transmitters for Cellular User Equipment-Wideband CMOS Power Amplifiers and Antenna Impedance Tuners

Lindstrand, Jonas

2019

Document Version: Publisher's PDF, also known as Version of record

Link to publication

Citation for published version (APA):

Lindstrand, J. (2019). Integrated Transmitters for Cellular User Equipment–Wideband CMOS Power Amplifiers and Antenna Impedance Tuners (1 ed.). Lund University, Faculty of Engineering.

Total number of authors:

Creative Commons License: Unspecified

Unless other specific re-use rights are stated the following general rights apply: Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

• Users may download and print one copy of any publication from the public portal for the purpose of private study

- or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal

Read more about Creative commons licenses: https://creativecommons.org/licenses/

If you believe that this document breaches copyright please contact us providing details, and we will remove access to the work immediately and investigate your claim.

# Integrated Transmitters for Cellular User Equipment–Wideband CMOS Power Amplifiers and Antenna Impedance Tuners

JONAS LINDSTRAND

DEPARTMENT OF ELECTRICAL AND INFORMATION TECHNOLOGY

FACULTY OF ENGINEERING | LTH | LUND UNIVERSITY

# Integrated Transmitters for Cellular User Equipment—Wideband CMOS Power Amplifiers and Antenna Impedance Tuners

Jonas Lindstrand

#### DOCTORAL DISSERTATION

by due permission of the Faculty of Engineering, Department of Electrical and Information Technology, Lund University, Sweden.

To be defended on Friday, November 8, 2019 at 9.15 in lecture hall E:1406, Department of Electrical and Information Technology, Ole Römers väg 3, 223 63 Lund Sweden

Faculty opponent

Professor Timo Rahkonen, University of Oulu, Oulu, Finland

| Organization                                        | Document name                    |

|-----------------------------------------------------|----------------------------------|

| LUND UNIVERSITY                                     | DOCTORAL DISSERTATION            |

| Department of Electrical and Information Technology |                                  |

| P.O. Box 118                                        |                                  |

| 221 00 Lund                                         |                                  |

| Sweden                                              |                                  |

|                                                     | Date of issue: October 2019      |

| Author: Jonas Lindstrand                            | Sponsoring organization: VINNOVA |

|                                                     |                                  |

Title and subtitle: Integrated Transmitters for Cellular User Equipment-Wideband CMOS Power Amplifiers and Antenna Impedance Tuners

#### Abstract

The digital cellular systems era started about thirty years ago with the release of the first digital cellphones. These first digital cellphones were very different from today's slim and esthetic cellular pocket computers. They were not mass-produced in million units a day, and they were designed for radio performance rather than appearance. Today, all components are integrated inside the mobile phone to enable a product for the masses and not only the lucky few. For the radio performance this makes a large difference, especially the cellphones interaction with the user, which has a tendency to load the integrated antennas. This loading of the antennas means that the electronics inside the cellphone works sub-optimally, and a decrease in radio performance inevitable, resulting in increased power consumption and reduced data rates. This problem can, however, be reduced by a concept called adaptive antenna impedance matching. This compensates for antenna loading effects, so that the electronics inside the cellphone can still operate with a close to optimum impedance, although the antenna impedance is changed due to user interaction. For adaptive impedance matching, the key component is the so called impedance tuner, which is studied, designed, and evaluated in this thesis. The requirements on this impedance tuner are very high, with low insertion loss, in-band distortion, out-of-band distortion, high tunability, and good power handling. The cosh should also be as low as possible, which means that it should be implemented in a CMOS based technology suitable for mass-production. In this thesis, an impedance tuner is therefore designed and implemented in a CMOS-SOI technology. It has been verified to fulfill the requirements for use in a modern cellphone, with all measurements of key merits indicating high performance. Finally, it is worth to mention that this impedance tuner has also been used in a different project, where adaptive impedance matching was used in MIMO channel measurements with real cellphone users,

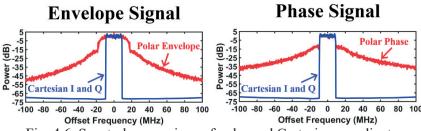

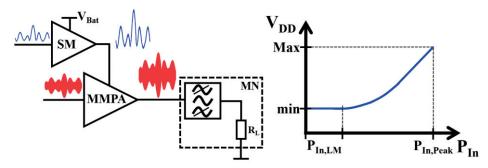

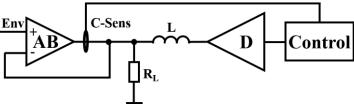

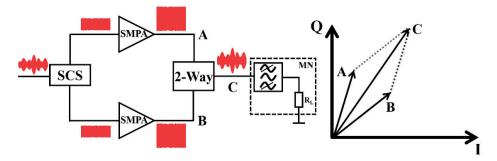

The range of frequencies used for cellular communication has increased over the years, and today a large part of the so called sub-6 GHz frequency range is used. Most of the wireless services we have today use this decade wide frequency range (~600-6000 MHz), and although it is a wide frequency range, the spectrum is congested with a high density of communication. The circuits used to communicate in the sub-6 GHz bands must therefore have high RF-performance, and they should also be low cost since a large number of circuits is used to cover the complete frequency range. Difficulties reducing the cost per frequency band has drastically increased the cost of today's cellphones. This thesis therefore proposes an alternative concept for the power amplifier, the key component in the transmitter of the mobile phone, with the goal to reduce the cost of and the number of power amplifier circuits required to cover the complete sub-6 GHz range. The core of the concept was first designed and verified by measurements, an injection-locked power amplifier with supply modulation and dynamic transistor bias, resulting in high efficiency and bandwidth. To further reduce the cost of the cellphone more of the transmitter functionality, i.e. the frequency up-conversion, was added to the power amplifier circuit, which also improved the overall transmitter performance. Furthermore, a new version of polar modulation is proposed, to reduce the baseband signal bandwidth expansion, which polar modulation is notorious for. The reduction in bandwidth expansion decreases the overall power consumption of the transmitter, since the baseband circuits can then have lower bandwidth and clock-frequency. To further reduce the number of power amplifier circuits needed to cover the entire sub-6 GHz range, the bandwidth of the circuit was improved using a new higher order output matching network, together with a dual output power amplifier, resulting in a circuit that can operate with high performance over the complete sub-6 GHz frequency range. The

Key words: CMOS, LTE, Impedance tuner, Injection lock, Power amplifier, Efficiency, Polar bandwidth expansion, and Multiband

| Classification system and/or index terms (if any)     |                    |                                   |

|-------------------------------------------------------|--------------------|-----------------------------------|

| Supplementary bibliographical information             |                    | Language: English                 |

|                                                       |                    |                                   |

| ISSN and key title: Series of licentiate and doctoral | al dissertations   | ISBN (digital): 978-91-7895-307-3 |

| 1654-790X; No. 127                                    |                    | ISBN (printed): 978-91-7895-306-6 |

| Recipient's notes                                     | Number of          | Price                             |

|                                                       | pages 138          |                                   |

|                                                       | Security classific | cation                            |

I, the undersigned, being the copyright owner of the abstract of the above-mentioned dissertation, hereby grant to all reference sources permission to publish and disseminate the abstract of the above-mentioned dissertation.

# Integrated Transmitters for Cellular User Equipment—Wideband CMOS Power Amplifiers and Antenna Impedance Tuners

**Doctoral Thesis**

Jonas Lindstrand

Department of Electrical and Information Technology Faculty of Engineering, Lund University Lund, Sweden 2019

#### © Jonas Lindstrand

Department of Electrical and Information Technology Lund University P.O Box 118 ISBN 978-91-7895-306-6 ISSN 1654-790X; No. 127

Printed in Sweden by *Tryckeriet i E-huset*, Lund University Lund 2019

#### Abstract

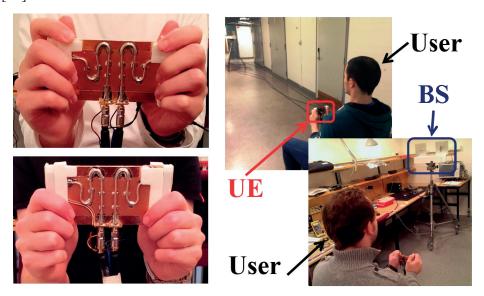

The digital cellular systems era started about thirty years ago with the release of the first digital cellphones. These first digital cellphones were very different from today's slim and esthetic cellular pocket computers. They were not mass-produced in million units a day, and they were designed for radio performance rather than appearance. Today, all components are integrated inside the mobile phone to enable a product for the masses and not only the lucky few. For the radio performance this makes a large difference, especially the cellphones interaction with the user, which has a tendency to load the integrated antennas. This loading of the antennas means that the electronics inside the cellphone works sub-optimally, and a decrease in radio performance is inevitable, resulting in increased power consumption and reduced data rates. This problem can, however, be reduced by a concept called adaptive antenna impedance matching. This compensates for antenna loading effects, so that the electronics inside the cellphone can still operate with a close to optimum impedance, although the antenna impedance is changed due to user interaction. For adaptive impedance matching, the key component is the so called impedance tuner, which is studied, designed, and evaluated in this thesis. The requirements on this impedance tuner are very high, with low insertion loss, in-band distortion, out-ofband distortion, high tunability, and good power handling. The cost should also be as low as possible, which means that it should be implemented in a CMOS based technology suitable for mass-production. In this thesis, an impedance tuner is therefore designed and implemented in a CMOS-SOI technology. It has been verified to fulfill the requirements for use in a modern cellphone, with all measurements of key merits indicating high performance. Finally, it is worth to mention that this impedance tuner has also been used in a different project, where adaptive impedance matching was used in MIMO channel measurements with real cellphone users, but that project is outside the scope of this thesis.

The range of frequencies used for cellular communication has increased over the years, and today a large part of the so called sub-6 GHz frequency range is used. Most of the wireless services we have today use this decade wide frequency range (~600-6000 MHz), and although it is a wide frequency range, the spectrum is congested with a high density of communication. The circuits used to communicate in the sub-6 GHz bands must therefore have high RF-performance, and they should also be low cost since a large number of circuits is used to cover the complete frequency range. Difficulties reducing the cost per frequency band has drastically increased the cost of today's cellphones. This thesis therefore proposes an alternative concept for the power amplifier, the key component in the transmitter of the mobile phone, with the goal to reduce the cost of and the number of power amplifier circuits required to cover the complete sub-6 GHz range. The core of the concept was first designed and verified by measurements, an injection-locked power

amplifier with supply modulation and dynamic transistor bias, resulting in high efficiency and bandwidth. To further reduce the cost of the cellphone more of the transmitter functionality, i.e. the frequency up-conversion, was added to the power amplifier circuit, which also improved the overall transmitter performance. Furthermore, a new version of polar modulation is proposed, to reduce the baseband signal bandwidth expansion, which polar modulation is notorious for. The reduction in bandwidth expansion decreases the overall power consumption of the transmitter, since the baseband circuits can then have lower bandwidth and clock-frequency. To further reduce the number of power amplifier circuits needed to cover the entire sub-6 GHz range, the bandwidth of the circuit was improved using a new higher order output matching network, together with a dual output power amplifier, resulting in a circuit that can operate with high performance over the complete sub-6 GHz frequency range. The proposed solutions in this thesis can reduce the number of ICs in cellular devices, which benefits not only the production cost, but also has positive effects on the environment.

## Populärvetenskaplig sammanfattning

Under de tre senaste årtiondena har mobilindustrin utvecklats och utvecklat trådlösa system som blivit nödvändiga i vår vardag. Man kan säga att denna resa började med 2G, vilket faktiskt är den andra generationen för den mobila kommunikationen, men den första generationen som baserades på signalbehandling i den digitala fortsatte resan sedan har digitalisering kommunikationssystem varit en stark trend, vilket innebär att det mesta av funktionaliteten nu är digital, och denna trend inom mobilindustrin är en del av trenden i dagens samhälle med genomgående digitalisering. Men själva de trådlösa signalerna är fortfarande analoga radiovågor som kommuniceras över etern med en fysisk antenn som bygger på samma principer som en vanlig antenn till radion eller TVn. Inuti mobiltelefonen finns dessa antenner kvar, men de syns inte från utsidan utan är inbyggda i telefonen, vilket har strömlinjeformat det estetiska utseendet. Denna integrering av antenner i dagens tunna mobiltelefoner har gett en ny utmaning, och det är hur antennerna fungerar vid beröring från användarens händer och huvud. Detta gör att elektroniken inte arbetar som det är tänkt, och telefonen kan då dra mer ström så att den måste laddas oftare. Men det finns en metod som kallas adaptiv matchning som kan minimera detta problem. Adaptiv matchning innebär att antennen är oförändrad ur elektronikens synvinkel, det vill säga för den elektronik som finns inuti mobiltelefonen. Ett huvudspår i denna avhandling har varit att undersöka så kallade impedanstuners, som är den viktigaste elektronikkomponenten för adaptiv matchning, och slutresultaten visar på en signifikant vinst i minskad effektförbrukning eller ökad datahastighet. De viktigaste egenskaperna för en impedanstuner, förutom att kompensera för antennens variationer, är att den ska kosta så lite pengar så möjligt vilket betyder att den måste byggas med halvledare i CMOS (som är billiga vid massproduktion), och att elektroniken i impedanstunern endast minimalt får förändra de analoga radiovågorna i form av dämpning och förvrängning av signalen. Denna avhandling uppvisar en impedanstuner i CMOS som uppfyller dessa krav.

Frekvensspektrumet för mobil kommunikation utökas ständigt, men delas i dagsläget mellan 2G, 3G, 4G, och snart kommer också 5G, och det kan därmed sägas att spektrumet är väldigt fullt. Detta betyder att kraven på elektroniken i en mobiltelefon är mycket höga, och att det dessutom behövs mer elektronik för att täcka många frekvensområden. Som en direkt konsekvens har totalkostnaden per mobiltelefon ökat. För att försöka minska kostnaden har därför en alternativ lösning för den dyraste komponenten föreslagits i denna avhandling. Komponenten är effektförstärkaren, som dessutom är den viktigaste byggstenen i en mobil sändare, och en av de största energiförbrukarna i en mobiltelefon och vars prestanda därför är centrala för att öka tiden mellan laddningarna. Effektförstärkaren måste med

precision förstärka radiosignalerna innan de omvandlas till radiovågor i antennen, vilket måste ske med så lite strömförbrukning som möjligt, och komponenten i sig måste också ha en så låg kostnad som möjligt. Den alternativa lösning för effektförstärkare som tagits fram i avhandlingen har därför utvecklats för låg strömförbrukning samt för att uppfylla precisionskraven för mobil kommunikation, och CMOS har använts för att den potentiella kostnaden ska vara minimal vid massproduktion. För att vidareutveckla konceptet har ett elektroniksystem för sändare konstruerats som innehåller mer funktionalitet än endast den hos effektförstärkaren. Detta system ger generellt lägre strömförbrukning och leder också till att färre komponenter behövs vilket minskar produktionskostnaderna. Till systemet har också en ny signalbehandlingsalgoritm tagit fram vars huvudsyfte är att ytterligare sänka strömförbrukningen. Ett annat sätt att minska kostnaden är att minimera antalet dyra komponenter i mobiltelefonen genom att minska antalet effektförstärkare. Detta har också gjorts i denna avhandling genom att konstruera och utvärdera en effektförstärkare som har likvärdig prestanda i alla frekvensband där det finns mobil kommunikation i dagsläget. Som slutsats kan det nämnas att de kretslösningar som tagits fram har en hög komplexitet men också hög potential ur en kostnadssynvinkel och ur ett miljöperspektiv, för när antalet elektronikkomponenter minimeras per konsumentprodukt kommer kostnaden och miljöpåverkan från själva produktionen att minska.

### **Table of Contents**

| A | de la |                                                       | I    |

|---|-------------------------------------------|-------------------------------------------------------|------|

| P | opulärvetenska                            | plig sammanfattning                                   | III  |

| T | able of Conten                            | ts                                                    | V    |

| P | reface                                    |                                                       | IX   |

| A | cknowledgeme                              | nts                                                   | XIII |

|   | e                                         | tions                                                 |      |

|   |                                           |                                                       |      |

|   | •                                         |                                                       |      |

| P | art I General l                           | ntroduction                                           | 1    |

| 1 | Introduction                              | n                                                     | 3    |

| 2 | Cellular III                              | E Transcievers                                        | 9    |

| _ |                                           | band Transceivers                                     |      |

|   |                                           | cuit's for the Duplex Function                        |      |

|   |                                           | omodyne Receiver                                      |      |

|   |                                           | ic Noise Properties                                   |      |

|   |                                           | ic Linearity Properties                               |      |

|   |                                           | ss-Modulation Distortion in the Homodyne $R_X$        |      |

|   |                                           | iprocal Mixing and Mixer Issues in the Homodyne $R_X$ |      |

|   |                                           | omodyne T <sub>x</sub>                                |      |

|   |                                           | -Interference from the T <sub>x</sub> in FDD          |      |

|   |                                           | inearity and Noise                                    |      |

| 3 | User-Intera                               | ection and Adaptive Matching in UE                    | 27   |

|   | 3.1 The E                                 | ffect of User-Interaction on Antenna Impedance        | 27   |

|   |                                           | ive Impedance Tuners                                  |      |

|   | 3.3 Imped                                 | lance Tuners in CMOS-SOI                              | 31   |

|   |                                           | cuit Design                                           |      |

|   |                                           | cuit Verification by Measurement                      |      |

|   |                                           | Interactions in a MIMO Environment                    |      |

|   |                                           | Experimental MIMO UE                                  |      |

|   | 3.4.2 The                                 | MIMO-Channel Measurement                              | 41   |

| 4 |                                           | Enhancement Techniques for UE Transmitters            |      |

|   |                                           | luction to Power Amplifier Classes                    |      |

|   |                                           | ency Enhancement Circuits and Techniques              |      |

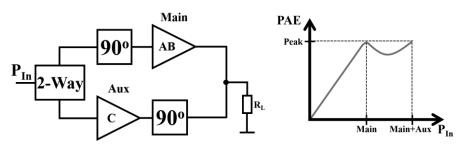

|   |                                           | Doherty Amplifier                                     |      |

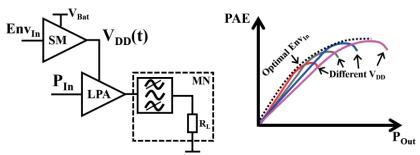

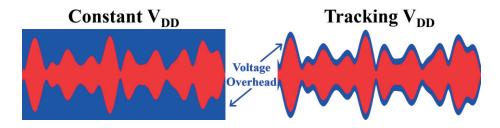

|   |                                           | Envelope Tracking System                              |      |

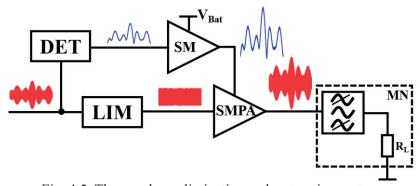

|   | 4.2.3 The                                 | Envelope Elimination and Restoration System           | 49   |

| 4.2.4       | The Hybrid and Mixed-Mode Systems with Supply Mod   | ulation 51 |

|-------------|-----------------------------------------------------|------------|

| 4.2.5       | The Supply Modulator                                | 52         |

| 4.2.6       | Linear Amplification using Nonlinear Components     |            |

| 4.2.7       | Digital Pre-Distortion                              |            |

| 5 Inject    | ion-Lock Theory and Techniques                      | 57         |

|             | ntroduction                                         |            |

| 5.2 I       | Dynamic Biasing and Supply Modulation of the ILPA   | 58         |

| 5.3         | Theory for the Injection-Locked PA with Supply Modu | lation 60  |

|             | Conclusion                                          |            |

| 6 Sumn      | nary with Conclusions and Future Work               | 67         |

| Appendix A  | A: Basic Injection-Lock Theory                      | 69         |

| References  |                                                     | 75         |

| Part II Inc | cluded papers                                       | 85         |

| Summary o   | of included papers                                  | 87         |

| Paper I:    |                                                     | 91         |

| Paper II:   |                                                     | 97         |

| Paper III:  |                                                     | 103        |

| Paper IV:   |                                                     | 119        |

| Paper V:    |                                                     | 133        |

#### **Preface**

My journey into the world of electrical engineering started already in my boy room growing up, and it involved music, electric guitars, and electric guitar gear. I did not play the instruments myself, the fascination for me was all the equipment including amplifiers, speakers, and effects based on distortion and delays. My keen interest in these things pointed me in the direction of Analog electronics and later in my undergraduate studies towards Radio electronics in CMOS technology. The grand idea of me getting a good education was always spoken of by my maternal grandmother and she always encouraged me to go down this path, which I apparently did. Her belief started a summer evening over thirty years ago, among some stunned family friends and a grand design built from LEGO.

As this journey ends and a new one begins, there is some time for reflection. This journey in science and engineering resulted in a handful of publications included as the main body of this thesis (Papers [I-V]), and also in additional publications where I have contributed to the research of others (Papers [VI-IX]). Furthermore, this project was funded by the Vinnova Industrial Excellence Center – System Design on Silicon (SoS) and the Excellence Center at Linköping – Lund in Information Technology (ELLIIT), which have a close relation to the Swedish industry. Through this relation two patent applications were filed, and as of today both applications are granted patents [i, ii]. I would like to end with a citation, well-known to me even long before I started this journey of circuits and systems:

<sup>&</sup>quot;Success is a journey, not a destination. The doing is often more important than the outcome"

<sup>-</sup>Arthur Ashe, American Athlete

#### **Included publications**

- J. Lindstrand, I. Vasilev, and H. Sjöland, "A low band cellular terminal antenna impedance tuner in 130nm CMOS-SOI technology," in Proc. European Solid-State Circuit Conference, Venice, Italy, Sept. 2014, pp. 459-462.

- II. J. Lindstrand, C. Bryant, M. Törmänen, and H. Sjöland, "A 1.6-2.6GHz 29dBm injection-locked power amplifier with 64% peak PAE in 65nm CMOS," in Proc. European Solid-State Circuit Conference, Helsinki, Finland, Sept. 2011, pp. 299–302.

- III. J. Lindstrand, M. Törmänen, and H. Sjöland, "An injection-locked power up-converter in 65-nm CMOS for cellular applications," in IEEE Transactions on Microwave Theory and Techniques, vol. 67, no. 3, pp. 1065–1077, March 2019.

- IV. J. Lindstrand, M. Törmänen, and H. Sjöland, "Origin attraction a technique to reduce signal bandwidth in polar transmitters," Submitted to IEEE Transactions on Circuits and Systems I: Regular Papers.

- V. J. Lindstrand, M. Törmänen, and H. Sjöland, "A Decade Frequency Range CMOS Power Amplifier for Sub-6 GHz Cellular Terminals," Accepted for Publication in *IEEE Microwave and Wireless Components Letters*.

#### **Related publications**

- VI. I. Vasilev, J. Lindstrand, V. Plicanic, H. Sjöland and B. K. Lau, "Experimental Investigation of Adaptive Impedance Matching for a MIMO Terminal With CMOS-SOI Tuners," *in IEEE Transactions on Microwave Theory and Techniques*, vol. 64, no. 5, pp. 1622-1633, May 2016.

- VII. C. Bryant, J. Lindstrand, H. Sjöland and M. Törmänen, "A 70 and 210 GHz LO generator in 65nm CMOS," *in Proc. 2012 IEEE International Symposium on Radio-Frequency Integration Technology*, Singapore, 2012, pp. 195-197.

- VIII. M. Törmänen, J. Lindstrand and H. Sjöland, "A 13dBm 60GHz-band injection locked PA with 36% PAE in 65nm CMOS," *in Proc. Asia-Pacific Microwave Conference 2011*, Melbourne, Australia, 2011, pp. 1-4.

- IX. M. Törmänen, A. Axholt, J. Lindstrand and H. Sjöland, "A 2GHz Tx LO generation circuit with active PPF and 3/2 divider in 65nm CMOS," *in Proc.* 2011 International Symposium on Integrated Circuits, Singapore, 2011, pp. 208-211.

#### **Approved Patents**

- i. J. Lindstrand, C. Bryant, and H. Sjöland, "High efficiency power amplifier," Okt. 2013. US Patent 8,554,162

- ii. C. Bryant, J. Lindstrand, and H. Sjöland, "Transceiver front-end," Sept. 2017. US Patent 9,774,365

#### Acknowledgements

First of all I would like to extend my gratitude to my supervisor, Professor Henrik Sjöland. He always appears to know something about pretty much everything, a natural in technical solutions, and he has real prowess in technical and academic writing. It should also be mentioned that Professor Sjöland and his connections provided me a very rare and game changing master thesis opportunity and he also gave me the chance to pursue a PhD degree, and I am always grateful to him for these long term investments in me. I would also like to thank my assisting supervisor, Associate Professor Markus Törmänen. For teaching me some very important skills in the beginning of my PhD-studies, also for being a good friend, for all your support, and for always believing in me. My sincerest gratitude goes to the head of the department, Professor Daniel Sjöberg, without your guidance and support this thesis would never have been written. To the people I have cooperated with in the adaptive matching project, the pleasure was all mine and thank you for everything, Professor Buon Kiong (Vincent) Lau and my PhD student friend Doctor Ivaylo Vasilev. I would also like to acknowledge my two favorite educators, Associate Professor Pietro Andreani and Lecturer Göran Jönsson, especially for passing on your invaluable knowledge and for being a big inspiration. To my past and present fellow PhD students and group members, some often enclosed in your own world, myself often included, and to all of you that I interacted with over the years, you have my sincerest appreciation and some of you are really good and genuine people. I can add that Earth is a big place, but somehow the world is yet so small and hopefully I will interact with some of you in the future. My grateful thanks goes to Elisabeth Nordström, Andreas Johansson, Göran Jönsson, Erik Jonsson, Stefan Molund, and Sirvan Abdollah Poor of the technical and administrative staff for all the help over the years. I would also like to thank the retired members of the technical and administrative staff, Pia Bruhn and Lars Hedenstjerna, whom always have a special place in my heart.

I send all my love to my parents, Berit and Jan, for always being there, for all your support, and you have really been good and fair parents. Your Swedish way rarely makes you speak your mind, but you always show your appreciation with real actions and real commitments, and these are the things that really matters at the end of the day. I should also add without being humble, that I inherited my mother's determination and patience, my father's creativity and innovative ways to problem solving, and without these characteristics it would have been impossible for me to reach this level of education within the field of engineering. To my brother, Philip, I always try to send as much love as possible, he is the biggest catalyst of me starting this journey. It is his love and passion for music and electric guitars that sparked my love and passion for electric devices and their details.

I would also like to thank the American side of my family and although you live on the other side of the planet, you are always here with me in spirit. To Eileen, David, and Paul, your door is always open and your homes have been a refuge for me throughout the years, a place away from PhD student life and its implications. My sincerest appreciation to Inger Elman, a very close family friend and a big inspiration, energetic supporter, and role model.

Last but not least to my love, Elise, you have always rocked my world and when I am with you I always feel like a winner. You are my biggest inspiration to say the least, your open-mindedness, your intelligence, your efficiency, and your ability to learn and solve the impossible. Throughout the years, your love and support has made completion of this journey possible, and even through all these highs and lows. Somehow, as the turmoil of daily life has pushed us very close to the physical and mental breaking point at times, but our relationship and love for each other has always helped us prevail and only to make our love and relationship even stronger.

Jonas Lindstrand

Is Late

Lund, 2019-09-19

### List of Abbreviations

2G 2<sup>nd</sup> Generation cellular systems

2-Way Two-Way combiner

3G 3<sup>rd</sup> Generation cellular systems

3GPP 3G Partnership Project

4G 4<sup>th</sup> Generation cellular systems

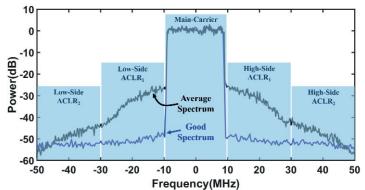

ACLR Adjacent Channel Leakage Ratio

ADC Analog to Digital Converter

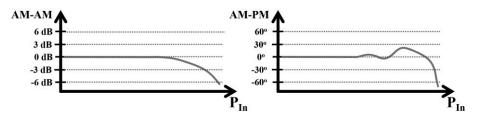

AM-AM Amplitude-Modulation to Amplitude-Modulation distortion

AM-PM Amplitude-Modulation to Phase-Modulation distortion

Aux Auxiliary

BALUN BALanced to UNbalanced

BAW Bulk Acoustic Wave

BB Base-Band

BER Bit Error Rate

BOM Bill Of Material

BS Base-Station

BW BandWidth

BWE BandWidth Expansion

CM Common Mode

CMOS Complementary Metal Oxide Semiconductor

CMRR Common Mode Rejection Ratio

CP Compression Point

C-Sens Current-Sensor/Sensing

DAC Digital to Analog Converter

DCO Digitally Controlled Oscillator

DET envelope DETector

DL Down-Link

DPD Digital Pre-Distortion

DUT Device Under Test

EER Envelope Elimination and Restoration

EM Electro-Magnetic

ET Envelope Tracking

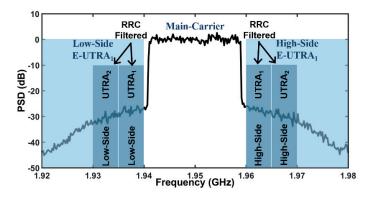

E-UTRA Evolved UMTS Terrestrial Radio Access

EV Error Vector

EVM Error Vector Magnitude

F noise Factor

FDD Frequency Division Duplex

FFP Feed-Forward Path

G<sub>P</sub> Power Gain

GaAs Gallium Arsenide

GMSK Gaussian Minimum Shift Keying

GSM Global System for Mobile communication

Gen signal Generator

H-Band High-Band

HD Harmonic Distortion

H-EER Hybrid Envelope Elimination and Restoration

I<sub>BB</sub> In-phase Base-BandIC Integrated Circuit

ICP Input referred Compression Point

ICP<sub>1</sub> 1 dB Input referred Compression Point

IIP<sub>x</sub> Input referred Intercept Point of the x<sup>th</sup> order

II. Insertion-Loss

ILPA Injection-Locked PA

IM<sub>2</sub> 2<sup>nd</sup>-order Inter-Modulation product

IM<sub>3</sub> 3<sup>rd</sup>-order Inter-Modulation product

IMD Inter-Modulation Distortion

$IMD_2$   $2^{nd}$ -order Inter-Modulation Distortion  $IMD_3$   $3^{rd}$ -order Inter-Modulation Distortion

IMD<sub>5</sub> 5<sup>th</sup>-order Inter-Modulation Distortion

IP Intercept Point

IP<sub>3</sub> 3<sup>rd</sup>-order Intercept Point

ISI Inter Symbol Interference

ISO ISOlation

L-Band Low-Band

LIM LIMiter

LINC Linear amplification using Nonlinear Components

L-ISO Low-ISOlation

LNA Low Noise Amplifier

LO Local Oscillator

LPA Linear class Power Amplifier

LTE Long Term Evolution

LUT Look-Up Table

MEMS Micro-Electro-Mechanical Systems

MIMO Multiple Input Multiple Output

ML Matching-Loss

MMPA Mixed-Mode/class Power Amplifier

MN Matching Network

MODEM MOdulator-DEModulator

MOM Metal-Oxide-Metal

NF Noise Figure

OCP Output referred Compression Point

OFDM Orthogonal Frequency-Division Multiplexing

OIP<sub>x</sub> Output referred Intercept Point of the x<sup>th</sup> order

PA Power Amplifier

PAE Power Added Efficiency

PAPR Peak-to-Average Power Ratio

PC Personal Computer

PCB Printed Circuit Board

PLL Phased Locked Loop

PPA Pre-Power Amplifier

PSK Phase Shift Keying

PWM Pulse Width Modulation

Q Quality factor

Q<sub>BB</sub> Quadrature-phase Base-Band

QAM Quadrature Amplitude Modulation

QVCO Quadrature Voltage Controlled Oscillator

R<sub>X</sub> Receiver

RF Radio Frequency

RL Resistive-Loss

RRC Root Raised Cosine

SAW Surface Acoustic Wave

SC-FDMA Single-Carrier Frequency-Division Multiple Access

SCS Signal Component Separator

SiGe Silicon Germanium

SM Supply Modulator

SMPA Switched-Mode Power Amplifier

SNR Signal-to-Noise Ratio

SOC System On Chip

SOI Silicon On Isolator

SOS Silicon On Sapphire

SRF Self-Resonance Frequency

STM ST-Microelectronics

T Transformer

T<sub>x</sub> Transmitter

T<sub>X</sub>-BB Transmitter Base-Band

TDD Time Division Duplex

T/R Transmit/Receive

T<sub>X</sub>-Synth Transmitter Synthesizer

UE User Equipment

UL Up-Link

UMTS Universal Mobile Telecommunications System

UTRA UMTS Terrestrial Radio Access

VCO Voltage Controlled Oscillator

VNA Vector Network Analyzer

VSWR Voltage Standing Wave Ratio

W-CDMA Wideband Code Division Multiple Access

Wi-Fi Wireless Fidelity

WLAN Wireless Local Area Network

XMD CROSS-Modulation Distortion

ZVS Zero-Voltage Switching

# **List of Symbols**

$\Gamma$  Reflection coefficient

$\eta_{PA}$  Power amplifier drain efficiency

$\eta_{SM}$  Supply modulator drain efficiency

$\eta_{tot}$  Total drain efficiency

$\phi(t)$  Time-variant phase signal

$\omega$  Angular frequency

A(t) Time-variant amplitude signal

$A_{Duplex}^{f=Rx}$  Duplexer attenuation in the receive band

$C_{ds}$  Drain-source capacitance

$C_{gd}$  Gate-drain capacitance  $C_{gs}$  Gate-source capacitance

Env(t) Time-variant envelope signal

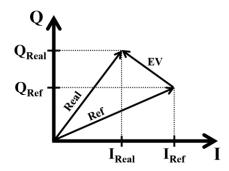

EV(I,Q) Error Vector in the Cartesian domain

$f_{max}$  Maximum oscillation frequency

$f_T$  Transit frequency  $F_{Tot}$  Total noise factor

$g_d$  Small-signal drain conductance  $G_m$  Large-signal transconductance  $g_m$  Small-signal transconductance

$P_{DC}$  DC power consumption

$\overline{P_{EV}}$  Average power of the Error Vector

$P_{Noise-Tx}^{f=Rx}$  Transmitter output noise in the receive band

$\overline{P_{Ref}}$  Average power of the Reference Vector

$P_{Tx}^{f=Tx}$  Transmitter output power

$r_{ds}$  Small-signal drain-source resistance

$R_L$  Load resistance

$r_n$  Small-signal negative resistance

$R_{off}$  Off-resistance

$R_{on}$  Triode on-resistance

$t_s$  Symbol time

# Part I General Introduction

# CHAPTER 1

#### 1 Introduction

During the last three decades digital wireless communication has evolved rapidly, with a user maximum data rate going from 270 kilobits per second (kbps) in the 2<sup>nd</sup> Generation cellular systems (2G) or Global System for Mobile communication (GSM) [1, 2] to today's approximately 100-400 megabits per second (Mbps) in the 4<sup>th</sup> Generation cellular systems (4G) or Long Term Evolution (LTE) [3]. The data rates have thus increased about 1000 times. The main driving force in this dramatic development has been Moore's Law [4], i.e. the exponential down-scaling of features-sizes in the most significant semiconductor technology for electronic consumer products, which is the Complementary Metal Oxide Semiconductor (CMOS) technology. This exponential down-scaling in features-sizes means that the digital functionality per unit area is doubled every two years, and circuit speed is also increased, best observed as the increase in Personal Computer (PC) processor clock frequency during the 1990's [5]. In the beginning of digital wireless communication, the CMOS-scaling only effected the digital blocks since all the analog blocks were implemented in specialized technologies like as GaAs[6] and SiGe[7], which had superior analog performance during those days, and still have better performance in some key aspects like gain, noise, linearity and voltage breakdown. However, during the 3<sup>rd</sup> Generation (3G) or Universal Mobile Telecommunications System (UMTS)/Wideband Code Division Multiple Access (W-CDMA) era in the late 1990's, due to scaling of CMOS it was now possible to use the technology to also implement the analog- and Radio Frequency (RF)-blocks, and the main reason was that the CMOS processes now had enough speed (ft and f<sub>max</sub>). By implementing all building blocks in CMOS, complete System On Chip (SOC) solutions were possible and the main feature was that digital, mixed-signal, analog, and RF circuits all could be implemented on the same die. This opened-up the door for wireless products to the main advantage of CMOS technology, the ability to mass-produce chips and also to reduce the number of chips in each User Equipment (UE)/Cellphone. The first fully integrated RF SOC in CMOS was developed by Ericsson in the late 1990's, it is known in the world as Bluetooth [8], and as of today Bluetooth is used in the widest range and largest quantities of consumer products ranging from videogames to bed lamps. This is only possible by

implementing the chip in a CMOS process, where the high level of integration and large volume of fabrication makes each sold unit cheap. If other more exotic technologies were to be used the cost would be orders of magnitude higher for the required Integrated Circuit (IC) production. Finally, the main misconception of CMOS though, that it only cost "nickels" and "dimes", is not true. Only with mass-production can each chip unit cost "nickels" and "dimes", and then only if millions and millions of chips are sold.

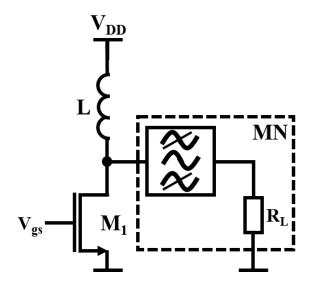

As the development of analog/RF-CMOS circuits continued, the main approach to achieve sufficient performance was circuit design innovation exploiting opportunities and avoiding weaknesses of the technology, and it is still this way today. This is all in the nature of the technology and the market, CMOS is cheap to mass-produce, and yes, speed has increased with Moore's Law, but gain, noise, linearity and voltage breakdown are all getting worse with each CMOS scaling step. The designer has to work with what is available, in Receivers  $(R_X)$  the Low Noise Amplifier (LNA) was a big issue in CMOS, but to achieve sufficient gain and low noise, a noise canceling approach was first disclosed in [9]. Further, the designer can use the main advantage of CMOS down-scaling, which is the high performance of transistors operated as switches. High performance, low noise and high linearity, mixers for frequency conversion in receivers and Transmitters (T<sub>X</sub>) can then be realized. The mixers can be of different types, active [10] or passive [11], current mode [12] or voltage mode [13], and can also include harmonic rejection [14] to counteract the harmonics of the switching waveform. Switches can also be used to create programmable and reconfigurable circuits, switching in and out components or entire building blocks. For instance a Digitally Controlled Oscillator (DCO) [15] can be created by switching in and out capacitors of the resonator according to a digital control number, altering the oscillation frequency. For transmitters Power Amplifiers (PA) with high efficiency can be realized using transistors operating as switches, called Switched-Mode Power Amplifiers (SMPA) [16]. Still, it is very hard to design a power amplifier in CMOS technology. In scaled down technology, where transistors have high speed and excellent switch performance, the voltage breakdown is very low, making it hard to reach high output power. An often used circuit solution is to use stacked transistors, in a so-called stacked-cascode configuration [17]. Two or more transistors stages are then stacked on top of each other, so that the maximum supply voltage of the PA can be the sum of the maximum supply voltage of all stacked stages, i.e. the PA supply voltage is divided among several transistors. Then a higher supply voltage compatible with higher output power can be used, even though the individual transistors cannot handle such voltage levels. By using a stacked-cascode configuration, the performance of each individual transistor is not improved, but the result yields an increased performance for each cascode element added.

From a system point of view, one of the biggest breakthroughs has been the elimination of the Surface Acoustic Wave (SAW) and/or Bulk Acoustic Wave (BAW) filter in both R<sub>X</sub> and T<sub>X</sub>. This elimination became possible by the use of circuit understanding and design, the solution was a passive mixer [11], which has a feature called frequency-translation [18]. In the frequency-translation phenomenon, if an impedance is connected to the mixer low frequency terminal, at the RF mixer terminal the same impedance will appear, but up-converted to RF frequency. The frequency difference, i.e. how much the impedance is translated in frequency, is set by the Local Oscillator (LO) frequency. If the impedance has a low-pass characteristic, like a parallel RC circuit, and if the LO frequency is much higher than the BandWidth (BW) of the low frequency filter, the result is a very narrow RF bandpass filter, which would not be possible to realize on-chip without this technique. Further, by using this solution, tunable selectivity can also be introduced and by changing LO frequency the passband frequency of the filter can be changed as well.

These are examples of only a few circuit solutions/concepts developed over the two and a half decades when CMOS been a serious contender for RFIC implementation.

In the meantime, the wireless system technology has evolved as well, at first GSM only used Gaussian Minimum Shift Keying (GMSK), a type of frequency modulation, but as throughput requirements increased higher order modulation schemes like 8 Phase Shift Keving (PSK), 16 Ouadrature Amplitude Modulation (QAM), 64QAM, 256QAM, were required to increase spectral efficiency, i.e. data rate for a certain bandwidth. To further increase the data-rate the bandwidth has also increased, and to handle the frequency variations of wireless channels Orthogonal Frequency-Division Multiplexing (OFDM) was introduced [19]. Effectively the data is then carried by many closely spaced narrow-banded individually modulated so-called subcarriers. The higher order modulation schemes and OFDM increased spectral efficiency and data rates [20], but the requirements on the hardware in the Modulator-DEModulator (MODEM) also became more stringent. Further, to meet the ever increasing requirements for higher data rate, a multiple antenna technique called Multiple Input Multiple Output (MIMO) was introduced [21]. From basic MIMO theory, the theoretical throughput increases linearly with the number of antenna elements, but this is only true if the antenna signals are uncorrelated [22]. Circuit hardware, on the other hand, must be added to each individual antenna element, increasing cost, power consumption, and complexity. This is a big problem for the handheld UE, powered by batteries. Finally, the main issue with a handheld UE utilizing MIMO is the human touch and the fact that people touch the UE when they use it. To clarify, today's wireless UE has most of its surface area covered by antennas, due to MIMO and the wide range of carrier-frequencies/bands used. If the user touches the UE, it will load the different antennas, and this results in an increase in correlation between the different antennas and an increase in RFIC power consumption, due to the mismatched antenna impedance [23].

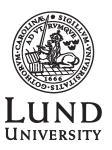

In Fig. 1.1 the evolution of the cellular wireless spectrum over the past three decades is illustrated, 30 years ago GSM mainly used four bands (850 MHz, 900 MHz, 1800 MHz, and 1900 MHz), and in rare cases also 400 MHz and 450 MHz [24], and today with LTE sixty-six (66) bands are used ranging from 450 MHz to 5850 MHz [25]. Further, the LTE standard also has to co-exist with 2G, 3G, and Wireless Local Area Network (WLAN)/Wireless Fidelity (Wi-Fi) which means that the utilized spectrum (450 MHz to 5850 MHz) is at max capacity today. Looking at the cost of cellular devices, the Bill Of Material (BOM) of the MODEM has increased, mainly due to the amount of hardware/components required to cover all the utilized frequency bands, also supporting MIMO. The second problem, since the frequency spectrum is full all unwanted spectral emissions, both in-band and out-of-band, must be kept at a minimum. The third major issue, all the hardware has to be connected on a Printed Circuit Board (PCB) to each antenna, with high quality supply and ground connections, such complex PCB having substantial cost. Finally, all these complex devices have to co-exist in a crowded frequency spectrum, where the margin of error can be considered as small as the feature-size of the individual devises on the CMOS die.

# The Cellular Bands Three Decades Ago

Fig. 1.1. The spectral-evolution of wireless cellular communication.

# CHAPTER 2

### 2 Cellular UE Transcievers

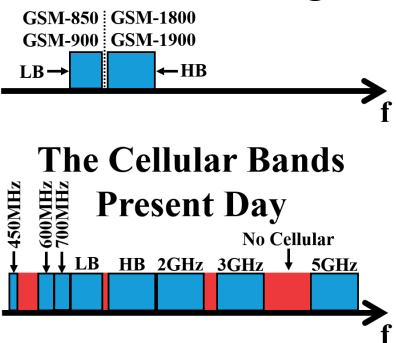

The core of every MODEM is the transceiver, which consist of one or many  $R_X$  and  $T_X$  pairs. In today's transceivers all frequency band are covered by one IC, which can be realized by using separate  $R_X$  and  $T_X$  chains for each band [26], or by using a wideband  $R_X$  and  $T_X$  solution [27]. Further, the major difference between today's transceiver and the transceivers of the past is the frequency conversion, and in present day it is dominated by homodyne/direct conversion architectures [28], whereas in the past heterodyne/IF architectures [29] dominated the transceiver implementation. The main differences are illustrated in Fig 2.1, the homodyne transceiver operates with an LO frequency equal to the RF frequency whereas the heterodyne structure has an LO frequency lower or higher than the RF frequency.

Fig. 2.1. Comparison of homodyne and heterodyne frequency conversion.

The main benefit of the homodyne is that it requires the lowest amounts of off-chip filtering, whereas the heterodyne has a natural isolation between RF and LO (not operating at the same frequency). The main drawback of the homodyne is that it has issues with CROSS-Modulation Distortion (XMD) due to interaction of LO signal leakage and signal-blockers [30] and it is also very susceptible to oscillator pulling [31], whereas the heterodyne requires higher amounts of sharp filters and also more frequency conversion steps. Overall, the homodyne transceiver is more straightforward and it also requires the least amount of off-chip hardware.

#### 2.1 Multi-band Transceivers

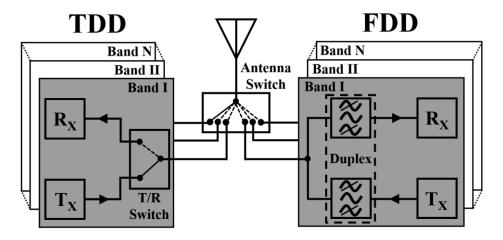

Fig. 2.2. The TDD and FDD multi-band cellular transceiver systems.

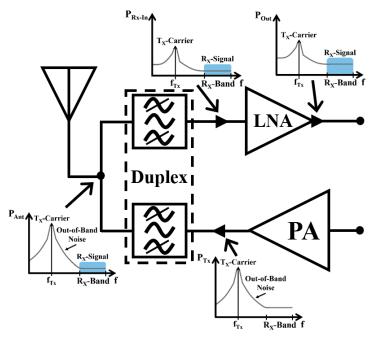

Fig. 2.2 shows a simplified block diagram of a multi-band cellular transceiver, the R<sub>X</sub> (Down-Link [DL]) and T<sub>X</sub> (Up-Link [UL]) can operate at different frequency bands according to both Time Division Duplex (TDD) (for GSM/LTE) and Frequency Division Duplex (FDD) (for W-CDMA/LTE) schemes. In TDD the R<sub>X</sub> and T<sub>X</sub> do not operate simultaneously, and a Transmit/Receive (T/R) switch can thus be used to connect them alternatingly to the antenna. In FDD, on the other hand, the  $T_X$  and  $R_X$  operate simultaneously, but at different frequencies. In order to isolate the signals from the  $T_X$  to the antenna and from the antenna to  $R_X$ , so that strong  $T_X$ signals do not saturate the R<sub>X</sub>, an off-chip duplex filter (duplexer) is generally used in FDD. Such off-chip (SAW or BAW) duplexers are fixed to a specific frequency band. Therefore, switches are used to change operating bands and each duplexer provides the required isolation for each band. The duplexer has three system functions, to isolate the sensitive  $R_X$  from the strong  $T_X$ -carrier, to filter-off the noise in the R<sub>X</sub>-band generated by the T<sub>X</sub>, and to filter-off noise and spurious content to and from the antenna. At the R<sub>X</sub> input the high powered (+27dBm [0.5W], Power Class 2 in LTE) T<sub>X</sub>-carrier signal must be attenuated to not compress the R<sub>X</sub>, the noise from the T<sub>X</sub> is caused mainly by the phase-noise in the local oscillator signal  $(LO_{Tx})$  and thermal noise in the  $T_X$  mixers and some of it ends up in the  $R_X$ -band, and if not suppressed this noise will reduce the ability to receive weak signals, i.e. it will desensitize the  $R_X$ .

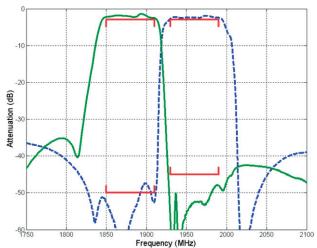

In Fig. 2.3 the frequency characteristic of a SAW duplexer is shown, ISOlation (ISO) of both  $T_X$ -carrier and  $T_X$ -noise, and Insertion-Loss (IL) of both the  $R_X$  and  $T_X$  path to the antenna are shown. As can be seen, the  $T_X$ -carrier isolation (in the  $T_X$ -band) is high (about 50 dB) and the  $T_X$ -noise in the  $T_X$ -band is attenuated by about 45 dB, so if the MODEM did not include a duplexer, the transceiver system requirements would be impossible to meet with a reasonable power consumption. Active duplexers and balancing duplexers for implementation on-chip have been sought to replace off-chip SAW/BAW devices, and examples are shown in [33] and [34-37], respectively.

Fig. 2.3. Frequency-characteristics of a SAW-duplexer [32].

# 2.1.1 Circuit's for the Duplex Function

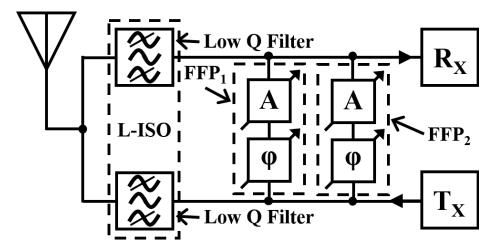

The block diagram of an active duplexer is shown in Fig. 2.4. The core of the active duplexer is the Low- ISOlation (L-ISO) device, which connects the antenna to the  $R_X$  input and  $T_X$  output. For the implementation of the L-ISO device, low Quality (Q)-factor tunable resonators are used, which are easier to implement and also provides a wider frequency coverage. The L-ISO device supplies enough isolation for the  $R_X$  input not to significantly load the  $T_X$  output, the main additional  $T_X$  load being due to the two Feed-Forward Paths (FFP) [FFP<sub>1</sub> and FFP<sub>2</sub>].

The function of FFP<sub>1</sub> and FFP<sub>2</sub> is to null-out the transfer from the  $T_X$  to the  $R_X$  port at both the  $R_X$  and  $T_X$  frequencies, which is done by adding a phase shifted (antiphase) and properly attenuated version of the  $T_X$  signal to the  $R_X$  port. The attenuation and phase of the FFPs should be adjusted so that the  $T_X$  signal fed forward will cancel the  $T_X$  signal leaking through the L-ISO at the center frequencies of the  $T_X$  and  $T_X$  signals. The individual FFP consist of a tunable Phase-Shifter ( $T_X$ ) and a tunable Attenuator (A). Control range, insertion loss and linearity are the key metrics for these building blocks. The most important metric, however, is the power

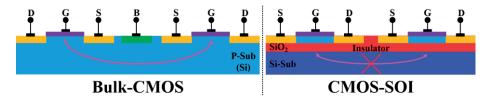

breakdown of the passive (inductors [L] and capacitors [C]) and active devices, and it is therefore common that circuits close to the antenna are implemented in either Silicon On Sapphire (SOS) or Silicon On Isolator (SOI) processes. The substrate can then be high-resistive, about 1000  $\Omega$ cm, compared with a bulk RF CMOS process of 10  $\Omega$ cm at most. This enables good passive components with high Q-values and Self Resonance Frequencies (SRF), but also the option of isolating the individual transistors from each other, which is very beneficial when designing stacked transistors in switches and power amplifiers (more stacked devices can be used than in bulk CMOS).

Fig. 2.4. The Block diagram of an active duplexer system.

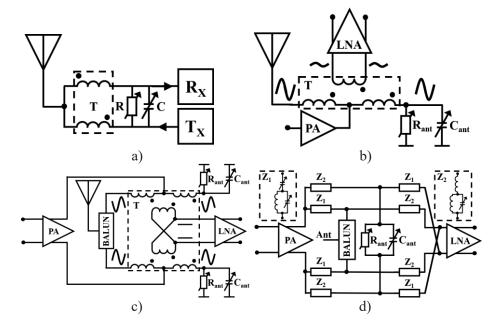

In Fig. 2.5 several versions of balancing duplexers are shown. Fig. 2.5a shows a balancing duplexer, which is very similar from a system point of view to the active duplexer in Fig. 2.4. The balancing duplexer consists of a Transformer (T) connected to the antenna,  $R_X$  input, and  $T_X$  output, which is fairly close to the L-ISO device, and the resistor R and the capacitor C is equivalent to a single FFP used in the active duplexer. The differences, on the other hand, is that the R and C in the balancing duplexer also helps with the impedance matching of the antenna, and the R and C path also has much larger current amplitudes, causing losses contributing to increased IL.

The balancing duplexer in Fig. 2.5b uses a single-ended "Dummy-Load". The main concept is to cancel the  $T_X$ -carrier and the  $T_X$ -noise at the  $R_X$  input by the means of balancing. If the dummy load, represented by  $R_{ant}$  and  $C_{ant}$  in the figure, is equal to the antenna impedance, then equal  $T_X$  currents (in both magnitude and phase) will flow from the PA connected to the center tap to each of the antenna and dummy load terminals. Since the two currents will then flow in opposite directions through equal transformer primary windings, no signal will be induced in the transformer

secondary, where the R<sub>X</sub> is connected. With a perfectly balanced structure, i.e. symmetric transformer, and perfectly matched dummy load to the antenna, the T<sub>X</sub> to R<sub>X</sub> isolation becomes infinite. It should be noted, however, that due to capacitive coupling between the transformer primary and secondary side, some T<sub>X</sub> signal will appear in Common Mode (CM) at the LNA input, requiring a certain CM Rejection Ratio (CMRR) of the LNA, but the required CM voltage/power range will be more important at full T<sub>X</sub> power. Further, the PA feeds equal current to antenna and dummy load, so fundamentally half the power goes to the antenna and the other half goes to the dummy load. This feature results in a loss of 3dB, in addition to losses of the transformer. Furthermore, the noise of the dummy load will equal that of the antenna at the  $R_X$  input, so the NF of the  $R_X$  is also at least 3dB. Finally, another bottleneck is associated with the tunable dummy load, whose tunable impedance has to be equal to the antenna impedance at all times over the frequency ranges of interest, or the balancing technique will fail. So with today's antennas and together with user interactions, the tunable dummy load must cover most of the possible antenna impedances and the tunable circuit elements in the load must also have high Q-values, good tunability, and very high voltage and current breakdown levels. The normal time-frame for user interaction is around 1 ms [23], so the tunable load does not have to be varied at a fast pace. To reduce the impedance tuning range of the dummy load an adaptive impedance tuner can be placed between the duplexer and antenna, but at the expense of increased IL.

Fig. 2.5. Balancing duplexers. (a) Narrow-band version [34]. (b) Wideband duplexer [35]. (c) Full balanced wideband duplexer [36]. (d) Hybrid-filter version with low loss [37].

In Fig 2.5c a fully balanced balancing duplexer is shown. The main difference from the balancing duplexer circuit in Fig. 2.5b is that the whole structure is differential, and thereby the common-mode voltage of the R<sub>X</sub> input due to capacitive coupling in the transformer is cancelled. The power handling capabilities are thereby greatly improved. However, all other bottlenecks associated with the structure in Fig. 2.5b still exist, and finally an extra BALanced to UNbalanced (BALUN) component is required between the duplexer and antenna.

The differential balancing duplexer in Fig. 2.5d includes filters, which eliminates most of the power dissipation in the dummy load (R<sub>ant</sub>, C<sub>ant</sub>). This structure uses two types of resonators/filters,  $Z_1$  and  $Z_2$ , the first resonator/filter  $Z_1$  being tuned to a low impedance at the T<sub>X</sub>-carrier frequency and a high impedance at the R<sub>X</sub>, whereas the resonator/filter Z<sub>2</sub> is tuned to a high impedance at the T<sub>X</sub>-carrier frequency and a low at the R<sub>X</sub>. The PA is connected differentially to the antenna port (BALUN) through Z<sub>1</sub> and to the dummy load through Z<sub>2</sub>. This means that T<sub>X</sub>carrier at the antenna is filtered/suppressed at the Rx-band frequency, and the Tx signal across R<sub>ant</sub> and C<sub>ant</sub> is filtered/suppressed at the T<sub>X</sub>-carrier frequency. A lower T<sub>X</sub> signal amplitude is then present at the dummy load, which reduces the power dissipated. The LNA is connected differentially to the dummy load through Z<sub>1</sub> and to the antenna through Z<sub>2</sub>, which means that the LNA is isolated from R<sub>ant</sub> and C<sub>ant</sub> at the R<sub>X</sub>-carrier frequency, and that there is a low loss path from the antenna to the input of the LNA, which means that the LNA can be designed with conventional input impedance. To further improve the isolation between the PA and LNA, the balancing concept is also used in this solution. The strong T<sub>X</sub>-carrier with noise in the R<sub>X</sub>-band is canceled at the LNA input if the dummy load impedance is equal to the antenna impedance, since the cross-coupled and non-cross-coupled signal paths from PA to LNA then become equal.

# 2.2 The Homodyne Receiver

# 2.2.1 Basic Noise Properties

The overall Noise Figure (NF) is considered the key figure of merit of the  $R_X$ , since for a certain signal strength, in absence of strong interference, this will set the Signal-to-Noise Ratio (SNR) level in the detector and thus the Bit Error Rate (BER) of the received data. A good starting point for understanding the noise figure (NF)/noise Factor (F) in an  $R_X$ , is provided by Friis' formula (2.1).

$$F_{Tot} = F_1 + \frac{F_2 - 1}{G_1} + \frac{F_3 - 1}{G_1 G_2} + \dots + \frac{F_n - 1}{G_1 G_2 \dots G_{n-1}} \approx F_1 + \frac{F_{rest} - 1}{G_1}$$

(2.1)

The equation describes the total noise factor of a cascade of circuit blocks, where  $F_1$ ,  $G_1$  are the noise factor and gain of the first block,  $F_2$ ,  $G_2$  of the second, etc. Let us now consider the  $R_X$  as a cascade of such blocks. If a circuit with high gain  $(G_1)$  is placed in the beginning of the  $R_X$ -chain, the equation tells us that the gain of this first block  $(G_1)$  will suppress the noise factor (F) of the circuit blocks further down the  $R_X$ -chain. The total noise factor will then be dominated by that of the first stage  $(F_1)$ , so by having the first stage gain high and noise factor low, the entire receiver will have high noise-performance. However, there is always another side to the story, and to place a high gain circuit in the beginning of the  $R_X$ -chain might cause linearity problems, due to large signals further down the  $R_X$ -chain. The noise figure (NF) is closely related to the noise factor (F), it is merely a conversion to dB units (2.2).

$$NF(dB) = 10 \cdot log_{10}(F) \tag{2.2}$$

# 2.2.2 Basic Linearity Properties

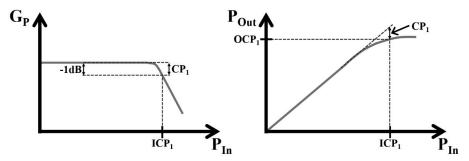

The other important performance of the  $R_X$  scenario is linearity. Lack of linearity, i.e. non-linearity, gives rise to distortion. Depending on the signals involved and type of non-linearity we can distinguish different types of distortion. One type of such distortion is called signal compression. In Fig. 2.6 signal compression and the measurement of Compression Point (CP) is illustrated. The CP is defined as the Input referred CP (ICP) or Output referred CP (OCP), these CP are also defined by the amount of signal compression in dB by the index, and as an example: a 1dB Input referred CP is referred to as  $ICP_1$ . The meaning of  $ICP_1$  is that this input power ( $P_{In}$ , Fig. 2.6) due to compression reduces the Power Gain ( $G_P$ ) by 1 dB compared to the small-signal value.

Fig. 2.6. Illustration defining 1dB compression point.

The decrease in  $G_P$  will consequently decrease the output power of the fundamental-signal at the circuit output. This is due to a non-linear transfer characteristic, where the gain/slope is lower at higher input signal levels. Fitting a polynomial to such a non-linearity gives odd-order coefficients with a negative sign. In general, however, there are also non-zero even-order coefficients. The polynomial transfer will depend on signal level and the coefficients give rise to Harmonic Distortion (HD). This distortion occur at new frequencies, at multiples of the frequencies of the signal components of the input signal.

The HD is typically not a major issue for the modern  $R_X$ , because the distortion occurs at frequencies outside the band of interest, but there may be cases where interferers occur at say a third of the received frequency so that third-order harmonics may disturb reception. A worse problem, however, is typically the so-called Inter-Modulation Distortion (IMD), which occurs when two or more signals with different frequencies enter a non-linearity, and the signals then mix with each other to generate distortion at new signal frequencies. The main difference between HD and IMD is that the new IMD tones are often/generally close to the original input signals, making them hard to suppress with filters.

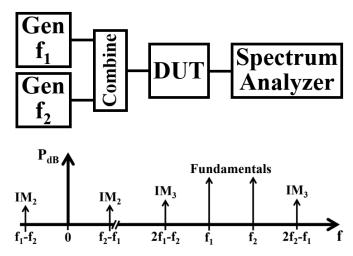

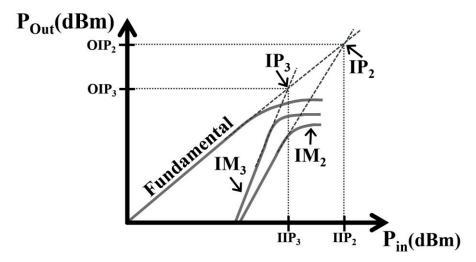

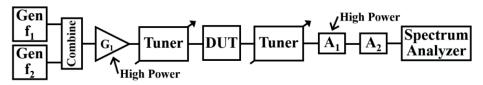

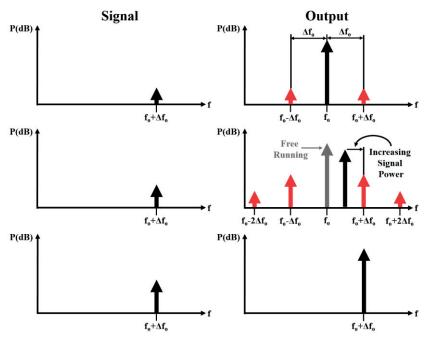

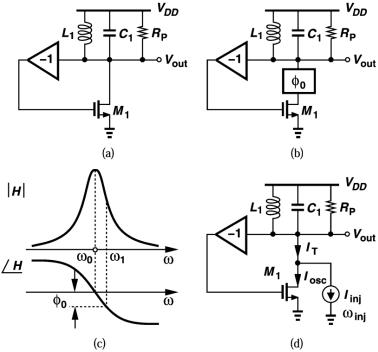

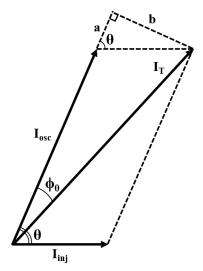

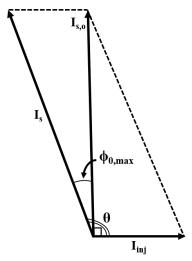

Fig. 2.7. The test bench and visual concept of a two-tone-test.

In order to benchmark the IMD performance, a two-tone-test can be performed either by measurement or by simulation, as shown in Fig. 2.7. The two tones have the same power/amplitude, but different frequencies  $f_1$  and  $f_2$ . IMD tones at different frequencies will then be generated due to the non-linearity of the Device Under Test (DUT). The most investigated IMD tones are the third-order ones at  $2f_2$ - $f_1$  and  $2f_1$ - $f_2$ , and the second-order one at  $f_2$ - $f_1$ . During the measurement/simulation the power of the two tones are increased in logarithmic/dB steps.

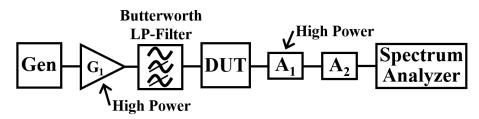

In this way the non-linear behavior of the DUT can be quantified and illustrated in a graphical plot as shown in Fig. 2.8. It is important that the diagram has a dB scale on both the horizontal and vertical axis. At low signal levels, well below compression, the slope of the fundamentals ( $f_1$  and  $f_2$ ) should then be close to one, the slope of the IM<sub>2</sub> close to two, and the slope of the IM<sub>3</sub> close to three, which can be seen in Fig. 2.8. The curves from the measurement/simulation, i.e. the fundamental, the IM<sub>2</sub>, and the IM<sub>3</sub>, are all linearly extrapolated from the curveportions where the slope is constant, and this extrapolation is also shown in Fig 2.8. Finally, the intersection of the extrapolated lines are found, the Intercept Point (IP) between the fundamental and the IM<sub>2</sub> is called the second-order IP (IP<sub>2</sub>), and the IP between the fundamental and the IM<sub>3</sub> is called the third-order IP (IP<sub>3</sub>). The IP can also be Input- and Output- referred, named the IIP<sub>x</sub> and OIP<sub>x</sub>, respectively, where x is the IMD order. By using these linearity benchmarks, system design and specifications can be well defined and connected to circuit design.

Fig. 2.8. Intercept point extraction from a two-tone measurement.

# 2.2.3 Cross-Modulation Distortion in the Homodyne R<sub>X</sub>

The cellular frequency spectrum of today is a cocktail of wireless standards, with both narrow and wideband operation. For these standards to all co-exist in the same spectrum, the mobile standard protocols and the frequency bands are managed/controlled by the 3G Partnership Project (3GPP) community [38]. Achieving co-existence still becomes increasingly difficult due to the ever more crowded spectrum. This makes the  $R_X$  design a real challenge, especially the circuits close to the antenna, which operate with the high frequency RF-carrier. These building blocks, the LNA and the down-conversion mixer, are also known as the  $R_X$  front-end. Fig. 2.9 illustrates the  $R_X$  front-end in a scenario with a strong blocker

signal and LO-leakage in co-existence with the received RF-carrier at the  $R_{\rm X}$  input. The linearity of the LNA is of foremost importance. If its compression point is not high enough, the strong blocker will cause gain compression of the LNA. If the blocker then has amplitude modulation, it will modulate the gain of the LNA. The LO-leakage at the output of the LNA will then be amplitude modulated. This mechanism is called cross modulation (XMD). Since in a homodyne  $R_{\rm X}$  the LO-leakage is located at the center of the channel to receive, if the LO-leakage is not low enough and the LNA compression point high enough, the XMD can result in a total corruption of the received signal. If severe, the information in the RF-carrier might be undetectable (BER=50%), but a smaller blocker will cause less BER degradation.

Fig. 2.9. Receiver cross-modulation scenario, due to LO-leakage and interferer.

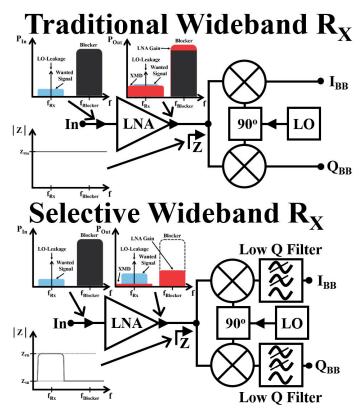

When using a wideband  $R_X$ -chain, the LNA should have a good wideband NF,  $G_P$ , ICP<sub>1</sub>, IIP<sub>3</sub>, and reverse-isolation. This is required since the received carrier is very small compared to the blocker and LO signal. However, to aid the LNAs linearity, down-conversion can be performed with a current mode passive mixer [12] or a voltage mode passive mixer with frequency-translation [18]. The mixer will then

have a low input impedance at the blocker-frequency, loading the LNA output reducing its blocker voltage level, reducing the risk for gain compression. The example in Fig. 2.9 uses a voltage mode passive mixer with frequency-translation. This will increase the ICP<sub>1</sub>, IIP<sub>3</sub>, and also the filtering of frequencies where the wanted  $R_X$  signal is not present. Finally, by improving the selectivity,  $G_P$  of the LNA can be increased, improving the in-band noise-performance. However, the noise-performance in presence of blockers is also dependent on  $R_X$ -LO phase-noise.

# 2.2.4 Reciprocal Mixing and Mixer Issues in the Homodyne R<sub>X</sub>

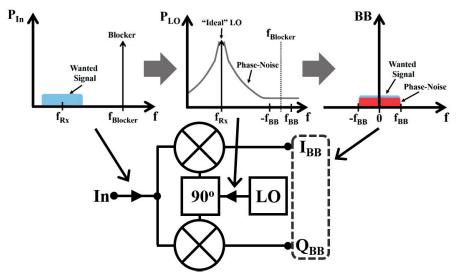

When a strong blocker is present at the RF-input of the down-conversion mixer, it causes the phase-noise of the  $LO_{Rx}$  at the blocker-frequency to be down-converted to DC. This phenomenon is called reciprocal mixing and is illustrated for a homodyne  $R_X$  in Fig. 2.10. It occurs when in the mixer the phase noise of the  $LO_{Rx}$  is multiplied with the strong blocker signal. The phase-noise within the frequency range  $f_{Blocker}$ - $f_{BB}$  to  $f_{Blocker}$ + $f_{BB}$  will after this reciprocal mixing fall on top of the received channel and degrade the noise-performance of the  $R_X$ . Although just illustrated for homodynes in Fig. 2.10, the problem of reciprocal mixing is present in all  $R_X$  architectures, i.e. also in heterodynes.

Fig. 2.10. Receiver reciprocal mixing caused by LO phase-noise and a large blocker.

LO-leakage and second order non-linearity (IIP<sub>2</sub>) are of particular importance in down-conversion mixers for homodyne receivers. For this reason differential mixer implementations are preferred. The LO-leakage and IIP<sub>2</sub> are then caused by circuit

mismatch, since a perfectly symmetric mixer driven by perfectly differential signals will not have any LO-leakage or even-order non-linearity. Some degree of mismatch is, however, inevitable. The resulting LO-leakage at the mixer input will then propagate through the LNA and end up at the LNA input. In a homodyne receiver the LO-leakage will be in the passband of the antenna filter, and will thus reach the antenna with low attenuation. High reverse isolation in the LNA is thus important. The LO-leakage at the antenna must be below spectral emission limits, and additional limits on the leakage level are often put by XMD and DC-offset. Finally, the IIP<sub>2</sub> of the mixer is of highest concern when the transceiver operates in FDD. The self-interference from the  $T_X$  is then the main issue. The duplexer in Fig. 2.3 is used to attenuate the T<sub>X</sub>-carrier at the R<sub>X</sub> input, but for economic reasons and to achieve small footprint the isolation of the duplexer is limited. The strongest interferer is then typically the own T<sub>X</sub> signal, which together with blockers must pass through the LNA and down-conversion mixer without generating significant distortion in the channel of interest. Due to mismatch, the differential mixer will produce unwanted IM<sub>2</sub> signals, which may end up within the Base-Band (BB) channel of the signal to receive, preventing or degrading the reception. For a single strong modulated interferer, like the own T<sub>X</sub> signal, a second-order non-linearity will produce distortion components with twice the original interferer bandwidth, centered at DC, like the homodyne baseband signal. The mixer IM<sub>2</sub> requirements in the homodyne R<sub>X</sub> are thus stringent.

# 2.3 The Homodyne $T_X$

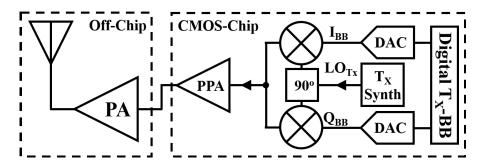

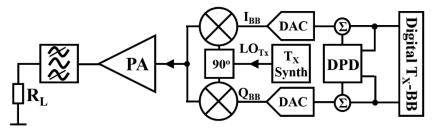

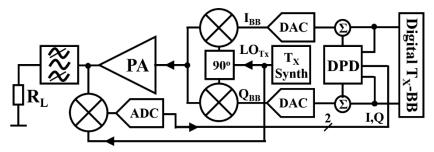

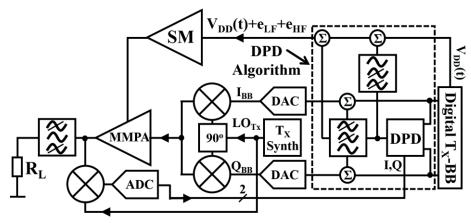

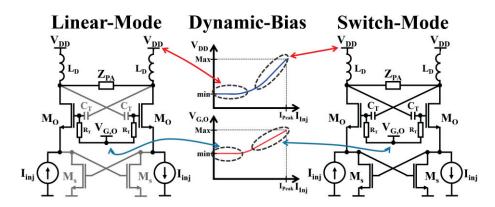

The traditional linear  $T_X$ -chain is shown in Fig. 2.11, consisting of the digital  $T_X$ -BB, Digital to Analog Converters (DACs), two mixers also known as a quadrature modulator, a Pre-PA (PPA), and a PA. In the digital  $T_X$ -BB, BB-signals with proper pulse-shapes and filtering are generated, the digital in-phase ( $I_{BB}$ ) and quadrature-phase ( $I_{BB}$ ) BB signals. The digital signals are converted to analog form in the DACs, including reconstruction filtering to remove high frequency aliases. The analog BB-signals are then frequency up-converted to RF in the quadrature modulator, by the use of the  $I_X$ -LO signal ( $I_{CT_X}$ ), which is generated by the  $I_X$ -

Fig. 2.11. Linear cellular homodyne transmitter.

Synthesizer (T<sub>X</sub>-Synth) in Fig. 2.11. Further, the generated modulated RF-carrier is amplified by the PPA, which often has a variable/programmable gain to adjust the transmit power level. The PA is typically off-chip, with associated parasitic impedances of the PA/PPA interface. The PA then requires sufficient input matching, and the PPA sufficient drive capability, but by implementing the PA in a semiconductor technology optimized for that purpose, higher performance can be reached than for an on-chip CMOS PA.

In an FDD-system, the  $T_X$  transmits a signal at the same time as the  $R_X$  receives, but at different frequencies ( $T_X$  at UL and  $R_X$  at DL frequency). By operating the  $T_X$  and  $R_X$  simultaneously, the requirements on both signal-chains become more stringent, foremost in terms of  $T_X$  out-of-band noise and  $R_X$  linearity The main sources of the  $T_X$  out-of-band noise is the  $T_X$  frequency synthesizer ( $T_X$ -Synth) and the frequency up-conversion mixers. The output signal ( $T_X$ -Synth) of the  $T_X$ -Synth has phase-noise (thermal-noise converted into time jitter inside the oscillator in  $T_X$ -Synth), which the mixers add to the signal in the frequency up-conversion and they also add their own thermal noise. The remainder of the  $T_X$ -chain amplifies the up-converted noise and adds its own noise as well, but the noise contribution of the PPA and PA is typically not dominant.

#### 2.3.1 Self-Interference from the $T_X$ in FDD

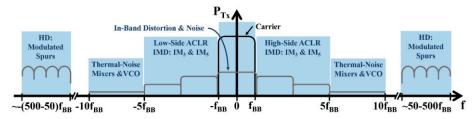

Fig. 2.12. Effects of the transmitter noise in the R<sub>X</sub>-band.

In Fig. 2.12,  $T_X$  out-of-band noise in the  $R_X$ -band and the effects on the  $R_X$  frontend are illustrated. As can be seen there is  $T_X$  out-of-band noise at the frequency of the wanted  $R_X$ -carrier, so leakage of this noise through the duplexer can increase the noise-floor at the  $R_X$  input and degrade the  $R_X$  SNR. To not de-sensitize the  $R_X$ -chain, the  $T_X$ -noise issues must then be addressed at the source of the problem, which is the circuits that generate the modulated  $T_X$ -carrier. The  $T_X$  output noise requirement is comparably straight-forward to determine, the noise-floor in the  $R_X$  is set by the thermal noise level and the noise figure  $(NF_{R_X})$  [39], the duplexer  $R_X$ -band suppression is 45 dB at minimum, and the  $T_X$  out-of-band output noise requirement can then be determined as (2.3). Note the degradation of the  $R_X$  noise figure  $(\Delta NF_{R_X})$  in (2.4), caused by the noise ratio  $(NR_{R_X})$ , a ratio between the noise-floor from the  $T_X$  at the LNA input  $(P_{Noise-TX-RX}^{f=RX})$  and the noise-floor without the  $T_X$  at the LNA input  $(P_{Noise-LNA}^{f=RX}(dBm), [-174 (dBm/Hz) + NF_{R_X}])$ . By calculating a degradation of the noise figure of approx. 1dB with (2.4), resulting in a finit noise-floor caused by the  $T_X$ , which must be approx. 6dB below the noise-floor of the  $R_X$ .

$$\begin{split} P_{Noise-Tx}^{f=Rx}\left(\frac{dBc}{Hz}\right) &= P_{Noise-LNA}^{f=Rx}(dBm) + NR_{R_X-1dB}(dB) + A_{Duplex}^{f=Rx} - P_{Tx}^{f=Tx} = \\ &= -174 + 3 + (-6) + A_{Duplex}^{f=Rx} - P_{Tx}^{f=Tx} = -177 + A_{Duplex}^{f=Rx} - P_{Tx}^{f=Tx} \end{split} \tag{2.3}$$

$$\Delta N F_{R_X}(dB) = 10 \cdot log_{10} \left( 1 + N R_{R_X} \right) = 10 \cdot log_{10} \left( 1 + \frac{P_{Noise-Tx-Rx}^{f=Rx}}{P_{Noise-LNA}^{f=Rx}} \right)$$

(2.4)

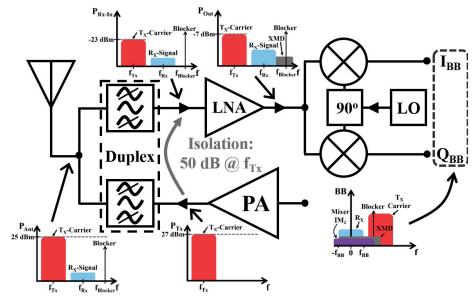

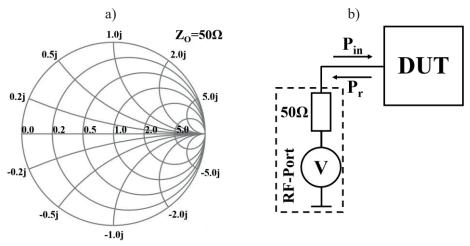

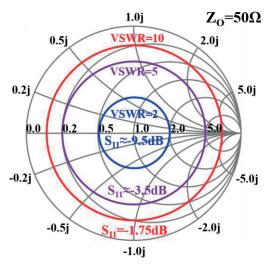

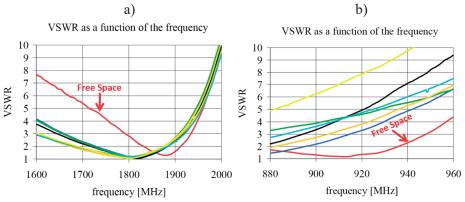

A more complex situation is self-interference together with an external blocker, as shown in Fig. 2.13. The worst case situation is when the UE is located far-away from the Base-Station (BS), and the received signal is small and close to the thermalnoise-floor. Far from the BS the UE will also generate a strong/high-power T<sub>X</sub>carrier. The T<sub>X</sub>-carrier is suppressed by about 50 dB in the duplexer before it reaches the R<sub>X</sub>-input. The blocker, however, is close in frequency to the received signal and is therefore not attenuated significantly before reaching the R<sub>X</sub>-input. The blocker is also of relatively strong/high-power, with respect to the small received signal, and the blocker and T<sub>X</sub>-carrier will cross-modulate to form XMD in the LNA. Further, all the signals are now present at the R<sub>X</sub>-mixer input, i.e. the wanted received signal, the T<sub>X</sub>-carrier, the blocker, and the XMD. Now as the mixer down-converts the weak wanted signal, it also generates IMD of the second-order (IMD<sub>2</sub>), caused mainly by the T<sub>X</sub>-carrier, which is stronger than the blocker. This scenario sets the linearity requirements of circuit blocks in the R<sub>X</sub> front-end, and that is the IIP<sub>3</sub> of the LNA and the IIP<sub>2</sub> of the down-conversion mixer. Finally, to ease the effects of the self-interference, cancelation paths like the FFP of the active duplexer (Fig. 2.4) can be used, as shown in [40]. This is possible because the  $T_X$ -carrier is generated locally in the UE and it is hence available for cancellation.

Fig. 2.13. Transceiver scenario with self-interference and strong blocker.

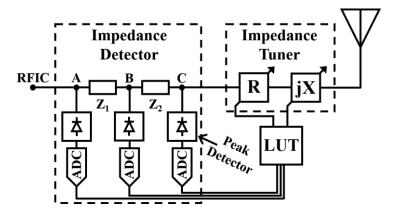

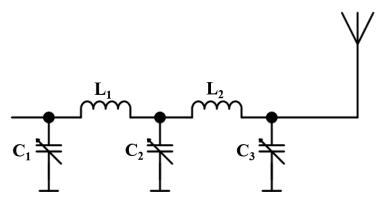

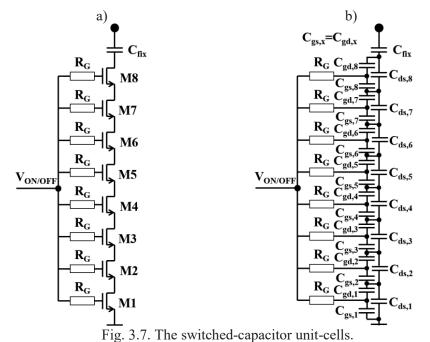

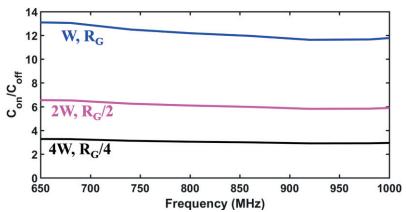

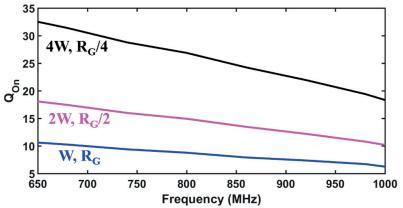

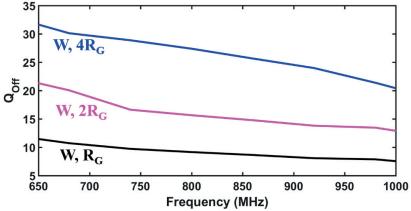

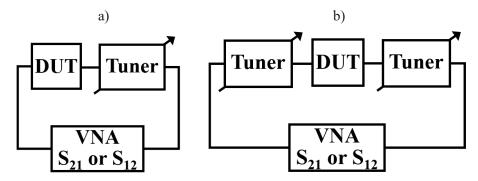

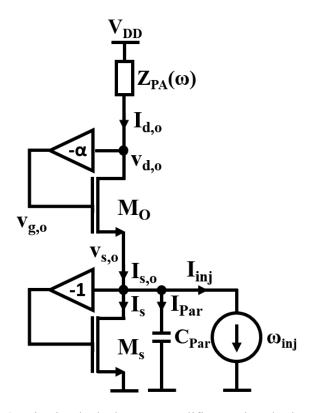

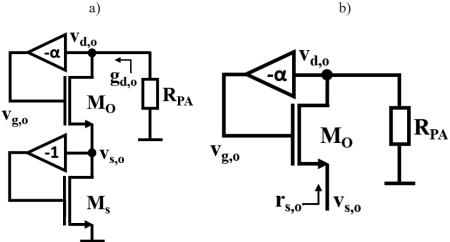

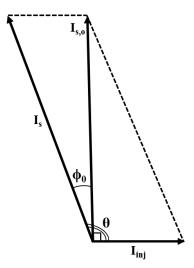

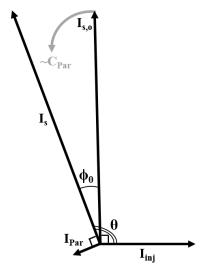

#### 2.3.2 T<sub>X</sub> Linearity and Noise