## On Lightweight Security for Constrained Environments

Sönnerup, Jonathan

2020

Document Version: Publisher's PDF, also known as Version of record

Link to publication

Citation for published version (APA): Sönnerup, J. (2020). On Lightweight Security for Constrained Environments. [Licentiate Thesis, Department of Electrical and Information Technology]. Lunds Universitet/Lunds Tekniska Högskola.

Total number of authors:

General rights

Unless other specific re-use rights are stated the following general rights apply:

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

• Users may download and print one copy of any publication from the public portal for the purpose of private study

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal

Read more about Creative commons licenses: https://creativecommons.org/licenses/

Take down policy

If you believe that this document breaches copyright please contact us providing details, and we will remove access to the work immediately and investigate your claim.

# On Lightweight Security for Constrained Environments

Jonathan Sönnerup

ISBN 978-91-7895-576-3 (printed) ISBN 978-91-7895-577-0 (electronic) Series of licentiate and doctoral theses No. 131 ISSN 1654-790X

Jonathan Sönnerup Department of Electrical and Information Technology Lund University Box 118 SE-221 00 Lund Sweden

Typeset using Lag. Printed in Sweden by Tryckeriet i E-huset, Lund, 2020.

© 2020 Jonathan Sönnerup Published articles have been reprinted with the permission from the respective copyright holder.

#### **Abstract**

The market of connected devices, IoT devices in particular, is hotter than ever. To-day, lightweight IoT devices are used in several sectors, such as smart cities, smart homes, healthcare, and the manufacturing industry. IoT solutions help increase productivity by predictive maintenance and resource management in the industry. Devices with voice interfaces are spreading rapidly in the home automation markets. Hospitals utilize these "smart" devices to monitor patients and present diagnostics data, aiding physicians in their work.

It is safe to say that we will be surrounded with more and more connected devices. This opens up to potential attacks, where adversaries may try to disrupt critical services or steal sensitive information. To combat this, data needs to be secured in different ways. This dissertation presents cryptographic algorithms and their performance in constrained environments.

First, a new lightweight cryptographic algorithm, Grain-128AEAD, is presented. Grain-128AEAD is a stream cipher designed to be implemented in hardware at a low cost while still being fast. The new design improves on earlier versions by making previous attacks more difficult.

Next, Grain-128AEAD is implemented in hardware using multiple optimization techniques to fit different criteria. Trade-offs between throughput, power, and area are evaluated to analyze the suitability for both constrained devices but also for server back-ends.

Finally, the overhead when adding confidentiality and authenticity for communication in an IoT device is evaluated. Here, modern lightweight protocols are utilized in multiple use-cases to give an overview of the overhead in terms of bytes, time, and energy.

# Acknowledgements

They say that when you decide to become a Ph.D. student, you do not chose your subject, you chose your supervisor. At least, that was the case for me. The first course I ever took in security was taught by Martin. His deep knowledge and enthusiasm in the subject led me to slowly change my major from hardware design to security. Multiple courses later along with a master's thesis, I am now writing my dissertation, with Martin as my main supervisor. I can not express anything other than my fullest gratitude for giving me this opportunity to pursue this degree. I would like to thank my assistant supervisors Paul Stankovski Wagner and Martin Höst for their guidance and interesting discussions.

I want to thank all my colleagues and friends in the Security and Crypto group at the EIT department for all the discussions during lunch and fika, and other random small-talk in the corridors. I would like to thank some people in particular. Erik Mårtensson was the first colleague with whom I had the pleasure of sharing office. However, that did not last long. After many, many hours of talking and discussing, not getting any work done, we eventually had to split, albeit only to an office next door. At one point in time, Erik was officially banned from my new office, due to overly excessive writing of mathematical formulae on my whiteboard. Even though we had our differences, I have always enjoyed his company during our travels around the world. We were the Jim and Dwight in the office. I want to thank Linus Karlsson for being a good role model. He is always up-to-date with the latest technology, knowledge that he happily shares with others. I have spent many hours in Linus's office discussing subjects from teaching to the internals of C compilers, but also hiding from Erik. Finally, I would like to thank Jing Yang for putting up with me during these years. I never gave her an easy time with all the jokes and pranks, for which I am not sorry. During our travels, she kept me and Erik in check, while still always being happy and kind.

I wish to thank the administrative and technical staff for all help during these years. Special thanks to Elisabeth Nordström who had to endure my rants about the travel expenses, Erik Jonsson for letting me degrade the security of the department by allowing me to open ports in the firewall on a daily basis, and Bertil Lindvall for helping me out when I needed equipment and for all joyful discussions ranging from farming to Breaking Bad.

Finally, I want to thank all my friends and family who have helped and supported me during my years as a Ph.D. student. In particular, I want to mention all the crazy projects with Christoffer, and the philosophical discussions with Umar. To my mom and dad for raising me to become who I am today, to my grandparents who always believed in me, and to my loving girlfriend, thank you for your love and understanding.

#### **Contribution Statement**

The following papers are included in this dissertation:

- Paper I Martin Hell, Thomas Johansson, Willi Meier, Jonathan Sönnerup, and Hirotaka Yoshida. "An AEAD Variant of the Grain Stream Cipher". In Codes, Cryptology and Information Security: Third International Conference, C2SI 2019, Rabat, Morocco. Springer Nature Switzerland AG. pp. 55-71.

- Paper II Jonathan Sönnerup, Martin Hell, Mattias Sönnerup, and Ripudaman Khattar. "Efficient Hardware Implementations of Grain-128AEAD". In Progress in Cryptology INDOCRYPT 2019 20th International Conference on Cryptology Proceedings, Hyderabad, India. Springer Gabler. pp. 495-513.

- Paper III Pegah Nikbakht Bideh, Jonathan Sönnerup, and Martin Hell. "Energy Consumption for Securing Lightweight IoT Protocols". This paper has been submitted but not yet published.

The responsibilities Jonathan Sönnerup had in each paper are summarized in the table below:

| Paper | Writing | Concepts | Implementation | Evaluation |

|-------|---------|----------|----------------|------------|

| I     | partial | partial  | YES            | -          |

| II    | YES     | YES      | yes            | YES        |

| III   | yes     | YES      | YES            | yes        |

Capital letters indicate roles where Jonathan Sönnerup had the primary responsibility.

In Paper I, Jonathan created a C implementation of the design, both a reference implementation and an optimized version. He contributed with implementation ideas and approaches, and parts of the hardware implementation, and wrote the corresponding section in the paper.

In Paper II, Jonathan had the primary responsibility for writing the paper. He contributed with optimization ideas and approaches, and parts of the implementation. Together with the other authors, he analyzed and evaluated the results.

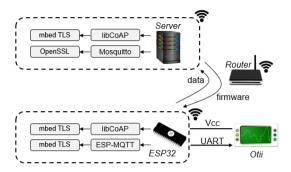

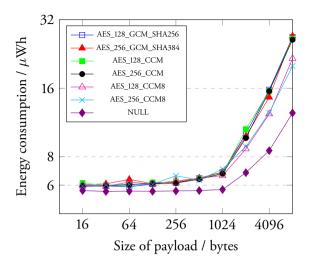

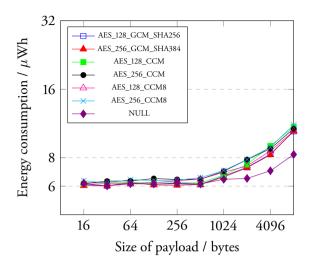

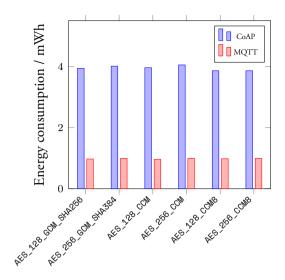

In Paper III, Jonathan's primary responsibility was the implementation of the system and test suite and the embedded system, i.e., the client-side. Together with the other authors, he defined the overall system along with evaluating the results, where he was responsible for MQTT.

A further description of the papers' contributions to the research field is presented in Section 3.1.

#### Other Contributions

The following peer-reviewed publications have also been published during my Ph.D. studies, but are not included in this dissertation.

- Martin Höst, Jonathan Sönnerup, Martin Hell, and Thomas Olsson. "Industrial Practices in Security Vulnerability Management for IoT Systems an Interview Study". In *International Conference on Software Engineering Research and Practice, SERP'18, Las Vegas, United States*, pp. 61–67.

- Jonathan Sönnerup and Martin Hell. "Evaluating Security of Software Through Vulnerability Metrics". In *International Conference on Security and Management, SAM'18, Las Vegas, United States*, pp. 79–85.

- Alexander Cobleigh, Martin Hell, Linus Karlsson, Oscar Reimer, Jonathan Sönnerup, and Daniel Wisenhoff. "Identifying, Prioritizing and Evaluating Vulnerabilities in Third Party Code". In 2018 IEEE 22nd International Enterprise Distributed Object Computing Workshop (EDOCW), Stockholm, Sweden. pp. 208–211, IEEE.

- Sara Gunnarsson, Peter Larsson, Sara Månsson, Erik Mårtensson, Jonathan Sönnerup. "Engaging Students using GitHub as a Learning Management System". In Lunds universitets pedagogiska utvecklingskonferens 2017, Lund, Sweden. pp. 63–70.

# **Contents**

| Ab | act                                                        | iii                        |

|----|------------------------------------------------------------|----------------------------|

| Ac | owledgements                                               | v                          |

| Co | ribution Statement                                         | vi                         |

| Co | ents                                                       | ix                         |

| 1  | ntroduction  1 Dissertation Outline                        | 1 2                        |

| 2  | ackground  1 Constrained Devices and Lightweight Protocols | 3<br>3<br>12<br>23         |

| 3  | Contributions and Conclusions  1 Contributions             | 31<br>31<br>33             |

| Re | ences                                                      | 35                         |

| In | ded Publications                                           | 43                         |

| I  | n AEAD Variant of the Grain Stream Cipher  Introduction    | 45<br>45<br>47<br>50<br>53 |

x CONTENTS

|     | 5 Implementation                        |               |          | 56  |

|-----|-----------------------------------------|---------------|----------|-----|

|     | 6 Conclusions                           |               |          | 58  |

|     | References                              |               |          | 58  |

|     | Appendix                                |               |          | 63  |

| II  | Efficient Hardware Implementations of   | Grain-128AE   | AD       | 65  |

|     | 1 Introduction                          |               |          | 65  |

|     | 2 Grain-128AEAD                         |               |          | 67  |

|     | 3 A Straightforward Approach            |               |          | 70  |

|     | 4 RTL Level Optimizations               |               |          | 71  |

|     | 5 Synthesis Level Optimization          |               |          | 76  |

|     | 6 Synthesis Results                     |               |          | 77  |

|     | 7 Conclusions                           |               |          | 82  |

|     | References                              |               |          | 83  |

| III | II Energy Consumption for Securing Ligh | tweight IoT P | rotocols | 85  |

|     | 1 Introduction                          |               |          | 86  |

|     | 2 Related Work                          |               |          | 87  |

|     | 3 CoAP and MQTT                         |               |          | 88  |

|     | 4 Experimental setup                    |               |          | 89  |

|     | 5 Methodology and Use Case              |               |          | 91  |

|     | 6 Results and Discussion                |               |          | 93  |

|     | 7 Conclusions                           |               |          | 101 |

|     | References                              |               |          | 102 |

# Introduction

Ever considered that your smart-home could kill you? While that may be an exaggeration, connecting random things to the Internet might pose a significant problem.

Today, more and more "smart" devices are being manufactured and sold, both in industrial markets and to regular households. Heating, Ventilation, and Air Conditioning (HVAC) is one example of industrial entities transformed by the latest IoT technologies. Adding connectivity allows for a vast flow of information, both to and from the HVAC devices, such as weather feeds, sensor data. This may be used to perform data analysis on a larger scale, which may help reducing power consumption and increase efficiency. Connectivity also allows for remote management of the complete system.

Another example is self-driving cars. Connecting cars, or general automotive vehicles, to the Internet allows for distribution of software updates in real-time. Manufacturers may also analyze the performance and usage of the vehicles and adjust properties accordingly. Connectivity would aid the self-driving system by gathering relevant data of its surroundings, preventing potential accidents. It is not difficult to see that even though the benefits are many, by allowing remote communication, an attacker could send bogus data or also gain access to the control mechanisms in the car, allowing the attacker to cause fatal incidents.

A less obvious example of abusing an IoT device might be a temperature system, including sensors and heaters, in a villa controllable from a smartphone app. An attacker could use the current temperature information to deduct if the house is empty, to break in. If the house is equipped with an alarm system, this too may be exploited.

What, then, needs to be done to protect companies and households from having their IoT devices exploited? There is little surprise that the answer to this question is cybersecurity. However, there is no single solution to all problems. The infrastructure and computational resources of self-driving cars are entirely different from temperature sensors. For the smallest of devices, there are strict requirements on speed, physical area, and power consumption. Being that most

2 Introduction

smaller devices run on batteries, they can not afford any high-power solutions. Instead, one must design cryptographic primitives suitable in a constrained environment, without weakening the security. The design aspect ranges from the physical hardware design and implementation of circuits to the software that utilizes the hardware components.

#### 1.1 Dissertation Outline

This dissertation is organized as follows. The following chapter, Chapter 2, introduces the topics related to the research conducted in this dissertation.

Section 2.1 presents the possibilities and limitations of constrained devices and their role in modern society. Here, we also present some current lightweight protocols adapted to keep the overhead and power consumption at a minimum. The section introduces the concepts used in Paper III. In Section 2.2, the area of cryptography is presented with a focus on symmetric ciphers, especially stream ciphers. The area of cryptography is the basis of all papers in this dissertation. Finally, in Section 2.3, the reader is introduced to the process of designing digital circuits, i.e., hardware design, and how to implement digital logic running at high speed and consuming low power. This section is closely related to Paper II, where a stream cipher is implemented in hardware.

Chapter 3 summarizes the contributions of the research, followed by conclusions.

Finally, the second part of this dissertation contains the publications.

Today, products such as watches, clothes<sup>1</sup>, smart grids, and industrial sensor networks are being connected to the Internet, aggregating and exchanging data. These products are commonly referred to as the Internet of Things, or IoT. Some of these products are made up of small and cheap embedded devices, such as microcontrollers (MCUs). Being connected to the Internet poses a risk for the devices, due to the exposure to attackers. To avoid exploitation and data leakage, one needs to implement security measures.

Such small devices usually lack the resources to perform heavy computation. Thus, to prevent or mitigate attacks, careful design and implementation is a must, ranging from the design process from the hardware chip to the selection of cryptographic algorithms and software implementation.

In this chapter, we introduce the general concepts behind constrained devices, cryptography, and hardware design.

# 2.1 Constrained Devices and Lightweight Protocols

Following IETF, a device is said to be constrained if it consists of a limited CPU, small memory such as ROM and RAM, low bandwidth, low energy consumption, or a combination of these [BEK14]. IETF also specifies different classes of constrained devices, ranging from class 0, including small sensors that do not directly communicate with the Internet, up to class 2, including devices that can run standard protocols but would benefit from running lightweight protocols due to energy and bandwidth.

Generally speaking, a constrained device can not, or should not, run the *usual* protocols such as TCP/IP, TLS, HTTP, and so on. Instead, many lightweight protocols have been developed to be used in a constrained device, described in Section 2.1.3.

A microcontroller unit (MCU) is a single integrated circuit (IC), comprising of a CPU along with memory and peripherals for I/O. Microcontrollers range from

<sup>1</sup>https://atap.google.com/jacquard/

the smallest architectures such as Atmel AVR 8-bit products, e.g., ATmega8A, to Espressif 32-bit microcontrollers with integrated WiFi and support for Over-the-Air (OTA) updates, e.g., ESP32. An MCU typically consists of the following:

- A central processing unit, CPU.

- Flash memory, for storing program instructions and non-volatile data.

- Volatile memory, RAM, for temporary data storage during run-time.

- General purpose input/output, GPIO, configurable to act as either an input, when reading, e.g., sensor data, or an output when controlling, e.g., LEDs or motors.

- Serial communication protocols, such as UART, I<sup>2</sup>C, and SPI.

- Timers and PWM generators.

- Analog-to-Digital converters, ADCs.

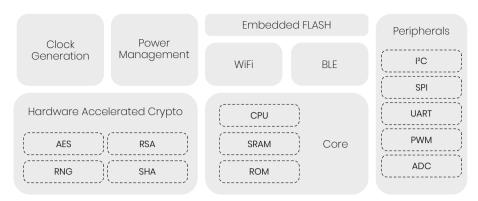

Some microcontrollers also include crypto modules, i.e., hardware-accelerated cryptographic functions such as RSA, AES, ECC, RNG, and hash functions. Having these algorithms run in hardware instead of software saves energy and increases throughput. The general architecture of a microcontroller is depicted in Figure 2.1. Some common microcontrollers, along with an excerpt of their specifications, are shown in Table 2.1. As seen in the table, the devices are quite constrained in terms of speed and memory, with the ARM Cortex-M0+ being the most lightweight processor.

**Table 2.1:** Comparison of popular IoT development boards. All have an operating voltage of 3.3 V.

| Board              | CPU              | Arch   | Clock   | RAM     | Connectivity |

|--------------------|------------------|--------|---------|---------|--------------|

| Particle<br>Photon | ARM Cortex M3    | 32-bit | 120 MHz | 128 KiB | WiFi         |

| Particle<br>Argon  | ARM Cortex-M4F   | 32-bit | 64 MHz  | 256 KiB | WiFi + BLE   |

| ESP32              | Tensilica Xtensa | 32-bit | 240 MHz | 520 KiB | WiFi + BLE   |

| Arduino<br>MKR1000 | ARM Cortex-M0+   | 32-bit | 48 MHz  | 32 KiB  | WiFi         |

It is not only microcontrollers who benefit from hardware acceleration. In 2010, Intel released the first set of CPUs with an instruction set for running AES in hardware, known as AES-NI [Gue06]. AES is such a widespread and common algorithm that the increase in speed and reduction in power consumption outweighs the hardware cost [CLG13].

Figure 2.1: A general architecture of a microcontroller.

Today, most microcontrollers are programmed using C/C++, but even Python and Javascript may be used in some cases. However, due to the variety of microcontrollers, the standard implementations of programming languages might not be feasible. Many flavors of standard languages, such as Embedded C [Int08], nesC [Gay+03], and MicroPython<sup>2</sup> have been implemented to better fit embedded systems.

#### 2.1.1 Low-Power Solutions

Since many IoT devices run on batteries, the circuits employ functionality to help reduce power consumption. A common solution is to use a set of sleep modes. A sleep mode can be thought of as a set of active components used in the system. The deeper the sleep, the fewer components are active, lowering the used power.

The technique for powering down certain parts of a circuit is known as clock gating. Clock gating implies that the clock signal is *gated*, i.e., activated or deactivated for some time. By disabling the clock pulses, the digital logic no longer switches states. It is the switching activity that consumes dynamic power.

An example of sleep mode levels is described next, assuming a microcontroller with communication capabilities, like in the architectural overview in Figure 2.1. Note that we here express power consumption in terms of current, which is common practice. While it is technically wrong to do so, the power consumption for a microcontroller is proportional to the current, since the voltage is kept constant.

Active mode Here, the device operates normally with all components in the active state. Active mode is the state where the device consumes the most power. It is not unusual for the power consumption to be a few 100 mA. For example, the ESP32 with the communication blocks active consumes around 30 mA

<sup>&</sup>lt;sup>2</sup>https://docs.micropython.org/en/latest/

in idle state, and around 100 mA during transmission. A Raspberry Pi Zero consumes roughly 100 mA while being 600 mA for Raspberry Pi 4<sup>3</sup>.

Sleep mode Communication is one of the most expensive operations in an embedded system. Hence, this is the first part to power down in sleep mode. The CPU is also paused in the sense that it does not execute any instructions. The high-frequency clock generator is active in order to quickly resume regular operation once we exit sleep mode via an interrupt, for example. Peripherals may be active, along with the SRAM, to allow computation and storage via DMA without the need for CPU intervention. A typical value for power consumption in this state is a few mA. An ESP32 in sleep mode consumes ca 1 mA<sup>4</sup>.

Deep sleep This is as close to the system being completely shut down as we can get, without actually shutting down the system. The high-frequency clock is powered off, and only critical parts are active, such as the real-time clock and watchdog timer. The content previously stored in CPU registers and RAM is also erased. If some data needs to be saved, one can utilize the non-volatile flash memory. The power consumption in this state may be as low as a few  $\mu A$ . For example, the ATmega328P uses around 1.5  $\mu A$  at 3 V [Atm].

#### 2.1.2 Over-the-Air Updates

As software is being continuously developed with new features, bug fixes, or security patches, the already deployed systems need to be updated. In systems without communication capabilities, this is usually done by manually flashing a new firmware via UART, SPI, JTAG, or similar, requiring physical access.

Many IoT devices are deployed in areas that are physically cumbersome to access [Bar+08]. Other devices are located in home environments, measuring humidity, temperatures, power consumption, and so on. A home environment may make it hard to update the devices since ordinary residents do not possess the tools nor skills to perform a system update. In such cases, *Over-the-Air* updates may assist.

Over-the-air, or OTA, refers to the wireless medium used to distribute content, such as firmware. With OTA, there is no need for physical presence while performing an update, which solves many of the above problems. However, implementing OTA support is not a trivial task, not only from an implementation point of view but also from a management point of view. Some potential issues are given next.

You need to handle devices that lose connection and which devices have and have not already been updated.

<sup>&</sup>lt;sup>3</sup>https://www.raspberrypi.org/documentation/hardware/raspberrypi/power/

<sup>&</sup>lt;sup>4</sup>https://lastminuteengineers.com/esp32-sleep-modes-power-consumption/

- Installing a new firmware may cause the system to hang or break.

- There needs to be sufficient space for temporarily storing the latest firmware before it can be applied.

Next, let us look at some known architectures for OTA.

Modern Android implements so-called A/B system updates<sup>5</sup>. Upon update, the new firmware is downloaded and stored in /data. After the full firmware is retrieved, it is installed in a partition different from the currently running firmware, called A and B partitions. The installation process does not interrupt the user as the current firmware is running until the user reboots the device. Upon booting, the new firmware is applied. If it fails, the device will load the previous firmware, known as roll-back. Since Android 8.0, it is now possible to use *streaming* A/B updates. This means that the firmware is written directly to partition B without having to store it in /data temporarily. To reduce the size of the new firmware, one may use compression algorithms such as Brotli<sup>6</sup>.

IETF has proposed an update-architecture for the IoT [Mor+19]. The document highlights that the update process must ensure that the firmware has integrity protection to prevent modification or injection attacks. The update process must be able to provide confidentiality protection since the first step of an attacker is usually to obtain the firmware and reverse engineer it. Other requirements include:

- The firmware distribution mechanism must support a variety of protocols, such as UART, BLE, HTTP, and CoAP. Supporting multiple protocols adds redundancy and compatibility.

- The device should not accept old firmware, preventing an attacker from exploiting a previous vulnerability. This attack is known as a roll-back attack.

- Updating the bootloader should be kept at a minimum since failure to update the bootloader properly may ultimately break the system.

- Updates can be client-initiated via polling. Polling only consumes energy

upon checking for new firmware, but the time difference between the release

of new firmware and the client checking for it may be significant, causing a

window of risk (or opportunity). A server-initiated update method requires

the clients to have a persistent connection to the server, but the client may

receive the firmware as soon as it is published.

All in all, this puts high demands on small devices, requiring careful and efficient implementation. Luckily, there exists a plethora of both circuits and libraries to handle the security requirements.

<sup>&</sup>lt;sup>5</sup>https://source.android.com/devices/tech/ota

<sup>&</sup>lt;sup>6</sup>https://github.com/google/brotli

#### 2.1.3 Lightweight Protocols

As described earlier, the old and well-established protocols like HTTP, TCP, and so on are not always applicable in a constrained setting. Imagine that we are to send 100 kB of data from a mobile phone to a friend in a secure way. We may use TCP/IP along with TLS to achieve this. We make the following assumptions:

- We are using IPv4.

- The maximum transmission unit, MTU, is 1500 bytes.

- The maximum segment size, MSS, of a TCP packet is 1460. That is, we are not using any options in neither TCP nor IP.

This means that we need to send  $\left\lceil \frac{100k}{1460} \right\rceil = 69$  packets. Using the numbers in [Mat20] means that the overhead is  $69 \cdot 40 = 2760$  bytes for TCP and IP itself, along with  $69 \cdot 30 = 2070$  bytes for TLS packet overhead, and around 5 kB for the TLS handshake. All in all, the total overhead is circa 10 kB bytes, which equals  $\frac{10k}{100k} = 10\%$  overhead, which is not too bad. Now, imagine that we have an IoT device transmitting 100 bytes to a gateway. The data fits into a single packet, and the overhead is around 5 kB, using the same setup as before. However, this equals a  $\frac{5k}{100} = 5000\%$  overhead.

A *lightweight* protocol tries to combat the issues of large overheads and computational costs by using less complex designs and small memory footprints. Lower complexity usually results in using fixed header lengths for ease of parsing and reducing the number of options that are part of the standard.

Next, we briefly present some of the most common lightweight protocols.

#### IEEE 802.15.4

The IEEE 802.15.4 standard defines low-rate wireless personal area networks, LR-WPANs [IEE16]. The standard specifies the physical layer along with the media access control (MAC) layer of the OSI model. It supports data rates up to 250 kb/s. The standard specifies the 2.4 GHz band as one of the allowed frequency bands for worldwide use.

#### **6LoWPAN**

6LoWPAN, short for IPv6 over Low-Power Wireless Personal Area Network, is a protocol for devices conforming to IEEE 802.15.4 [KMS07]. A LoWPAN may be characterized by the following:

- Devices are transmitting small-sized packets.

- Low bandwidth communication.

- The devices are battery operated.

Devices may be put into sleep mode for longer periods.

6LoWPAN utilizes IPv6 as the network protocol due to already existing infrastructure. IP-based networks have been used and analyzed for a long time; hence management and diagnostics for these networks are well known. The connectivity to other IP-based devices is straightforward since there is no need for gateways or proxies.

#### ZigBee

ZigBee is a low-power wireless mesh network protocol based on IEEE 802.15.4, adding networking functionality, such as network formation and routing [Zig15]. ZigBee also defines a framework for user applications. ZigBee operates typically at 2.4 GHz, making it compatible in many markets.

ZigBee has been used in many commercial products<sup>7</sup> such as Philips Hue<sup>8</sup>, IKEA's Trådfri products<sup>9</sup>, and HVAC systems<sup>10</sup>. The most interesting product, in the author's opinion, is the Hue Tap switch from Philips, using *only* the kinetic energy from physically pushing the buttons. That is, there is no battery involved.

A ZigBee device acts as one of three types within the network:

Coordinator The coordinator node initializes the network by configuring the frequency and network ID. The coordinator becomes the parent of all nodes connecting to the network through it.

**Router** The routers handle the packet routing in the network. These nodes are not required, but it is common to use them.

End Device An end device only sends and receives messages; hence it does not perform any other actions in the network. Only end devices may be put into sleep mode. The parent node then buffers messages until the device is awake again.

Even though IEEE 802.15.4 specifies encryption at the MAC layer, it lacks key management schemes and how to handle authentication. ZigBee implements these schemes at higher layers. ZigBee uses AES-128 for encryption and specifies three methods for key distribution: pre-installation, placing keys on the device before deployment; transport, sending keys over the network to the devices; and establishment, where keys are negotiated over the network.

ZigBee specifies two security models, described next.

<sup>&</sup>lt;sup>7</sup>https://zigbeealliance.org/product\_type/certified\_product

<sup>8</sup>https://www2.meethue.com

<sup>9</sup>https://www.ikea.com/us/en/cat/smart-lighting-36812/

$<sup>^{10}</sup>$ https://www.airconditioning-systems.com/zigbee.html

Centralized Security Networks In this model, there is a security component called the Trust Center responsible for authenticating devices joining the network. The Trust Center also generates network keys, which is periodically changed.

**Distributed Security Networks** This model is simpler but also less secure. There is no Trust Center, but only routers and end devices.

Even though the security in ZigBee is considered to be strong, there are potential weaknesses due to the actual implementation, but also due to many devices not being tamper resistant [Zill6]. Due to most ZigBee devices are constrained and battery-powered, they are susceptible to DoS and battery depletion attacks [Cao+16].

#### CoAP

The Constrained Application Protocol, or CoAP [SHB14], is a client-server based web transfer protocol designed to be used within constrained devices and networks. CoAP, similar to HTTP, is based on the REST model, where resources are available under a URL. Clients may then access the resources using methods like GET, POST, PUT, and DELETE. CoAP may be seen as a lightweight version of HTTP.

CoAP has the following features:

- Small header overhead

- Low parsing complexity

- Allows proxy and chaining

- Stateless HTTP binding, which allows access to CoAP resources via HTTP and vice versa

- Compatible with DTLS

The message header is of fixed length and only requires 4 bytes, using no options. CoAP runs over UDP due to UDP being more lightweight than TCP. Due to UDP not having mechanisms for reliable transmission, CoAP implements support for reliable messaging by marking a message as confirmable. A message marked as confirmable is retransmitted, using timeouts and exponential back-off, until the receiver has sent an acknowledgment message. For unreliable transmission, a message can be marked as non-confirmable instead.

Since CoAP runs over UDP, it is common to use DTLS for securing the communication channel. Another method for securing communication is to use OS-CORE [Sel+19]. Since CoAP is mappable to HTTP via proxies, which terminates the (D)TLS connection, the proxy servers may access and manipulate the data. OSCORE provides CoAP with an end-to-end encrypted channel. OSCORE has

a smaller overhead compared to DTLS, making it faster in some settings, as shown in [Gün+20].

CoAP is one of the protocols analyzed in Paper III with and without DTLS using different encryption schemes.

#### **MQTT**

The Message Queuing Telemetry Transport protocol, or MQTT [Ban+19], is a lightweight publish-subscribe protocol used to transport messages between devices. An MQTT network consists of two entity types: a message broker and clients. The broker acts as a router, receiving messages from clients, and routing the messages to the appropriate destination. A client is a device running an MQTT application, communicating with the broker to send and receive messages. MQTT usually typically runs over TCP/IP but supports other protocols as well.

Clients subscribe to specific topics. When a client sends a message with a specific topic, the broker distributes this to all clients subscribing to this topic. A client may both be a publisher and a subscriber.

An MQTT message packet consists of a header and payload, with a fixed-size header of 2 bytes. The length variable is a single byte, allowing for message sizes up to 127 bytes. For longer messages, MQTT supports a variable-length header using an encoding scheme. The largest supported message is approximately 256 MiB. The four first bits (MSB) in the header determines the message type, such as connect, publish, subscribe, and disconnect.

The security in MQTT is left to the implementer, but it is common to use TLS, allowing for password-based and certificate-based authentication. Management of keys and certificates for heterogeneous networks becomes cumbersome as the networks grow. The scalability issues have led to research on other approaches, such as using Attribute-Based Encryption (ABE) over elliptic curves, supporting broadcast encryption, as done in SMQTT [Sin+15].

MQTT-SN [ST13] is a continuation of the MQTT protocol, targeting small sensor nodes with minimal resources. MQTT-SN runs over UDP, which reduces the size of the messages. There is an MQTT-SN gateway translating between MQTT and MQTT-SN. Just like for MQTT, there have been several proposed security architectures for MQTT-SN, such as SMQTT-SN [Sin+15].

MQTT is the other protocol, along with CoAP, analyzed in Paper III.

# 2.2 Cryptography

The word cryptography originates from the Greek words *kryptós* "secret", and *graphein* "to write". In other words, *secret writing*.

The desire for hiding information has been around for a very long time - the oldest known use of cryptography dates back to 1500 B.C. [Kah96], used for hiding the formula of making pottery glaze. Monoalphabetic substitution ciphers were later invented, such as the Atbash cipher and the Caesar cipher. The ciphers use a fixed bijective mapping from an alphabet to itself, e.g., the letter "A" is always replaced with the letter "Q" and so on. Polyalphabetic ciphers build upon monoalphabetic, with the mapping being changed during the encryption or decryption process. For example, for the first five letters, "A" maps to "Q", while for the next five, we map "A" to "M", and so on.

In the modern age, there are two basic cryptographic primitives when it comes to encryption - asymmetric, known as public-key cryptography, and symmetric, known as symmetric-key cryptography.

#### 2.2.1 Asymmetric Ciphers

In the asymmetric case, we have two different, mathematically linked, keys: a public key for encryption and a private key for decryption. It is hard to find the private key given the public key, whereas it is easy to get the public key if we have access to the private one. Next, we describe some commonly used asymmetric algorithms.

#### **RSA**

Dating back to 1977, RSA [RSA78] is one of the first published public-key algorithms and is still today widely used in communication protocols. The security of RSA is known as the RSA problem. The RSA problem is related to the integer factorization problem, which is believed to be difficult. At the time of writing, no published algorithm solves the integer factorization problem in polynomial time.

**Definition** (Integer Factorization Problem). Given a positive integer n, find the prime factorization of n, such that  $n = p_1^{e_1} p_2^{e_2} \cdots p_k^{e_k}$ ,  $p_i$  being pairwise distinct primes with  $e_i \geq 1$ .

RSA consists of two parts: a public key consisting of the pair  $\langle e,n\rangle$ , and a private key d. In practice, more values are stored along with the private key, to speed up computations. The n parameter is calculated by multiplying a set of prime numbers, usually two, denoted p and q. The public exponent e is generated such that it is co-prime to  $\phi(n)$ , usually  $2^{16}+1$ , with  $\phi$  being Euler's totient function. This is sometimes replaced by Carmichael's totient function,  $\lambda(n)$ , for efficiency. Keeping e small allows for more efficient encryption, due to the reduced

amount of computation carried out. The private key is calculated as the inverse of  $e \mod \phi(n)$ . To summarize,

$$\begin{split} n &= p \cdot q, \\ e &= \{e \mid 2 < e < \phi(n), \ \gcd(e, \phi(n)) = 1\}, \\ d &\equiv e^{-1} \mod \phi(n). \end{split}$$

The encryption and decryption process, of a message m and ciphertext c, is then given by

$$c = m^e \mod n,$$

$m = c^d \mod n.$

The security relates to the size of n. NIST recommends using at least 2048 bits in today's systems, with an estimated security level of 112 bits [Bar+19]. Plain RSA is un-padded and deterministic, making it vulnerable to several attacks. Schemes like RSA-OAEP [Mor+16] have been proposed, which adds padding and randomness. RSA is not only used for encryption, but also for providing digital signatures. In this case, the private key, d, is used for signing, and the public exponent, e, is used for verification. Due to the usually small value of e, encryption and signature verification is fast, whereas decryption and signature creation is more expensive.

The introduction of quantum computers and Shor's algorithm [Sho94] poses a serious problem against algorithms like RSA, since it would be possible to break RSA fairly efficiently [GE19]. Post-quantum resistant versions of RSA have been proposed, such as the one in [Ber+17], but are impractical and require a vast amount of computational power.

#### Diffie-Hellman

The first publicly known public-key algorithm was the Diffie-Hellman (DH) key exchange algorithm, proposed in 1976 [DH76]. The underlying structure of DH is based on modular exponentiation, and the security relates to the discrete logarithm problem, DLP.

**Definition** (DLP). Given a prime p, a generator g of  $\mathbb{Z}_p^*$ , and an element  $\alpha \in \mathbb{Z}_p^*$ , it is difficult to find the integer  $x, 1 \le x \le p-1$ , such that  $g^x \equiv \alpha \mod p$ . The integer x is called the discrete logarithm of  $\alpha$  in base g, denoted  $\log_q \alpha$ .

Assume that Alice and Bob want to exchange a key using DH. They perform the following actions, with all operations performed mod p:

1. They agree on a finite cyclic group G with a primitive root (generator) g and a modulus p. These values are all public.

2. Alice chooses a secret random number  $a \in \mathbb{Z}/p\mathbb{Z}$ , sending  $g^a$  to Bob.

- 3. Bob chooses a secret random number  $b \in \mathbb{Z}/p\mathbb{Z}$ , sending  $g^b$  to Alice.

- 4. Alice now computes  $(g^b)^a$ , while Bob computes  $(g^a)^b$ . Alice and Bob now share the secret  $g^{ab}$ .

Due to the Pohlig-Hellman algorithm [PH78], the security of a group G is limited by the largest, prime order, subgroup of G. Hence, it is common to generate a so-called safe prime, using a Sophie Germain prime q to calculate p=2q+1. This prime makes the order of the group G divisible only by 2 and q.

The number field sieve [Len+90] is one of the most effective attacks against discrete logarithms. It was used in the LogJam attack in 2015 to break 512-bit Diffie-Hellman groups [Adr+15] by performing precomputation based on p, leading them to attack any Diffie-Hellman instance using the prime p. The authors estimate that the attack is plausible even at 1024 bits, using nation-state resources. Finally, they recommend the usage of 2048 bit primes or switching to elliptic curves instead. NIST also recommends using at least 2048 bit primes for discrete logarithm based protocols<sup>11</sup>.

Plain Diffie-Hellman (DH), also known as anonymous Diffie-Hellman, is vulnerable to Man-in-the-Middle (MitM) attacks due to the keys not being authenticated. One solution is to digitally sign the transmitted parameters,  $g^a$  and  $g^b$ , by using, e.g., RSA. If the keys used in DH are long-term keys, we call it static Diffie-Hellman. Ephemeral Diffie-Hellman (DHE) uses a new public key for every instance of the protocol. For DHE, if the long-term signing key is compromised, it does not affect the security of past sessions, resulting in Forward Secrecy (FS).

The current best practice for (D)TLS is to only use forward-secrecy-only ciphers [SHS15]. In TLS 1.3, all public-key based key exchange schemes provide forward secrecy [Res18].

# Elliptic Curve Cryptography

Instead of performing calculations in the finite group  $\mathbb{Z}_p$ , we can define an *elliptic curve* over a field K. An elliptic curve is defined as a set of solutions of an elliptic function, e.g., the curve, in Weierstrass form,

$$y^2 = x^3 + ax + b, \quad a, b \in GF(q),$$

(2.1)

q being an odd prime. The points on the curve form an ordered pair  $\langle x,y\rangle$ , with the coordinates being elements of  $\mathrm{GF}(q)$  that satisfies the curve equation. There is a particular point,  $\mathcal{O}$ , known as the point at infinity. This set of points forms a group under addition, using the chord-tangent process.

The strength of elliptic curves is related to discrete logarithms, known as the elliptic curve discrete logarithm problem, ECDLP. That is, for an integer m, we

<sup>&</sup>quot;https://www.keylength.com/en/4/

denote the summation of a point P with itself m times, as [m] P. This multiplication is easy to compute, but it is believed to be hard to invert.

The best-known attack against a general elliptic curve is the parallel Pollard's Rho algorithm [VW99], with a complexity of about  $\mathcal{O}(\sqrt{q})$ . To achieve a security level of 128 bits, we need to let  $q\approx 2^{256}$ . Note that this is much smaller than the group size of Diffie-Hellman.

The key generation for ECC is shown to be significantly faster compared to RSA. The time for generating ECC keys is linear with respect to the key size, while it is exponential for RSA [JA04]. It is also shown that signature verification is faster for RSA, due to the small *e*. The smaller key size for ECC also results in reduced memory footprint and less bandwidth during transmission.

The are multiple standardized elliptic curves, which are believed to be secure, described next [Che+19]. Curves recommended by NIST include P-224, P-256, P-384, and P-521. These curves are all so-called Weierstrass curves, given in Eq. 2.1. The prime field used in the NIST curves are based on generalized Mersenne primes.

**Definition** (Generalized Mersenne Prime). A generalized Mersenne prime is a prime of the form

$$2^{c_n} + \left(\sum_{i=1}^{n-1} -1^{b_i} 2^{c_i}\right) - 1,$$

where

$$b_i \in \{0, 1\},$$

$$c_1 > 0, \ c_{i-1} < c_i, \ c_n \ge n.$$

This allows for efficient modular reduction without using division [Sol+99].

The elliptic curve Curve25519 [Ber06] is a Montgomery curve, which allows for fast x-coordinate point operations, which may offer better performance than the NIST curves. A Montgomery curve is defined by

$$By^2 = x^3 + Ax^2 + x, \quad A, B \in K$$

(2.2)

over a field K, usually GF(q).

Brainpool curves [LM10] use verifiable pseudo-random primes, compared to the NIST curves. These primes may prevent attacks using backdoored designs. However, due to the randomness, fast reduction algorithms are no longer possible, leading to performance penalties<sup>12</sup>.

As new attacks are invented, we increase the parameters of the cryptographic algorithms. While this may be a good enough solution to make the algorithms

$<sup>^{12} \</sup>verb|https://tls.mbed.org/kb/cryptography/elliptic-curve-performance-nist-vs-brainpool$

secure, the more complex the algorithms are, the more resources it requires to perform the computations. This complexity is not desirable in small, constrained systems. This is a case where the system architect needs to decide to either increase parameters or replace the algorithms with new, hopefully more lightweight, ones.

Let us now shift our focus to symmetric ciphers. In a symmetric cipher, a key is generated and shared between entities. The key must be kept a secret for other parties not to be able to decrypt the data. Symmetric ciphers are categorized as either block ciphers or stream ciphers, described next.

#### 2.2.2 Block Ciphers

A block cipher operates on blocks of text, mapping n-bit plaintext to n-bit ciphertext, where n is the block size. For example, AES uses a block size of 128 bits. The encryption function  $C = E_K(P)$  of a block cipher must be invertible, with the inverse function,  $P = D_K(C)$ , being the decryption function, for a given key, K, and plaintext, P. How messages larger than a block are handled is described next.

For messages exceeding the block size, n, we split the message into n-bit chunks. The way the chunks are processed is known as the *mode of operation* of a block cipher. In the simplest case, known as electronic-codebook, or ECB, each chunk is processed separately. This mode has weaknesses, e.g., if two blocks of plaintexts are identical, so will the corresponding ciphertexts be. Modern modes of operation are based on block chaining or counters, such as CBC and CTR mode.

If a scheme also allows for authenticating unencrypted data, we call it an authenticated encryption with associated data, or AEAD, scheme [Rog02]. Authenticated encryption has been studied for a long time with several proposed ways of achieving secure designs. A message authentication code (MAC) is a piece of data providing integrity and authenticity to a message. A MAC is generated and verified using a shared secret key. It is a symmetric version of a digital signature. MACs can be constructed using cryptographic primitives such as block ciphers and universal hash functions [CW79]. Generally, there are three ways of combining a symmetric encryption scheme and a MAC: *Encrypt-then-MAC*, EtM; *Encrypt-and-MAC*, E&M; *MAC-then-Encrypt*, MtE. The authors in [BN00] show that the MtE and E&M schemes are insecure in some settings.

Modern AEAD schemes include the GCM [MV04] and CCM [WHF03] modes, both recommended to use according to NIST [Dwo04; Dwo07], described next.

GCM This mode combines counter mode encryption with Galois mode authentication, calculated over a field  $GF(2^w)$ , commonly  $GF(2^{128})$  defined by

$$\mathbb{F}_2[x]/(x^{128}+x^7+x^2+x+1).$$

Like the counter mode, GCM uses an incrementing counter and an IV as input to the block cipher, which essentially turns it into a stream cipher. For authentication, the GHASH [WC81] function is used, which requires multiplications in the above described field.

GCM allows for parallel computation and efficient use of CPU pipelines, making it fast and efficient, both in software and in hardware [MV05].

CCM This mode combines the counter mode encryption with the CBC-MAC authentication code. This combination is an application of the Authenticate-then-Encrypt scheme. The authors in [KR11b] show that CCM is slightly faster than GCM for smaller messages on x86 and ARM Cortex-A8, but slower for larger message sizes.

CCM-8 uses eight octets for the authentication tag, compared to the usual 16, which reduces the message size at the cost of security.

CCM\* is a variant used in low-rate wireless networks, IEEE 802.15.4. Besides the normal CCM operations, CCM\* also supports an encryption-only mode.

Let us now dive deep into the area of stream ciphers. Even though there exists public-key stream ciphers such as the Blum-Goldwasser scheme [BG84], we only look at the symmetric case.

# 2.2.3 Stream Ciphers

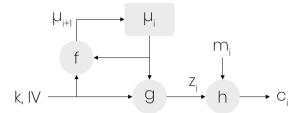

A stream cipher operates on a stream of symbols, see Figure 2.2 for a general architecture. Compared to a block cipher, a stream cipher has a state which is updated as it produces keystream. A stream cipher is an approximation of the Vernam cipher, which is known to be information-theoretically secure [Sha49]. A cryptographic primitive is said to be information-theoretically secure if there exists a proof that an attacker, even with infinite computational power, can not break it. More formally,

$$H(M|C) = H(M),$$

where H(X) is the entropy of X. That is, an attacker observing a ciphertext does not gain any information about the plaintext.

The Vernam cipher uses a key of the same size as the message, a requirement that is not applicable to *most* modern use cases. Instead, a limited finite-state is used to derive a keystream used for encrypting a message. Since the state is finite and the algorithm is deterministic, a conventional stream cipher is not information-theoretically secure. Instead, a stream cipher is an instantiation of a pseudo-random generator, PRG, and offers semantic security [GM84; Gol09].

The general advantage of a stream cipher compared to a block cipher, in hardware, is higher speed and lower circuit complexity. Stream ciphers are also capa-

Figure 2.2: General model of a stream cipher, with the initial state  $\mu_0$ , the key k, the initialization vector IV, the next-state function f, the keystream generator g, the keystream  $z_i$ , the output function h, along with the plaintext  $m_i$  and the ciphertext  $c_i$ .

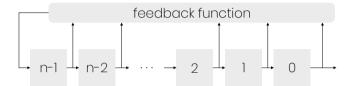

Figure 2.3: An LFSR in Fibonacci configuration.

ble of processing streaming data, e.g., network or mobile traffic, on-the-fly, while block ciphers need to buffer the data up to whole blocks.

There are multiple ways of constructing a stream cipher. One common approach is to use a linear-feedback shift register (LFSR) design. A shift register is a composition of multiple flip-flops connected in series. The feedback function updates the LFSR input with a value based on the previous state. It is common to use the linear XOR gates to construct the feedback functions. The flip-flops which are part of the feedback are called *taps*.

There are two ways of arranging the flip-flops and the feedback functions: Fibonacci and Galois configuration. In the Fibonacci configuration, the flip-flops are connected directly in series, and only the input of the last flip-flop is updated with the output from the feedback, see Figure 2.3. In Galois configuration, the XOR gates are located between flip-flops, controlled by the output of the LFSR. For an LFSR, a Fibonacci configuration may always be transformed into its corresponding Galois configuration. Due to their differences, the initial state may be different in order to produce the same output sequence. The Galois configuration is usually more efficient in software since it allows operations on multiple bytes simultaneously.

The feedback function may be expressed as a polynomial in a finite field mod 2, where the taps correspond to a monomial with coefficient 1. This construction allows us to use the mathematical theory about finite field arithmetic. We know that a primitive polynomial produces a maximal cycle length, which allows us to construct an LFSR producing the longest possible sequence before the cycle

repeats. A sequence produced by a maximal LFSR is known as *maximum length sequence*, or *m-sequence*. An m-sequence is a pseudo-random sequence with many interesting properties related to randomness [Gol+67]. Some properties are given below.

- The sequence is almost perfectly balanced. That is, there are  $2^{n-1}$  ones and  $2^{n-1}-1$  zeros. The zero-state only generates zeros; hence it is not particularly useful.

- Half of the runs are of length 1,  $\frac{1}{2^n}$  of the runs are of length n. There is also a single run of n ones and n-1 zeros.

- If a sequence is shifted by any non-zero number, the new sequence will have

2<sup>n-1</sup> 1 elements the same as the original sequence, and 2<sup>n-1</sup> elements

different. Interpreting the sequence as containing +1's and -1's instead of 1

and 0, the normalized autocorrelation function is given by

$$R(m) = \begin{cases} 1 & \text{if } m = 0, \\ -\frac{1}{N} & \text{if } 0 < m < N. \end{cases}$$

with N being the period of the sequence.

Adding two phase-shifted m-sequences results in another phase-shift of the same m-sequence.

There are many applications of m-sequences, such as measuring impulse responses in order to create reverberation effects for musical instruments [Val+12]. The impulse response is extracted from the measured system by a circular cross-correlation with the m-sequence. This operation works due to the autocorrelation of an m-sequence approximates the unit impulse, i.e., a Kronecker delta.

Even though m-sequences and general LFSR-based designs are widely used and work well, one can not only use an LFSR to generate secure keystream, due to its intrinsic linearity. The famous Berlekamp-Massey (BM) algorithm finds the shortest LFSR producing a given finite sequence [Ber68; Mas69] in  $\mathcal{O}(n^2)$  time, only requiring 2n consecutive bits to reconstruct an LFSR with length n. To mitigate these attacks, different approaches are taken to introduce non-linearity, described next.

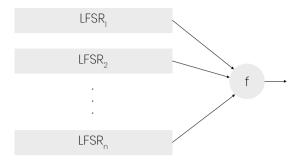

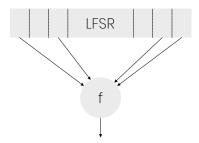

#### Non-linear Combining Functions

Here, we take the output of multiple LFSRs and combine the outputs via a non-linear Boolean function, see Figure 2.4. With n LFSRs in  $\mathbb{F}_q$ , the function is the mapping  $\mathbb{F}_q^n \to \mathbb{F}_q$ . The output can be given as

$$z = f(L_1, L_2, \dots, L_n).$$

**Figure 2.4:** General architecture of a stream cipher based on a non-linear combiner design.

A Boolean function needs certain properties to be applicable in stream cipher applications. Here, we present some of these properties, as given in [SM00].

**Balanced** A Boolean function, f, of n variables is said to be balanced if the Hamming weight  $wt(f) = 2^{n-1}$ . That is, there is an equal distribution of ones and zeros.

**Nonlinearity** A Boolean function, f, of n variables is said to have nonliearity m if the smallest Hamming distance between f and all n-variable affine functions is m.

**Algebraic degree** A Boolean function, f, of n variables can be represented as a polynomial in the algebraic normal form, ANF. The degree of this polynomial is called the algebraic degree, denoted deg(f).

Correlation immunity A Boolean function, f, of n variables is said to be correlation immune of order k if all sets of k variables, or fewer, are statistically independent of the output of f. That is, the random variable

$$Z = f\left(X_0, \dots, X_{n-1}\right)$$

is statistically independent from any random vector

$$(X_{i_1},\ldots,X_{i_k})$$

.

A balanced Boolean function with correlation immunity of order k is said to be k-resilient.

This leads to high linear complexity for the keystream; hence the BM algorithm becomes computationally hard. The Geffe generator [GP73] is an example of an architecture utilizing a non-linear combiner function. The problem with the stateless combiner functions is that they are susceptible to correlation attacks such

as [MS89]. To counter these types of attacks, the authors proposed Boolean functions with no good linear approximation, and which are also correlation immune, such as stateful combiners.

$E_0$  is a stream cipher used in Bluetooth [Blu19]. Although it is recommended to use AES-CCM when possible,  $E_0$  is kept for legacy reasons.  $E_0$  consists of four LFSRs with lengths 25, 31, 33, and 39, all using primitive polynomials. The output is generated by an FSM, called a summation combiner, thus being a stateful combiner. By using only a small number of memory cells,  $E_0$  is still vulnerable to attacks, such as that in [Cou04].

Another approach for increasing non-linearity is to use a nonlinear-feedback shift register, NFSR. An NFSR uses a feedback function, which is a non-linear function of the FSR state, usually by including AND and OR gates. Such construction is found in the Achterbahn cipher.

The Achterbahn stream cipher exists in two versions: Achterbahn-80 and Achterbahn-128, consisting of 11 and 13 NFSRs, respectively, with lengths ranging from 21 to 33. The output of the cipher is fed into a non-linear combiner function. For example, the combiner function, F, used in Achterbahn-128 has properties such as:

- · It is balanced

- It is correlation-immune of order 8

- It has non-linearity 3584

Due to all NFSRs being rather short and independent, attacks, where the output functions are linearized, are shown to be effective [JMM06]. The authors in [HJ07] observed a stronger dependency between the input to the Boolean function and its output than previously assumed. This dependency led the authors to mount an attack requiring less complexity than brute force.

#### Non-linear Filter

Instead of using multiple LFSRs, we can use a single LFSR and use the state values to be the input to a non-linear output function, see Figure 2.5. That is, given the internal states  $s_1, s_2, \ldots, s_L$ , the output is given by

$$z = f(s_1, s_2, \dots, s_L).$$

A non-linear filter design may be transformed into a non-linear combiner design by replicating the LFSR L times and shifting the initial state accordingly. The properties of the filter function are equal to the properties described for the combiner case.

The SNOW cipher, introduced in [EJ00], is a word-oriented stream cipher based on non-linear filter design. It has been updated as SNOW 2.0 in [EJ02],

Figure 2.5: General architecture of a stream cipher based on a non-linear filter design.

and as SNOW 3G in [3GP06]. Due to the non-random behavior of the ciphers, the authors in [KY11] were able to mount an attack based on related-key pairs. The latest version, SNOW-V, was proposed in [Ekd+19]. Instead of operating on bits, SNOW-V uses symbols in  $\mathbb{F}_{2^{16}}$ . SNOW uses two LFSRs of length 16 from where symbols enter an FSM, similar to  $E_0$ . The FSM consists of three 128-bit registers: R1, R2, and R3. Two blocks from the LFSR part are used as input to the FSM, which produces a 128-bit keystream. A tag is generated using GMAC. The FSM also uses an S-box based on the Rijndael (AES) round function, to provide strong diffusion. Utilizing AES building blocks allows for fast software implementations due to AES instructions, such as  $_{\tt mm_aesenc_si128}$ , being hardware-accelerated in most modern high-end architectures.

Due to linearity, stream ciphers based on LFSRs are susceptible to attacks such as algebraic attacks [Cou03b] and fast correlation attacks. The authors in [BL06] analyze the security on non-linear filters and combiners, based on known families of attacks, such as trade-off attacks, Berlekamp-Massey attacks, distinguishing attacks, fast correlation attacks, and algebraic attacks. The authors conclude that it is more challenging to protect combiner functions against certain attacks; hence they favor the non-linear filter generator.

The Grain family of stream ciphers is built on the non-linear filter design but uses one LFSR and one NFSR to further increase the non-linearity.

# 2.3 Hardware Design

1947 marks a valuable time in history - the birth of the transistor. The creators: John Bardeen, Walter Brattain, and William Shockley were rewarded with the Nobel Prize in Physics 1956. The transistor revolutionized the field of electronics, replacing vacuum tubes, making it easier and cheaper to manufacture electronic devices such as computers and radios.

Today, the most common type of transistor used in electronics is the Metal–Oxide–Semiconductor Field-Effect Transistor, or MOSFET for short. Estimations show that the MOSFET is the most manufactured component in the history of humanity  $^{13}$ , with a count of  $1.3\times10^{22}$ . In digital circuits, it is most common to use Complementary MOS, CMOS, which consists of symmetrical pairs of n-type and p-type MOSFETs. CMOS circuits are known for having excellent characteristics, such as low power consumption, high noise immunity, and low propagation delay.

Integrated circuits range from general to application-specific devices. General programmable devices include microcontrollers, usually found in embedded systems, such as Atmel AVR, processors such as those in a modern computer, e.g., AMD Ryzen. Domain-specific devices can perform general computations but are more focused on a specific area, or domain, such as Digital Signal Processors (DSPs) and Graphics Processing Units (GPUs), e.g., Nvidia RTX. Field-Programmable Gate Arrays (FPGAs) are re-programmable devices used for implementing both general and specific applications. In contrast, an Application-Specific Integrated Circuit (ASIC) is a hardware component implementing specific functionality very efficiently but can not be re-configured.

Next, we describe the synthesis process, along with optimization techniques for speed, area, and energy.

# 2.3.1 Hardware Synthesis

Designing hardware is easy; designing efficient hardware is hard. Today, hardware is implemented using a Hardware Description Language (HDL) such as VHDL and Verilog for describing the circuit at a register-transfer level (RTL), an abstraction model for the flow of data between registers. Just like compiling high-level source code into executable machine code in software design, the process is similar for hardware. Hardware synthesis is the process where an abstract description of the circuit, from HDL, gets translated into logic gates.

To produce a list of components and their connections, i.e., a netlist, we need to map a standard-cell library. This library contains all building blocks needed to realize the design, such as AND gates, XOR gates, and flip-flops. The exact implementation of the gates is vendor-specific, which leads to different results

$<sup>^{13}</sup> https://computerhistory.org/blog/13-sextillion-counting-the-long-winding-road-to-the-most-frequently-manufactured-human-artifact-in-history/$

in terms of speed, area, and power. Conventional technologies used in industry are 28 nm and 65 nm, but even older technologies such as 90 nm and 130 nm occur. One exception is the desktop and server market, where modern circuits use a process technology of only a few nanometers, such as the 3rd generation Ryzen architectures with a 7 nm technology.

As previously stated, the synthesis tool is responsible for translating the RTL code into physical logic gates, e.g., NAND and NOR, using as "efficient" implementation as possible. By efficient, we usually refer to the number of gate equivalents (GE). A GE is the area of a 2-NAND gate. Although the Boolean circuit minimization problem is  $\sum_{2}^{P}$ -complete [BU08], there exist efficient algorithms, using potential non-optimal heuristics, to facilitate the minimization process, such as Espresso [LS87]. The algorithm utilizes Boolean cubes to represent the ON-, OFF- and DC-sets of the function.

#### 2.3.2 Optimizing Speed

To increase the speed of a design, the first step is to find the bottlenecks. In hardware design, these bottlenecks are known as critical paths. The critical path denotes the longest path a signal must propagate between two flip-flops. This path determines the maximum clock frequency. If a higher clock is used, the signal on the critical path will not have propagated to its destination; hence the circuit will behave erroneously. Once the critical path has been identified, the next step is to make it shorter without altering the circuit behavior. Next, we present some conventional optimization techniques for speed.

### Pipelining

The fundamental concept of pipelining is simple; insert a flip-flop in the critical path, optimally dividing the path in two. If the critical path remains in the same path, the clock frequency may now be doubled. Of course, it is not as easy as this in reality.

First of all, we must make sure that pipelining is applicable. This is done by depicting the design as a graph, with arrows pointing in the data-flow direction. We are only allowed to insert pipeline steps in the feedforward cutset [Pro01]. A cutset is a set of edges such that if they are removed (cut), it results in two disjoint graphs. If data only flows forward on all cutsets, we call it a feedforward cutset. By inserting a pipeline step, we delay the computations by one clock cycle and introduce more hardware.

Even though the pipeline is strategically placed, there might be new paths that become the next critical path. For example, assume that the first critical path has a delay of 1000 ps. We insert a pipeline, dividing the path into two. This yields a 500 ps delay. Now, the next critical path might be somewhere else in the system, with a delay of 995 ps. The effective speed in the system is limited by 995 ps, not 500 ps. Pipelining, while simple, requires a thorough analysis of the whole system.

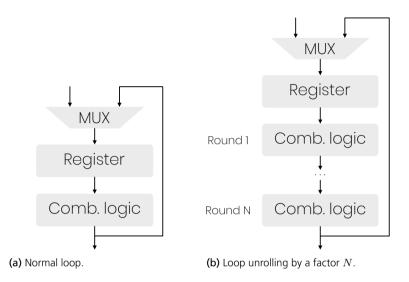

#### Loop Unrolling

Loop unrolling is a technique for improving the execution speed of a loop at the expense of the area. Unrolling a loop by a factor N, the body of the loop is repeated N times, and the total amount of loop iterations is reduced, see Figure 2.6. This reduces the amount of overhead from the loop itself.

Figure 2.6: Implementation of a loop in hardware.

There is, of course, a trade-off to be made between area and speed, and it is not always obvious what unrolling factor N results in the "best" design. An example of a design using unrolling is found in [GC09], where the authors implement and analyze AES with different levels of unrolling, showing that the throughput increases with N, but higher degrees of unrolling has a minimal increase in speed but a high area penalty.

# 2.3.3 Optimizing Energy

Minimizing energy consumption is an essential goal in circuit design, especially for circuits used in constrained systems. One important note to make here is that low power does not necessarily imply low energy.

Assume that we have a system performing some computation in time  $t_1$ , consuming the power  $P_1$ . We manage to reduce the power consumption to  $P_2=0.5P_1$ , which increases the computation time to  $t_2=4t_1$ . Now the total energy consumption after reducing the power is actually twice the initial energy consumption, i.e.,  $E_2=2E_1$ . Since the lifetime of a battery is proportional to the energy consumption, we should stick to the initial implementation.

26 Background

The relation between power and energy is not obvious; it depends on the system design and optimization techniques used. Analysis is a must to achieve the required result.

Loop unrolling is not only used for increasing the speed of a circuit. It may also lower energy consumption, as shown in [BBR15].

#### **Clock Gating**

Clock gating is a technique where the clock signal to a circuit, or part thereof, is disabled. This results in the flip-flops not being switched, which reduces the dynamic power consumption of the transistors. As described in Section 2.1.1, clock gating may be used to implement sleep modes in a system.

Studies show that the clock signals in digital circuits consume a significant fraction of the total power. Applying a clock gating scheme may have a tremendous impact on the total power consumption of the system [Mah+09].

#### 2.3.4 Optimizing Area

The cost of the die is proportional to its area<sup>14</sup>. Hence, it is beneficial to make the chip as small as possible. Next, we present conventional area-optimization techniques.

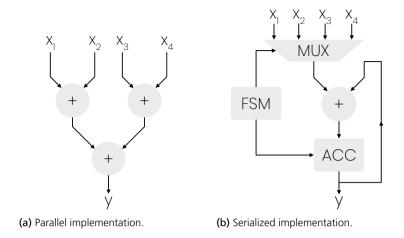

#### Logic Reuse

One way to save area is to reuse existing functionality by time-multiplexing. The goal is to determine the smallest amount of basic functional blocks required to implement the functionality. Assume that we need to implement the following function,

$$y = x_1 + x_2 + x_3 + x_4$$

.

A naïve implementation requires three adders. The corresponding hardware architecture is shown in Figure 2.7a.

Another description of the function would be given as we can instead describe the function as

$$y = \sum_{i=1}^{4} x_i,$$

thereby using only a single adder, but in a loop over time. This reduces the area of the adders, at the cost of latency. However, we need a state machine to control the flow of data in the second case, since it executes serially. The corresponding architecture is shown in Figure 2.7b. As seen in the figure, for this small example, it is not apparent which of the designs would yield a smaller area. For more complex

<sup>14</sup>https://mycmp.fr/technologies/price-list.html

**Figure 2.7:** Hardware implementation of an adder circuit. The serialized implementation uses an accumulator (ACC) to store intermediate values adding up to the final sum. A finite state machine (FSM) is used for controlling the dataflow.

functions, there could be lots to gain in area reduction, but this has to be carefully analyzed.

#### **Custom Logic**

During synthesis, the tool maps the RTL code to a specific cell library. This library contains all fundamental gates necessary to realize any logic function, such as NAND, NOR, XOR, multiplexers, and flip-flops. The gates are usually implemented using CMOS logic.

When talking about area optimization, one usually refers to the number of fundamental gates, like those listed above. However, even if any logic function can be described in terms of a minimal amount of NAND and NOR gates, it does not necessarily mean the realization uses a minimal number of transistors.

The most common approach when designing logic gates is to use complementary MOS, CMOS, technology. A CMOS gate consists of two parts - a *pull-up network* (PUN) and a *pull-down network* (PDN). The PUN provides a connection from the power supply,  $V_{dd}$ , to the output when the corresponding Boolean function equals 1. The PDN connects the output to ground,  $V_{ss}$ , when the function equals 0. The two networks are mutually exclusive, in the sense that only one network is active at a time, sourcing or sinking current. The PUN consists of PMOS transistors due to their ability to source current. Conversely, the PDN consists of NMOS transistors due to their ability to sink current [RCN02].

NMOS transistors in series correspond to a NAND function, whereas NMOS in parallel resembles a NOR function. Similarly, PMOS transistors in series correspond to a NOR function, while PMOS in parallel realizes a NAND function. By

28 Background

| Gate   | Transistors |

|--------|-------------|

| 2-NAND | 4           |

| 3-NAND | 6           |

| 2-NOR  | 4           |

Table 2.2: Common transistor count for NAND and NOR gates.

De Morgan's theorems, one can show that the PUN and PDN are *dual* networks, hence one only needs to construct one of the networks, with the other one being easily derived. CMOS logic is inverting and can only implement functions such as NAND and NOR. An additional inverter is required to implement AND and OR functions.

The power of synthesizing CMOS gates directly, not using standard gates, is apparent when the gates get complex. Consider the Boolean function

$$F = \overline{D + A \cdot (B + C)}.$$

Minimizing the expression in disjunctive form yields

$$F = \overline{BCD} + \overline{AD}$$

,

which requires a 3-input NAND, a 2-input NAND, and a NOR gate. From Table 2.2, we see that the cost of the function, F, in number of transistors is 14. Using methods for designing complex CMOS gate, we can implement the PDN using four transistors where B and C are in parallel, A is in series with B and C, and finally, D is in parallel with A, B, and C. Due to the PUN being the dual to the PDN, it uses an equal amount of transistors. Thus, we conclude that F can be implemented using eight transistors, which is  $\approx 43\%$  less than before.

It is worth noticing that the CMOS design of a Boolean function minimizes the transistor count, using that technology. That being said, other technologies may be used, resulting in an even lower transistor count.

# Transistor Technology

A popular alternative to CMOS logic is pass-transistor logic (PTL), intending to minimize the number of transistors required to implement a Boolean function. The difference is that we allow the input signals to drive both the gates and the source-drain terminals, whereas in CMOS logic, we only let the gates be driven by the input signals. Using this approach enables us to design a 2-AND gate using only four transistors, instead of six.

One drawback with this approach is that an NMOS, as stated earlier, efficiently sinks current, but is poor at sourcing current. That is, the NMOS can not pull a node high, but will only output  $V_{dd} - V_{th}$ . A widely used solution

29

to the problem with dropped voltage is to utilize so-called *transmission gates*. The idea is to use an NMOS to pull down (sink) and a PMOS to pull up (source). This is realized by placing the NMOS and PMOS in parallel, with complementary control signals to the gates. This allows for efficient implementation of complex gates without the voltage drop problems. For example, an XOR gate may be realized using only six transistors, compared to 12 for a complementary implementation [WFF94]. These kinds of transistor-reducing techniques were utilized by the designers of the Zilog Z80 CPU [Shi13].

# Contributions and Conclusions

#### 3.1 Contributions

In this chapter, we summarize the contributions of the papers included in this dissertation. This chapter ends with some conclusions.

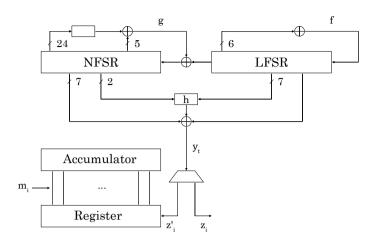

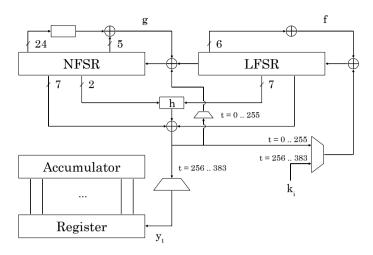

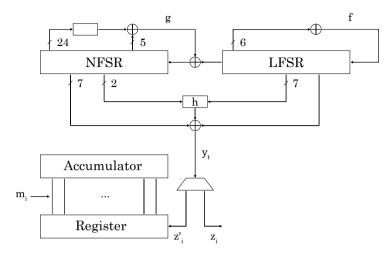

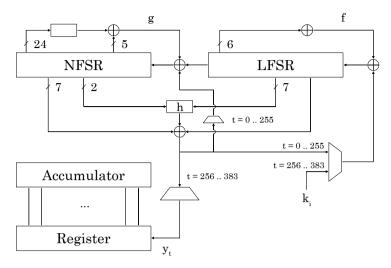

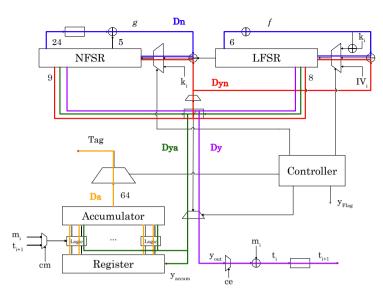

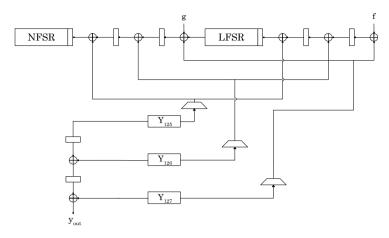

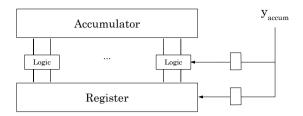

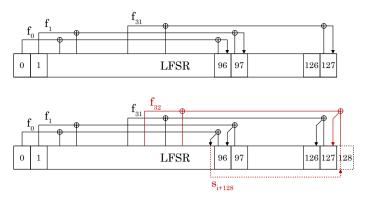

#### 3.1.1 An AEAD Variant of the Grain Stream Cipher

In Paper I, a new version of the stream cipher Grain is presented, Grain-128AEAD. Following the latest recommendations from NIST, Grain offers authenticated encryption with associated data at a 128-bit security level. Grain is designed to be lightweight to fit in the most constrained environments. At the time of writing, Grain-128AEAD is currently one of 32 ciphers managing to proceed to round 2 of the NIST lightweight cryptography standardization process<sup>1</sup>.

To mitigate attacks on previous versions of Grain, Grain-128AEAD no longer supports encryption only. The authentication tag has been extended to 64 bits. During the initialization, the key is re-introduced in order to randomize the state, thwarting key-recovery attacks. The keystream is also limited to  $2^{80}$ , to make attacks using linear approximations more difficult.