## LUND UNIVERSITY

#### **Test Cost Reduction of 3D Stacked ICs**

#### Test Planning and Test Flow Selection

Sengupta, Breeta

2020

Document Version: Publisher's PDF, also known as Version of record

#### Link to publication

Citation for published version (APA):

Sengupta, B. (2020). *Test Cost Reduction of 3D Stacked ICs: Test Planning and Test Flow Selection*. [Doctoral Thesis (monograph), Department of Electrical and Information Technology]. Department of Electroscience, Lund University.

Total number of authors:

#### General rights

Unless other specific re-use rights are stated the following general rights apply:

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights. • Users may download and print one copy of any publication from the public portal for the purpose of private study

- or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal

Read more about Creative commons licenses: https://creativecommons.org/licenses/

#### Take down policy

If you believe that this document breaches copyright please contact us providing details, and we will remove access to the work immediately and investigate your claim.

LUND UNIVERSITY

**PO Box 117** 221 00 Lund +46 46-222 00 00

# Test Cost Reduction of 3D Stacked ICs

### Test Planning and Test Flow Selection

Breeta SenGupta

LUND UNIVERSITY

Doctoral Dissertation 3D Stacked Integrated Chips Lund, September 2020

Breeta SenGupta Department of Electrical and Information Technology 3D Stacked Integrated Chips Lund University P.O. Box 118, 221 00 Lund, Sweden

Series of licentiate and doctoral dissertations ISSN 1654-790-132; No. 132 ISBN 978-91-7895-562-6 (print) ISBN 978-91-7895-563-3 (pdf)

© 2020 Breeta SenGupta Typeset in Palatino and Helvetica using  $\[\] T_E X 2_{\mathcal{E}}$ . Printed in Sweden by Tryckeriet i E-huset, Lund University, Lund.

No part of this dissertation may be reproduced or transmitted in any form or by any means, electronically or mechanical, including photocopy, recording, or any information storage and retrieval system, without written permission from the author. To my parents and Guha sir

### Popular Science Summary

It would certainly be pretty difficult, if not impossible, to find a person who would not fancy owning gadgets they flaunt in Star-Trek, or for that matter, in any Sci-Fi film. And would that be too irrational of us to imagine it to be as affordable as any ordinary gadget we own at present? Following recent advances in science and electronics, it is not unlikely we see that day before we see our grandchildren!

As technology progressed, the heart of all gadgets, the Integrated Circuit or IC, became crowded by the day. Technology had hit the wall when no more could be accommodated within the IC without making our gadgets perform worse. But, technology bounced back with this magnificent solution that held exceptional promises.

Typically ICs had been produced where only one layer of components crowded interiors of the black box, like people in a single storeyed building. But with the new solution, components were now being shared over several layers within the IC. We had evolved into the age of multi-storeyed buildings. We called these multi-layered ICs the 3D Stacked IC. Amongst the first of its kind was the test chip, Pentium 4 processor produced by Intel corporation in the year 2004. The three dimensional version, where circuitry was shared among two layers, gave a performance boost and power saving upon single layered IC by fifteen percent each.

With new ideas came new challenges.

Just as one would essentially need to enter or exit a multi-storeyed structure from the ground floor, so was the case of signals within the 3D Stacked IC. And instead of stairs, electrical signals travels vertically along the layers of the 3D Stacked IC through copper wires. These copper wires, which have a thickness of just a few nanometers are called the Through-Silicon-Vias, in short, TSVs. However, when even the human hair posed ten times the width of TSVs, constructing them did not come easy. Things got even worse when millions of perfectly made TSVs were required in each layer of the 3D Stacked IC. TSVs were constructed separately for each layer, and eventually lined up. Imagine yourself cutting one strand of hair, and gluing it back exactly as it was! It is also true, not every time do we construct each of the TSVs and line them up impeccably. Neither, in the first place, had we always been precise about creating single layered ICs.

#### To err might be human, but so is to aspire against!

We confronted the errors in our ICs by developing test mechanisms that ascertained only good ICs were incorporated within our gadgets. However, these test mechanisms did not come for free. All the more, as improved technology kept reducing the cost of manufacturing ICs, not much progress was made in the domain of tests. This led to a test cost accounting for more than three quarters of the total cost for present day ICs. This still pays off for the losses that the manufacturers would have otherwise encountered. For the past half of the century research has been conducted to improve the test of single layered ICs. But 3D Stacked IC brings about a whole new dimension to testing. That includes consideration of TSV technology, among many others. Over the past half of the decade rigorous research is being performed on improving test mechanisms for 3D Stacked IC. Each research has contributed to the betterment of test mechanism for the 3D Stacked IC, howsoever insignificant it may seem. A design and manufacturing group at IMEC, Belgium has suggested several mechanisms to adapt traditional testing strategies for ICs to the 3D Stacked IC. This includes planning of additional circuitry to be incorporated within the 3D Stacked IC that would be involved in testing the TSVs. Research groups at the Georgia Institute of Technology, and University of Michigan have helped develop prototypes for the same.

However, the price we pay for test may not always be tangible. A large share of the cost is the testing time. The remainder of which is accounted for the circuitry, machinery and equipment dedicated for testing. Saving, what might seem a negligible amount of the test time on each IC might prove profitable in the long run. The testing time of an IC in itself takes less than a minute. It would then enable us to test many more ICs per hour, if even the reduction of test time is a mere second. This in turn would facilitate production of thousands more ICs per day, thereby adding to the profit.

Not much activity has been observed that address the issue of reducing test time for 3D Stacked ICs. A major share of this test time accounts for the many additional stages of production during which 3D Stacked ICs may be tested. Researchers at the Department of Electrical and Information Technology at Lund University in Sweden have shown that random decisions of performing tests at various stages of production might lead to a few hundred times of the minimum test time. They addressed this problem for the first time by building a mathematical model that helps minimize test time by making the right choices during the manufacturing steps, whether or not to perform a test.

In addition, they provide several cost effective measures of laying out the circuitry and organizing tests. This may in some cases help reduce the total cost of the 3D Stacked ICs by up to a tenth.

It may seem infinitesimal, but with each tiny step we strive to create gadgets that do not only provide a superior performance, which also are more robust and reliable. With further improvement in test and manufacturing technologies, slowly but certainly we look forward to the future fancied only in science fiction until now. While Intel engages itself in refining 3D Stacked IC technology with two layers of varying technology, reputed names like Samsung and IBM have been mooting the idea of an eight layer memory stack.

With each new step, past multi-storeyed structures, the age of skyscrapers now dawns upon us!

### Abstract

Ever higher levels of integration within the Integrated Circuit (IC) to meet progressively widening scope of its application in respect of functionality, size, performance and manufacturing issues inspired development of the three-dimensional (3D) Stacked IC as a device having viable architecture. However, with increased complexity, manufacturing cost increased. The manufacturing cost includes the test cost component, essential to ensure fidelity to the desired design specifications. Of the several challenges faced by 3D Stacked ICs, cost efficient testing of the manufactured product is most critical. Reduction of test cost for 3D Stacked ICs through test planning along with test flow selection methods is addressed in this thesis.

Test planning for 3D Stacked ICs is performed by reducing the total cost accounting for the test time and Design-for-Test (DfT) hardware. Three test architecture standards are used: Built-In Self-Test (BIST), IEEE 1149.1 and IEEE 1500. The test cost corresponding to each test architecture is detailed and test planning algorithms are proposed. The algorithms are implemented and experiments are performed on several 3D Stacked IC designs formed with multiple 2D IC benchmarks. For experiment, a test flow is presented that comprises the wafer test of each chip followed by test of the entire packaged IC. Results indicate effectiveness of the proposed algorithms in terms of test cost.

Test flow selection, to decide stages at which tests are to be performed, for 3D Stacked ICs is addressed motivated towards the reduction of test time required to produce each single fault-free package. A model to calculate the total test time for any given test flow is detailed. An algorithm is proposed to find a test flow for reducing test time. The algorithm is implemented and executed on several 3D Stacked IC designs with up to ten chips in the stack. Results indicate considerable reductions in test time as compared to predetermined test flows.

### Preface

This thesis summarizes my academic work carried out since May 2010. During the period between May 2010 to December 2013, the research work was conducted in the Embedded System Laboratory group at the Department of Computer and Information Science, Linköping University, Sweden. Henceforth the research work has been conducted in the Digital ASIC group at the Department of Electrical and Information Technology, Lund University, Sweden.

The material presented in this thesis is based on the following publications.

#### Journal articles

- B. SENGUPTA, U. INGELSSON, AND E. LARSSON, »Scheduling Tests for 3D Stacked Chips under Power Constraints,« *Journal of Electronics Testing: Theory and Applications (JETTA)*, Vol. 28, No. 1, pp. 121-135, Jan 2012.

- I™ The first author was responsible for the evaluation of the problem, proposing test scheduling methods, implementation of the experiments and composition of the text. The research work is an extension of the article published in DELTA, 2011 and has been carried out by the first author under the guidance of the remaining authors.

- B. SENGUPTA, U. INGELSSON, D. NIKOLOV AND E. LARSSON, »Test Planning for Core-based Integrated Circuits under Power Constraints, *Journal of Electronics Testing: Theory and Applications (JETTA)*, Vol. 33, No. 1, pp. 7-23, Feb 2017.

- IP The first author investigated and proposed the test planning algorithm, and implemented the test planning algorithm for experiments. The research work is an extension of the VTS, 2014 paper, written by the first author under the guidance and constant input from the remaining authors.

- B. SENGUPTA, D. NIKOLOV, A. DASH AND E. LARSSON, »Test Flow Selection for Stacked Integrated Circuits, *Journal of Electronics Testing: Theory and Applications (JETTA)*, Vol. 35, No. 4, pp. 425-440, Aug 2019.

- The first author has developed and implemented the mathematical model used in TFSA for different test architectures, and written with the remaining supervising authors.

#### Peer-reviewed conference articles

- B. SENGUPTA, U. INGELSSON, AND E. LARSSON, »Scheduling Tests for 3D Stacked Chips under Power Constraints,« in 6th International Symposium on Electronic Design, Test and Applications (DELTA), Queenstown, New Zealand, pp. 72-77, IEEE, Jan 2011.

- I™ The research work including the development and implementation of the Partial Overlap and ReScheduling algorithms has been carried out by the first author under the guidance of the remaining authors.

- B. SENGUPTA, U. INGELSSON, AND E. LARSSON, »Test Planning for Core-based 3D Stacked ICs with Through-Silicon Vias,« in 25th International Conference on VLSI Design, Hyderabad, India, pp. 442-447, IEEE, Jan 2012.

- The first author proposed and implemented the test planning algorithms using the test architecture with continuous guidance from the remaining authors.

- B. SENGUPTA, AND E. LARSSON, »Test Planning and Test Access Mechanism Design for Stacked Chips using ILP,« in *VLSI Test Symposium (VTS)*, Napa, CA, USA, IEEE, Apr 2014.

- The ILP was formulated and simulated on IEEE 1500 test architecture by the first author under the guidance of the second author.

The research work has been supported by:

- European Union's 7th Framework Programme's collaborative research project FP7-ICT-2013-11-619871 BASTION Board and SoC Test Instrumentation for Ageing and No Failure Found,

- European Union's 7th Framework Programme's collaborative research project FP7-2009-IST-4-248613 DIAMOND Diagnosis, Error Modeling and Correction for Reliable Systems Design,

- Swedish Research Council (Vetenskapsrådet (VR)) Fault-tolerant design and optimization of multi-processor system-on-chip, Dnr:2009-4480, and

- The Swedish Foundation for International Cooperation in Research and Higher Education (STINT) Design of self-healing system chips, Dnr:YR2007-2008.

### Acknowledgments

First of all, I would like to convey my heartfelt gratitude for my supervisor Prof. Erik Larsson, for giving me the opportunity and his invaluable guidance over all these years.

I would also like to thank my co-supervisors at Linköping University, Dr. Urban Ingelsson and Prof. Zebo Peng, and Prof. Viktor Owäll, as well as Dr. Dimitar Nikolov at Lund University, for the valuable comments and encouragement.

I would like to thank all the professors at the Digital ASIC Laboratory, here at Lund University for your constructive feedbacks and support. Also, thanks to my fellow doctoral students Hemanth, Rakesh, Isael, Babak and the others for letting us be a part of the journey and the most entertaining parties. Thank you Anne Andersson, Pia Bruhn, Erik Göthe and Linda Bienen for the smooth transition from Linkoping helping out with anything formal.

My life away from home started halfway across the world at Linköping, Sweden. I could not have asked for a more cordial welcome from my colleagues at Linköping University. I would like to thank Petru Eles for the most intriguing coffee-break conversations, Unmesh Bordoloi, Ke Jiang, Adrian Lifa, and the entire team for the table-football sessions between the long work hours and the afterworks. To Min Bao for being the wonderful intercontinental travel guide cum companion and Ivan Ukhov for being the patient listener to my endless ramblings. A big thanks to the administrative staff Anne Moe and Eva Pelayo Danils for making life at the department feel like a breeze.

My deepest gratitude to my wonderful colleagues cum mentors at work, Hans Israelsson, Rajeshwari, Hind, Milan, Jörgen and so many others, from whom I learn something everyday while making the workplace as loud as it can get. I am also as thankful to my previous colleagues from EC Solutions, specially Oscar, Mathias and Angela for giving me the opportunity and believing in me.

The acknowledgments would not be close to complete without mentioning Dimitar Nikolov and Farrokh Ghani Zadegan, for simply putting up with me for the longest time, through Linköping University, Lund University, and now Ericsson! Thank you for the fruitful discussions, great travels and most of all for being the wonderful friends I can always count on.

I am deeply grateful to all the friends at my corridor in Linköping, who helped make the corridor a home away from home. I can not begin to count my friends here without appreciating Begoña Montanchez, you are the best, most dependable friend one can ask for! I am equally thankful to your wonderful family for the best Christmases I ever had. Surely, the corridor days would have been dull without the lot of you, especially Miguel, Isabella, Jeremy and Mounika.

All my professors during my undergraduate studies at Indian Institute of Technology, Kharagpur, India, for their continuing support and encouragement during and after my time there, thank you. Also, to my friends from the days, who have not let time zones get the better of us. A big shout out to Resham and Abhinendra whose encouragement and example kept me going. My childhood companions Amrita, Gangotri, Niharika, Ipsita and so many others who may be in different continents, yet just a phone call away. I would like to thank all my teachers ever, who have helped shape who I am today.

Today would not have been remotely feasible had it not been for the immeasurable and unconditional love and sacrifice of the two most important people in my life, my parents. Any amount of gratitude would fall short, yet as a token of my respect, here I dedicate this thesis to my two idols: my parents. I am equally indebted to all my grandparents, whose blessings, I am sure, have always been with me every step of the way. And lots of love to all my cousins, aunts and uncles who make all my vacations home feel like a royal endeavor.

> Breeta SenGupta Lund, June 2020

## Contents

| Popular Science Summary | v     |

|-------------------------|-------|

| Abstract                | ix    |

| Preface                 | xi    |

| Acknowledgments         | XV    |

| List of Figures         | xxi   |

| List of Tables          | XXV   |

| List of Algorithms      | xxvii |

| I | Pro  | ologue                        | 1  |

|---|------|-------------------------------|----|

| 1 | Intr | oduction                      | 5  |

|   | 1.1  | Design of Integrated Circuits | 6  |

|   | 1.2  | Test of Integrated Circuits   | 14 |

|   | 1.3  | Thesis Scope                  | 23 |

|   | 1.4  | Contributions                 | 25 |

|   | 1.5  | Thesis Organization           | 27 |

| 2 | Rel  | ated Work                     | 29 |

|   | 2.1  | Test Architecture             | 29 |

|    | 2.2  | Test Scheduling                 | 35  |

|----|------|---------------------------------|-----|

|    | 2.3  | Test Flow Selection             | 36  |

| II | Te   | st Planning                     | 39  |

| 3  | BIS  | Ted Architecture                | 43  |

|    | 3.1  | System Overview                 | 44  |

|    | 3.2  | Problem Formulation             | 45  |

|    | 3.3  | Motivating Example              | 47  |

|    | 3.4  | Proposed Approach: ReScheduling | 53  |

|    | 3.5  | Experiments                     | 59  |

|    | 3.6  | Discussion                      | 62  |

| 4  | IEE  | E 1149.1 Based Architecture     | 63  |

|    | 4.1  | Test Process                    | 64  |

|    | 4.2  | Problem Formulation             | 68  |

|    | 4.3  | Motivating Example              | 75  |

|    | 4.4  | Proposed Approach               | 78  |

|    | 4.5  | Experiments                     | 82  |

|    | 4.6  | Discussion                      | 87  |

| 5  | IEE  | E 1500 Based Architecture       | 89  |

|    | 5.1  | Test Process                    | 90  |

|    | 5.2  | Problem Formulation             | 93  |

|    | 5.3  | Motivating Example              | 97  |

|    | 5.4  | Proposed Approach Using ILP     | 101 |

|    | 5.5  | Experiments                     | 105 |

|    | 5.6  | Discussion                      | 109 |

|    | _    |                                 |     |

|    | Te   | st Flow Selection               | 111 |

| 6  | Test | Flow Selection                  | 115 |

|    | 6.1  | Problem Formulation             | 116 |

|    | 6.2  | Motivating Example              | 125 |

|    | 6.3  | Proposed Approach: TFSA         | 127 |

|    | 6.4                                     | Experiments                                                                                                                                              | 130                                                                                      |

|----|-----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|

|    | 6.5                                     | Discussion                                                                                                                                               | 140                                                                                      |

|    |                                         |                                                                                                                                                          |                                                                                          |

| IV | Ер                                      | ilogue                                                                                                                                                   | 141                                                                                      |

| 7  | Con                                     | cluding Remarks                                                                                                                                          | 145                                                                                      |

|    | 7.1                                     | Summary                                                                                                                                                  | 146                                                                                      |

|    | 7.2                                     | Future Work                                                                                                                                              | 149                                                                                      |

|    |                                         |                                                                                                                                                          |                                                                                          |

| Ap | pen                                     | dix                                                                                                                                                      | 152                                                                                      |

| •  | •                                       |                                                                                                                                                          |                                                                                          |

|    |                                         |                                                                                                                                                          |                                                                                          |

| v  | Ар                                      | pendix                                                                                                                                                   | 153                                                                                      |

|    | •                                       | •                                                                                                                                                        | 1 <b>53</b><br>155                                                                       |

|    | open                                    | dix A Test Mechanism                                                                                                                                     | 155                                                                                      |

|    | pen<br>A.1                              | <b>dix A Test Mechanism</b><br>Built-In Self-Test (BIST)                                                                                                 | <b>155</b><br>156                                                                        |

|    | <b>ppen</b><br>A.1<br>A.2               | <b>dix A Test Mechanism</b><br>Built-In Self-Test (BIST)                                                                                                 | <b>155</b><br>156<br>157                                                                 |

| Aŗ | A.1<br>A.2<br>A.3                       | dix A Test Mechanism<br>Built-In Self-Test (BIST)                                                                                                        | <b>155</b><br>156<br>157                                                                 |

| Aŗ | A.1<br>A.2<br>A.3                       | dix A Test Mechanism<br>Built-In Self-Test (BIST)                                                                                                        | <ol> <li>155</li> <li>156</li> <li>157</li> <li>162</li> <li>169</li> </ol>              |

| Aŗ | A.1<br>A.2<br>A.3                       | dix A Test Mechanism         Built-In Self-Test (BIST)         IEEE 1149.1         IEEE 1500         dix B 3D Stacked IC Construction         Benchmarks | <ul> <li>155</li> <li>156</li> <li>157</li> <li>162</li> <li>169</li> <li>170</li> </ul> |

| Aŗ | A.1<br>A.2<br>A.3<br><b>ppen</b><br>B.1 | dix A Test Mechanism         Built-In Self-Test (BIST)         IEEE 1149.1         IEEE 1500         dix B 3D Stacked IC Construction         Benchmarks | <ul> <li>155</li> <li>156</li> <li>157</li> <li>162</li> <li>169</li> <li>170</li> </ul> |

#### References

# List of Figures

| 1.1 | Representation of Moore's Law, that states that the num-  |    |

|-----|-----------------------------------------------------------|----|

|     | ber of transistors, per square inch, on a IC doubles ap-  |    |

|     | proximately every two years                               | 7  |

| 1.2 | Manufacturing stages that provide test opportunities for  |    |

|     | traditional ICs: (a) a wafer containing a grid of dies    | _  |

|     | (chips), and (b) a packaged IC                            | 8  |

| 1.3 | Lateral-cross section schematic of a wafer within a pack- |    |

|     | age and the hardware interface                            | 8  |

| 1.4 | Partitioning of IC logic into cores                       | 8  |

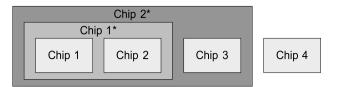

| 1.5 | Block diagram of a packaged 3D Stacked IC                 | 11 |

| 1.6 | A generic approach to testing ICs                         | 15 |

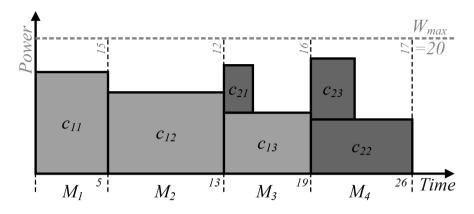

| 1.7 | Test schedule showing the power constraint and time taken | 15 |

| 1.8 | Scan design                                               | 17 |

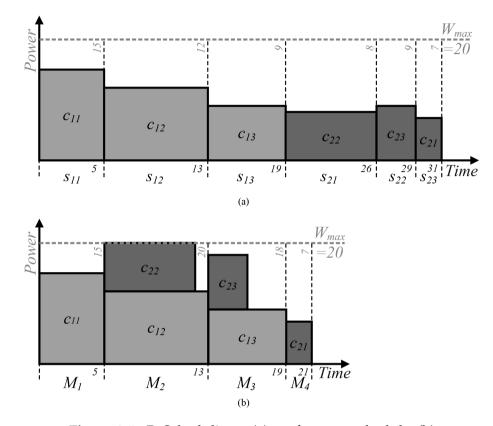

| 1.9 | Test flow comparison between (a) Non-stacked IC, and      |    |

|     | (b) 3D Stacked IC                                         | 20 |

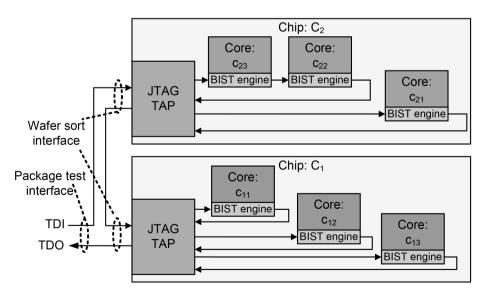

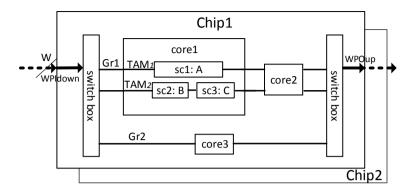

| 3.1 | DfT of a core-based 3D Stacked IC with BISTed cores       | 45 |

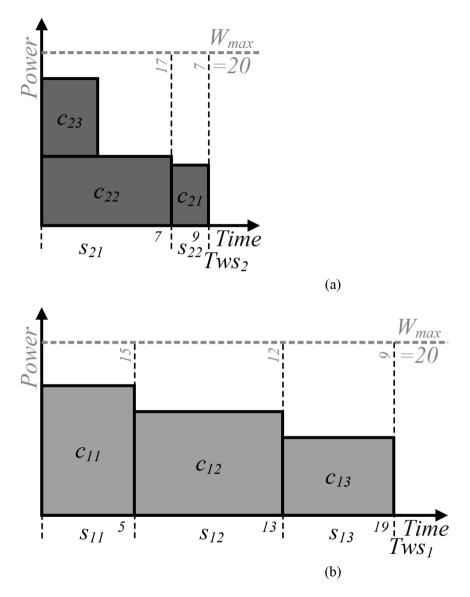

| 3.2 | Scheduling wafer sort of chips comprising the 3D Stacked  |    |

| 0.2 | IC: (a) Chip 1 (b) Chip 2                                 | 48 |

|     |                                                           | -0 |

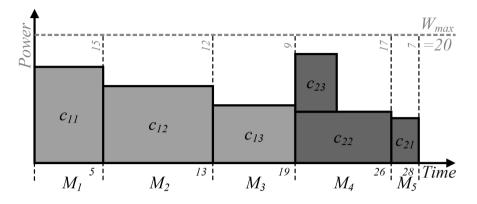

| 3.3 | Package test schedule obtained using by serially per-<br>forming wafer sort tests                                                                                                                                                                                                   | 50  |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 3.4 | Package test schedule obtained by merging power com-<br>patible sessions from different chips                                                                                                                                                                                       | 51  |

| 3.5 | ReScheduling: (a) wafer sort schedule (b) package test schedule                                                                                                                                                                                                                     | 52  |

| 3.6 | Generalization process by abstracting from already processed chips                                                                                                                                                                                                                  | 59  |

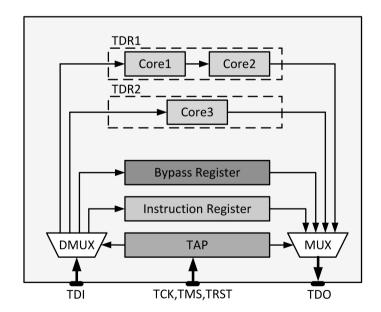

| 4.1 | Test architecture of a non-stacked chip with IEEE 1149.1                                                                                                                                                                                                                            | 65  |

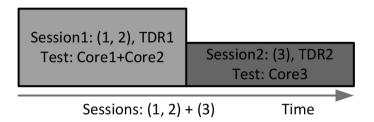

| 4.2 | Sessions formed by core tests                                                                                                                                                                                                                                                       | 66  |

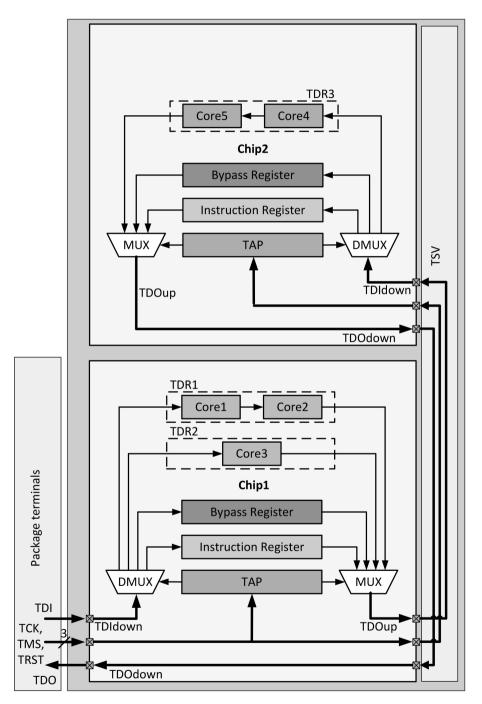

| 4.3 | Test architecture of 3D Stacked IC with a IEEE 1149.1                                                                                                                                                                                                                               | 67  |

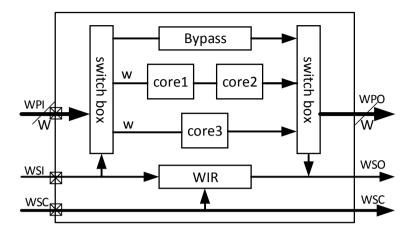

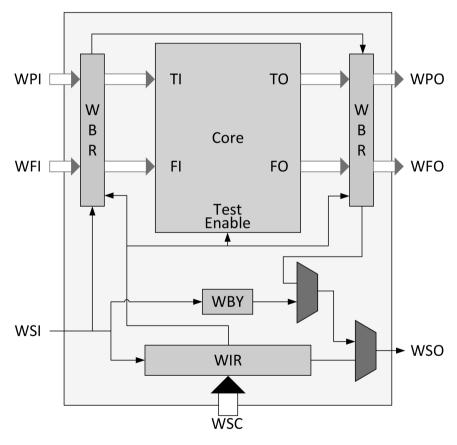

| 5.1 | IEEE 1500 based test architecture of a non-stacked IC                                                                                                                                                                                                                               | 90  |

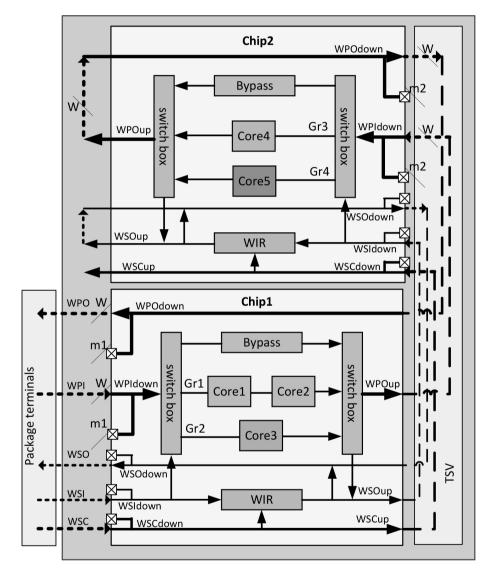

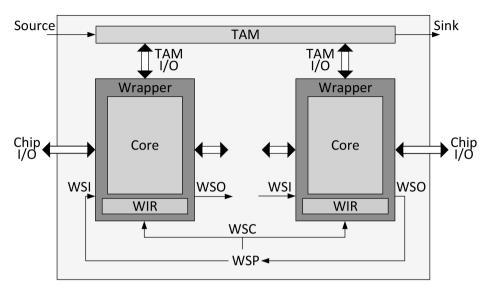

| 5.2 | IEEE 1500 based test architecture of a 3D Stacked IC                                                                                                                                                                                                                                | 92  |

| 5.3 | Scan-chains configured into wrapper-chains in Core1 of Chip1                                                                                                                                                                                                                        | 93  |

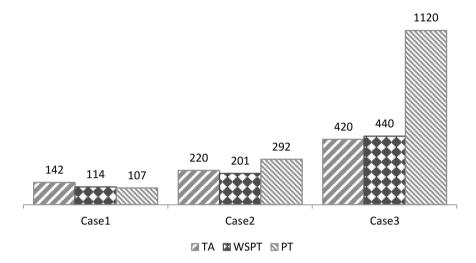

| 6.1 | Comparison of expected total test times for three test<br>flows – TA, WSPT and PT respectively – on one design<br>with three sets of yield values: Case 1, Case 2, and Case<br>3. PT, WSPT and TA require the lowest expected test<br>times for Case1, Case2 and Case3 respectively | 116 |

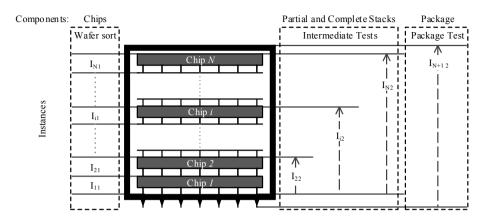

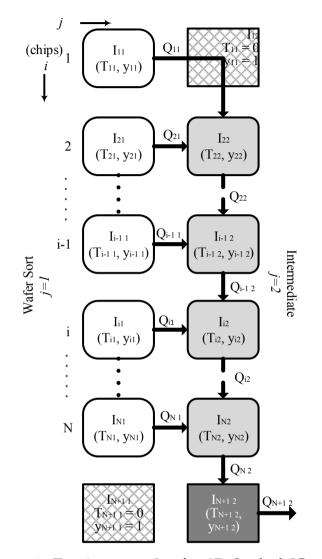

| 6.2 | Components of the 3D Stacked IC that are tested at in-<br>stance $I_{ij}$ . Wafer sort of individual chips are marked on<br>the left, from $I_{11}$ to $I_{N1}$ . Intermediate tests, $I_{22}$ to $I_{N2}$<br>of the 3D Stacked IC with 2 to N chips are to the right.              |     |

| 6.3 | Package test $I_{N+1 2}$ is at the right                                                                                                                                                                                                                                            | 117 |

|     |                                                                                                                                                                                                                                                                                     |     |

| A.1 | Test architecture of BIST                                                                                                                                                                                                                                                           | 156 |

| A.2 | Test mechanism of IEEE 1149.1                                                                                                                                                                                                                                                       | 157 |

| A.3 | Serial access of cores using IEEE 1149.1                                                                                                                                                                                                                                            | 158 |

| A.4 | State diagram of the IEEE 1149.1 TAP controller                                                                                                                                                                                                                                     | 159 |

| A.5<br>A.6 | The IEEE 1500 standard test wrapper for a core<br>Test access of cores provided with the IEEE 1500 wrapper | 162<br>163 |

|------------|------------------------------------------------------------------------------------------------------------|------------|

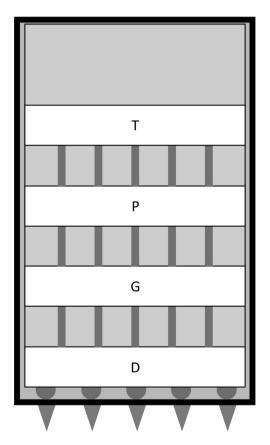

| B.1        | 3D Stacked IC constituting <i>N</i> chips, with face-to-back face-up bonding                               | 174        |

| B.2        | 3D Stacked IC constituting D (d695), G (g1023), P (p22810) and T (t512505) stacked face-down               |            |

# List of Tables

| 3.1 | List of notations                                        | 46 |

|-----|----------------------------------------------------------|----|

| 3.2 | Test time and power consumption for core tests in Chip   |    |

|     | 1 and Chip 2                                             | 49 |

| 3.3 | Maximum possible time reduction of sessions              | 53 |

| 3.4 | TAT reduction vs. increase in number of additional TDRs  | 53 |

| 3.5 | Reduction in test time against increase in the number of |    |

|     | TDRs for 3D Stacked ICs with up to four chips            | 61 |

| 4.1 | List of notations for non-stacked IC                     | 68 |

| 4.2 | List of notations for 3D Stacked IC                      | 72 |

| 4.3 | Given values for the 3D Stacked IC                       | 75 |

| 4.4 | Test schedule alternatives                               | 76 |

| 4.5 | Test costs achieved                                      | 76 |

| 4.6 | Reduction in cost for non-stacked ICs                    | 85 |

| 4.7 | Reduction in cost for 3D Stacked ICs with 2 and 3 chips  |    |

|     | in the stack                                             | 86 |

| 4.8 | Comparison of total execution times of the proposed      |    |

|     | heuristic against Simulated Annealing                    | 86 |

| 5.1 | List of notations                                        | 94 |

| 5.2  | Given data for 3D Stacked IC                                                  | 97  |

|------|-------------------------------------------------------------------------------|-----|

| 5.3  | Test cost variation for each chip                                             | 98  |

| 5.4  | Designs                                                                       | 106 |

| 5.5  | Scheme 1 where test architecture for each chip is opti-<br>mized individually | 106 |

| 5.6  | Scheme 2 where test architecture is optimized for the                         | 100 |

| 0.0  | lowest chip in the stack and used for all chips                               | 106 |

| 5.7  | Proposed 3D Stacked IC scheme where test architecture                         | 100 |

|      | and test planning are co-optimized for all chips                              | 107 |

| 5.8  | Test cost comparison between schemes for non-stacked                          |     |

|      | ICs and the proposed 3D Stacked IC scheme                                     | 107 |

| 6.1  | List of notations                                                             | 119 |

| 6.2  | Effective test time at each test instance Table 6.3                           | 124 |

| 6.3  | SIC with three different sets of yield                                        | 126 |

| 6.4  | Test times and yields of Chips $1$ to $10$                                    | 131 |

| 6.5  | Designs                                                                       | 131 |

| 6.6  | Comparison of expected total test times                                       | 132 |

| 6.7  | Comparison of test flows obtained with exhaustive search                      |     |

|      | against TFSA.                                                                 | 133 |

| 6.8  | Experimental data                                                             | 133 |

| 6.9  | Expected total test times required by 3D Stacked ICs for                      |     |

|      | different test flow and test architecture schemes, part 1 .                   | 134 |

| 6.10 | Expected total test tmes required by 3D Stacked ICs for                       |     |

|      | different test flow and test architecture schemes, part 2.                    | 135 |

| 6.11 | Expected total test times required by 3D Stacked ICs for                      |     |

|      | different test flow and test architecture schemes, part 3 .                   | 136 |

| 6.12 | Test flow used with SIC Scheme to minimize test time .                        | 137 |

| B.1  | Non-stacked benchmark circuits used in Chapter 3                              | 170 |

| B.2  | ITC'02 SoC benchmark circuits used in Chapter 4                               | 171 |

| B.3  | ITC'02 SoC benchmark circuits used in Chapter 5                               | 173 |

# List of Algorithms

| 1<br>2 | Wafer sort schedule of Chip $i$                                     |     |

|--------|---------------------------------------------------------------------|-----|

| 3      | Test plan for 3D Stacked ICs with N chips in the stack $\ .$        | 80  |

| 4<br>5 | ILP model for test planning of 3D Stacked ICs Scan Chain Allocation |     |

| 6      | Test Flow Selection Algorithm (TFSA)                                | 127 |

# Part I

# Prologue

This part comprises of two chapters. In Chapter 1 we first introduce the design and test process of 3D Stacked ICs, as it evolved from traditional non-stacked ICs. It is followed by a discussion of the scope of the thesis and the contributions. Chapter 2 presents previous work related to test planning and test flow selection.

1

### Introduction

Electronic devices are omnipresent today. They support almost all aspects of our everyday life: phones, digital watches, heaters, lamps, washing machines, televisions, cameras and computers, aviation, automobiles and health-care. At the heart of every electronic device lies Integrated Circuits (ICs). An IC is an electronic circuit, comprising of transistors and passive electrical components - such as resistors and capacitors. Starting with tens of transistors in the late fifties, contemporary ICs may contain several billion transistors.

With an increasing number of transistors being crammed within a single layer of silicon, *aka* die [1–3], even the smallest manufacturing defect resulting in the malfunction of a single transistor can hamper proper functioning of the IC which in turn might lead to a breakdown of the gadget built around it. Therefore, each IC must be carefully tested, to prevent defective gadgets.

Various solutions have been proposed over the years for testing ICs with a single die in the package [20–23]. The cost of testing demands a large share of the total cost of manufacturing ICs [20] [21] [23]. Among the major factors contributing to the cost of testing are test time and hardware [20] [21]. Several methods have been addressed in prior research to reduce the cost of testing ICs comprising a single die, by optimizing the contributing factors to test cost. However, most methods may prove sub-optimal for ICs with multiple layers of silicon bonded together to produce 3D Stacked ICs. Thus, in this thesis, we address the problem of test cost optimization for 3D Stacked ICs by optimizing both test time and hardware.

This chapter is organized as follows. First we discuss design concepts and test methodologies for non-stacked ICs and 3D Stacked ICs in Section 1.1 and Section 1.2, respectively. The thesis scope is presented in Section 1.3, followed by listing the contributions of the thesis in Section 1.4. Finally, the thesis outline is given in Section 1.5.

#### 1.1. Design of Integrated Circuits

In this section, first we discuss the design of ICs and the cost related to the design and manufacturing process of non-stacked ICs, followed by that for 3D Stacked ICs.

#### 1.1.1. Non-Stacked ICs

In 1958, Jack Kilby presented for the first time an operating integration of semiconductor devices forming a functional circuit on a single block, a monolith. The invention led to the production of the first ICs, earning Jack Kilby the Nobel Prize in physics in the year 2000 [1].

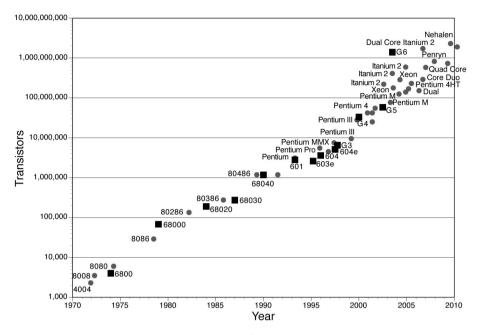

The journey of ICs began with the Small Scale Integration (SSI) technology, that hosted up to ten transistors [2]. These ICs starkly exhibited the improvements – size, cost, speed and accuracy. Reaping the benefits, within less than a decade, IC production technology ascended to Medium Scale Integration (MSI) with a few hundred transistors, followed by Large Scale Integration (LSI) containing tens of thousands transistors [2]. This led Gordon Moore to suggest, in 1965, that the number of transistors in an IC will double every two years [3], illustrated by Figure 1.1. Keeping pace with Moore's law, Very Large Scale Integration (VLSI) accommodated up to a million transistors by early eighties. Since the late eighties, ICs with over millions of transistors are being constructed with Ultra Large Scale Integration (ULSI) technology.

The state-of-art production process of ICs is complex, rigorous and time consuming. Furthermore, it is a costly process that not only includes the cost of the materials, but more importantly that of the process equipment.

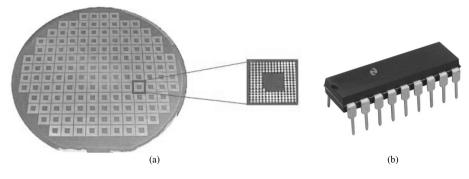

The complex manufacturing procedure of ICs begin at the Front-End-of-Line (FEOL) processes, that comprises fabricating the transistors on the silicon, the design is planned and verified. Once the design is frozen, masks are made to pattern out the circuits. Silicon crystals with a very high purity are used to produce a grid of multiple dies, called wafers, illustrated by the figure on the left in Figure 1.2. The wafers are then coated with silicon dioxide followed by an insulating silicon oxide layer. The mask is used for photolithography

**Figure 1.1.:** Representation of Moore's Law, that states that the number of transistors, per square inch, on a IC doubles approximately every two years

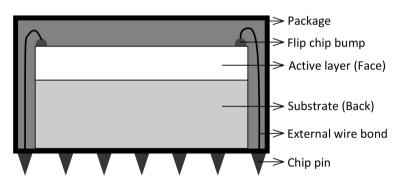

with ultra violet light and then the wafer is etched and finally doped. The Back-End-Of-Line (BEOL) process involves adding the connecting copper wires. In this process a metal layer is deposited on the silicon surface, which undergoes photolithograpphy followed by etching to bring about the wires. The side of the wafer where the circuit is materialized by etching and metal deposition is termed the active (face) side, while the substrate is the back side. The final wafer is obtained after all the layers of wiring have been developed. The final wafer is then cut into individual dies, and each die is packaged in an insulated casing with pins for transfer of signals, as shown by the right figure in Figure 1.2. Figure 1.3 depicts the schematic of a packaged IC. The packaged die comprises of the active metal layer and a semiconductor substrate. Connections to the package pins are established via the flip-chip bonds, for example.

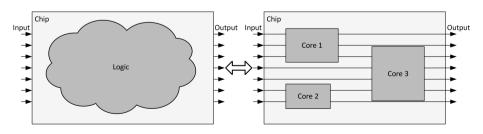

As the electronic circuits become progressively complex and diverse (heterogeneous), the IC design is partitioned into smaller blocks, known as cores, which are connected by on-chip wires for the transport of sig-

**Figure 1.2.:** Manufacturing stages that provide test opportunities for traditional ICs: (a) a wafer containing a grid of dies (chips), and (b) a packaged IC

**Figure 1.3.:** Lateral-cross section schematic of a wafer within a package and the hardware interface

Figure 1.4.: Partitioning of IC logic into cores

nal and data. In Figure 1.4, an example of an IC is shown, that contains three cores: Core 1, Core 2 and Core 3. The cores within the chip are accessed during operation or test by a number of wires. While core based design of ICs successfully match with the increasing complexity of IC designs, it also supports the import of external design expertise by integrating third-party design blocks.

The emergence of portable electronic devices required smaller form factors. This was initially achieved over the two-dimensional space by scaling transistors or integrating multiple chips inside a package. This led to the development of System-on-a-Chip (SoC), where all components were developed on a single chip (die) [4]. In other words, the SoC comprised all: digital, analog, timer, interface, logic, memory and other blocks within the same package. The high manufacturing cost of SoCs, due to low production yield, was addressed by Multi-Chip Modules (MCMs) [20]. MCMs are constructed by interconnecting multiple chips placed beside one another on a Printed Circuit Board (PCB) to achieve a smaller form factor. However, MCMs turned out to be capital-incentive and technology-complex as compared to Multi-Chip Packages (MCPs). As the name suggests, MCPs comprise of bare wafers placed side by side within a single pakage. MCPs were succeeded by the System-in-Package (SiP) that contained all components of a system integrated inside a package. A major drawback with SoCs, MCMs, MCPs and SiPs was low transistor density owing to the large portion of chip area dedicated to interconnects and other passive components [5]. System-on-Package (SoP) addressed the issue by using nano-scale embedded thin film components, thereby reducing the system size by up to a thousand times. In addition, SoPs also reduced the latency of previous integrations. Eventually the Package-on-Package (PoP) was introduced to account for the low yield and inflexibility of SoPs that provided even higher PCB-space savings and improved performance. Finally, 3D Stacked ICs with Through-Silicon Vias (TSVs) were introduced to achieve even better performance within a smaller form factor, where multiple bare chips are stacked and bonded with vertical copper wires through the substrate within a single package.

#### 1.1.2. 3D Stacked ICs

The quest for achieving performance improvement on a smaller footprint led to the development of 3D Stacked ICs. 3D Stacked ICs may be manufactured by a monolithic approach. Similar to ICs with a single chip, the circuit is fabricated on a wafer, followed by coating the circuitry with a layer of dielectric material, for electrical insulation. TSVs are etched through the dielectric layer, and additional circuits can be fabricated on top of the layer. However, the monolithic approach proves to be economically challenging, therefore typically each layer of a 3D Stacked IC is fabricated on separate wafers. The wafers are then stacked and bonded with vertical copper wires, called TSVs, through the substrate. The advent of 3D integration technology promises to revolutionize the IC industry. Among the benefits are [6–11]:

- Smaller footprint due to the vertical stacking of chips, as compared to laying them on the same plane.

- Heterogeneous integration is convenient. Chips (dies) manufactured with different technologies from different manufacturers as well as different functionality such as logic, memory or sensors can be stacked together.

- Partitioning the functionality of a system over individual chips reduces the complexity of each chip. In addition, the chips can be tested individually that enables reduction of cost by providing higher yield.

- The introduction of TSVs has a number of advantages [12]:

- The total wire length on the chip is reduced due to direct vertical interconnects. A shorter wire length in turn reduces propagation delay, thereby increasing signal speed within the system, leading to better performance.

- The smaller dimensions of TSVs as compared to external wires reduces the capacitance and hence boosts performance by up to 30% and 40% less power.

- In addition, it is possible to provide a large number of TSVs within the chips and thus increasing the bandwidth.

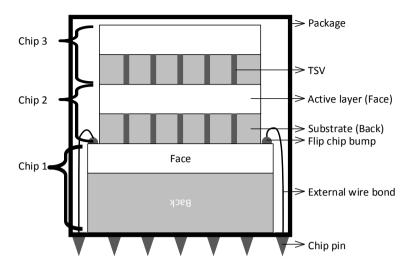

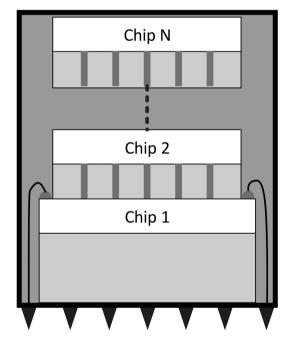

The 3D Stacked IC illustrated in Figure 1.5 consists of three chips in the package, bonded by TSVs. The manufacturing process of 3D Stacked ICs is a complex and rigorous one. After the chips constituting the stack are manufactured, they are thinned, aligned and bonded prior to packaging.

In contrast to non-stacked ICs that do not contain TSVs, for 3D Stacked ICs TSVs are fabricated at the end of the manufacturing process of the dies. TSVs are essentially cylindrical copper wires that run through the substrate layers of chips, orthogonal to the active layer, hence making an electrical connection between the chips, enabling

Figure 1.5.: Block diagram of a packaged 3D Stacked IC

stacks. However, compared to external wires, TSVs have considerably smaller dimensions: height about a few tens  $\mu$ m and diameter less than ten  $\mu$ m. TSVs are fabricated by first etching the TSV holes in the silicon substrate. The etching process is followed by oxide and copper deposition.

The chips then undergoes copper plating, and finally chemical mechanical polishing. TSVs can be fabricated on the chip at various stages, depending on whether it undergoes the via-first, via-middle or via-last process. During the via-first process, TSVs are fabricated before both the FEOL or BEOL processes. In via-middle process, the TSVs are fabricated post FEOL but prior to BEOL. Finally, for via-last, both FEOL and BEOL processes are concluded before fabricating TSVs. The dimensions of via-first and via-middle are much smaller as compared to via-last. Consequently, via-first and via-middle are analogous to semiconductor interconnect technology whereas via-last resembles interconnect technology.

Once the chips are fabricated on the wafers, the substrate layers undergo thinning to expose the ends of TSVs. During the process, the substrate layer, which is close to one millimeter thick, is thinned down to a few tens of  $\mu$ m, to match the height of TSVs. Conversely, TSVs require a much larger diameter in order to match the thickness of the substrate to ensure proper copper deposition.

Following the thinning process, the chips are stacked. There are sev-

eral alternatives to consider during the stacking process, one of which is the orientation of the chips. The chips may be stacked face-to-face, back-to-back, or face-to-back. For face-to-face stacking, the active layers, *aka* faces, of two chips are interconnected; the top chip is placed face down on the bottom chip. TSVs may be unnecessary in face-toface stacking, and external wire bonds used for external communication, that are connected to the lower chip having a larger surface area.

Back-to-back stacking involves the interconnecting the substrate layers, *aka* backs, of two chips using TSVs. External communications can be carried out using flip-chip bumps or wires from one of the faces. Thus, for two chips in the stack, back-to-back stacking would prove more cost efficient, due to the need of TSVs. However, both face-to-face and back-to-back bonding is limited to scaling over two chips in the stack. Face-to-back bonding is scalable to any number of chips, where the face of one chip is connected to the back of another chip using TSVs. The 3D Stacked IC illustrated in Figure 1.5 consists of three chips with face-to-back stacking.

Ånother variation in the stacking process occurs with die-to-die (D2D), die-to-wafer (D2W) and wafer-to-wafer (W2W) stacking [13]. In case of D2D stacking, the wafers are separated into individual chips, while only certain chips in the stack are separated from the wafers in D2W stacking. In W2W stacking where entire wafers are stacked, the time associated with the stacking and alignment of individual dies is avoided. However, on the other hand, W2W stacking provides less flexibility while stacking known good dies (KGDs). As a result, faulty dies may be stacked on good dies, adversely affecting the yield of production. Furthermore, the yield decreases exponentially with scaling [6] [8] [14].

The chips are aligned and eventually bonded, after stacking. Thermocompression bonding is commonly used among bonding technologies. The pressure and temperature required for the bonding process varies with the materials used for manufacturing TSVs and the respective landing-pads.

Despite providing several ground-breaking advantages over its predecessors, a lot of factors thwart the course of large scale production of 3D Stacked ICs. For instance, the cost benefit of 3D Stacked ICs over non-stacked ICs is maximized by scaling the number of chips forming the stack [6] [8] [9] [11] [14–17]. However, the complex production process limits the scaling of 3D Stacked ICs. In addition, 3D Stacked ICs require a different set of design tools as compared to nonstacked ICs. The additional process steps provide a scope for additional defects like cracking while thinning or bonding, or misalignment of TSVs while stacking, thereby reducing the production yield. New challenges arise with the introduction of TSVs, such as the additional steps in the manufacturing process and area overhead. Finally, traditional test methods used for non-stacked ICs, may not apply directly to 3D Stacked ICs. Despite the challenges, several industrial 3D Stacked IC design prototypes have been produced. Intel corporation simulated a 3D Stacked prototype of the Pentium 4 CPU with two chips bonded face-to-face [18]. This led to a 15% reduction in power consumption with respect to its non-stacked counterpart, and a 35% improvement in efficiency, as measured by performance per watt. In addition, Tezzaron Semiconductor built multiple 3D Stacked IC designs [19] with two chips in the stack, also bonded face-to-face. All designs exhibited considerably higher speed and lower power consumption. Due to a flexible design, 3D Stacked memory ICs with up to eight chips in the stack have been manufactured. Hence, 3D Stacked IC technology promises great outcomes regardless of a few design challenges.

#### 1.2. Test of Integrated Circuits

Testing is an integral part of IC production. As feature sizes keep decreasing, the manufacturing process of ICs demands atomic precision. This makes ICs more susceptible to defects introduced during the manufacturing process. Even the smallest impurity may cause an electrical component to malfunction, and in turn, causes the whole system to fail. Therefore, each IC must be carefully tested to determine whether the chip has been manufactured correctly. Testing not only sorts out the faulty parts but can also help in improving production yield of the manufacturing process, if the cause of defects is analysed. This makes testing an inevitable process during the manufacturing of ICs.

Besides being a complex process there is a considerable cost related to testing. Different factors contribute to the total test cost, which can be broadly categorized into two domains: fixed cost and variable cost. The fixed cost comprises of the cost of equipment external to the ICs, which do not change with the production process. An example of fixed cost is the cost of Automatic Test Equipment (ATEs). Variable cost, on the other hand increases with each additional unit produced. It comprises of factors internal to each individual IC, such as the time required for testing and the hardware dedicated to test [20]. Although reductions in variable test cost of each individual IC may be small, in large scale production the cumulative reduction in the cost of testing has a big impact. Hence, a lot of research has addressed the minimization of the variable test cost of ICs [2][20–23] as is the goal of this thesis.

New technologies enhance the yield of devices reducing the fabrication cost. However, strategies developed for testing do not reduce test cost in synchrony, thus increasing the share of test cost for the manufacturing process [2][21–23]. Therefore, it is not sufficient only to thoroughly test each IC, but it is also important that the tests consume minimal resources, and in turn the cost of testing is reduced.

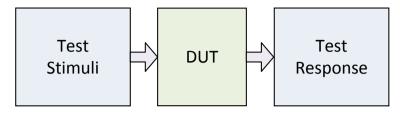

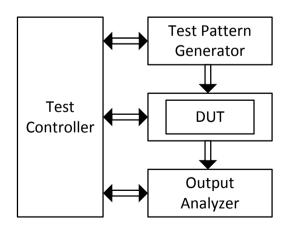

2D ICs are tested by applying test stimuli to the Device Under Test (DUT) and compare the response to an expected output, as illustrated in Figure 1.6. Generally, ICs are tested using an ATE, which is capable of performing a number of tests based on the test program. The ATE performs the test by supplying a set of binary patterns, called test vectors to the inputs of the DUT. The test vectors are generated by analyzing the DUT. The number of test vectors impact the test application time. The DUT is deemed fault-free or good if the output matches the expected response; otherwise the DUT is faulty and is extracted.

The order in which the test vectors are applied is determined in

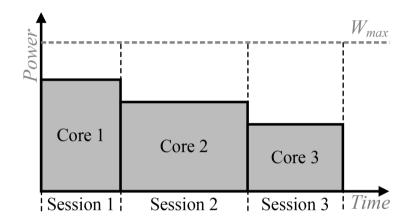

Figure 1.6.: A generic approach to testing ICs

**Figure 1.7.:** Test schedule showing the power constraint and time taken

advance. For core-based designs, there are tests for each core. Each core has a time assigned for the application of tests. The time for initiating the tests of each core is determined such that all constraints, such as power dissipation, resource management and test conflicts, are met. This order of tests is known as the test schedule. An example of a possible test schedule for each core of the chip given in Figure 1.4 is shown in Figure 1.7. The time taken to run the entire test schedule is the test time for the DUT, shown by the horizontal axis in Figure 1.7. The total time required by the test schedule is the sum of the time taken by the individual cores, as all cores are tested serially in this test schedule.

The test schedule can be optimized with respect to test time. Reduction in test time not only reduces the time to market, but also increases the profit margin by enabling more chips to be produced within the same time frame.

The vertical axis in Figure 1.7 illustrates the power consumed. The

horizontal line marked by  $W_{max}$  shows the maximum power dissipation allowed. The test power consumption must be kept under control, to avoid false test positives due to voltage drop or damage due to overheating.

It can also be noticed in Figure 1.7 that the test of a core is initiated only when the test of previous core(s) are completed. Multiple cores may be tested in the same sessions, and the test of each core is initiated simultaneously. In other words, a session can be defined as a group of tests that start simultaneously and no other tests are initiated until all tests of the session are finished. The concept of sessions simplify test scheduling under power constraints, because once the tests have been allocated to sessions, that are within the power limit, the schedule is found by processing the sessions in a sequence.

Prior to determining a cost efficient test schedule for ICs, provision should be made for controllability and observability of signals at various points inside the IC. Thus, tests can be applied and responses obtained for each core of the IC individually. Therefore, considering test early during the design process, additional hardware dedicated to testing is introduced into the IC. The process is known as design for testability (DfT). DfT was first defined during the seventies [2], when ad hoc methods were developed, aimed at testing parts of the IC that were difficult to access. Later, as DfT methods began to be standardized, several test architecture standards were proposed. With the standardized test architectures, all parts of the IC could be tested, enabling testing of cores developed by different manufacturers.

Therefore, in the following section, we discuss the test process of traditional non-stacked ICs, including the test scheduling and corresponding test architectures.

#### 1.2.1. Non-Stacked ICs

In this section we discuss two factors contributing to the test cost of ICs: DfT hardware and test time. The DfT hardware based on three test architectures is discussed, *namely*, Built-In Self-Test (BIST), IEEE 1149.1 and IEEE 1500. We discuss the impact of test scheduling and test flow selection as contributors to test time.

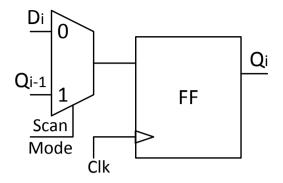

Scan based designs, introduced by Williams *et. al.* [24], use the flipflops in the IC to form shift registers. A multiplexer and clock is added to every circuit flip-flop for testing, shown in Figure 1.8, so that in scan mode, the flip-flops are converted into scan chains. The advantage with scan based testing is that the DUT behaves as a combinational circuit. The inputs and outputs of the shift registers behave as the

Figure 1.8.: Scan design

primary inputs and outputs, respectively. By using the scan design, the test vectors, also called test patterns are shifted in to the shift register. After a capture cycle, the test response is shifted out, while the next test pattern is loaded. All scan paths in the DUT can be observed within the number of clock cycles equal to the number of flip-flops in the longest scan chain.

ICs may be tested at several occasions, both during manufacturing and operation. Hence, test can be integrated as one of the functions of the IC, making the test process both easy and efficient. Frohwerk [25], thus conceptualized the BIST, where additional logic was inserted into the hardware of the IC to generate test vectors, and analyze the output. BIST could be used at any level of granularity, from core-level to waferlevel tests.

BIST provides several advantages. As external devices such as the ATE make use of the DUT's I/O ports for transfer of signal, test becomes a comparatively slow and lengthy process. BIST is elaborated in Appendix A.1.

Test architecture standards utilizing scan based designs have been used to simplify the test of non-stacked ICs. Two such standard designs are the IEEE 1149.1 and the IEEE 1500. Both test architecture standards are briefly discussed below.

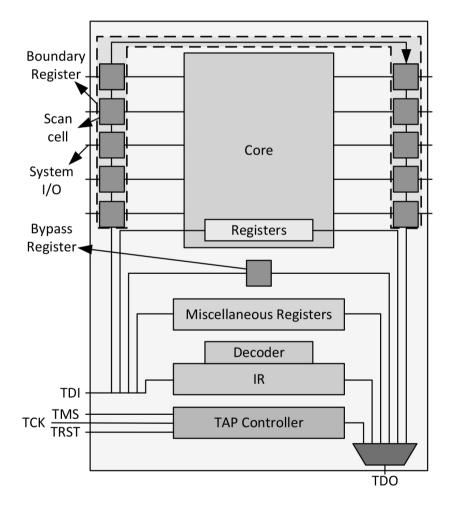

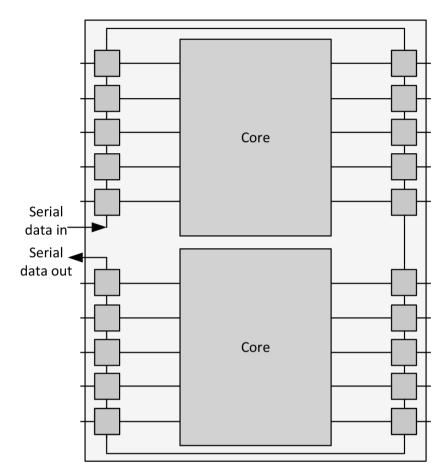

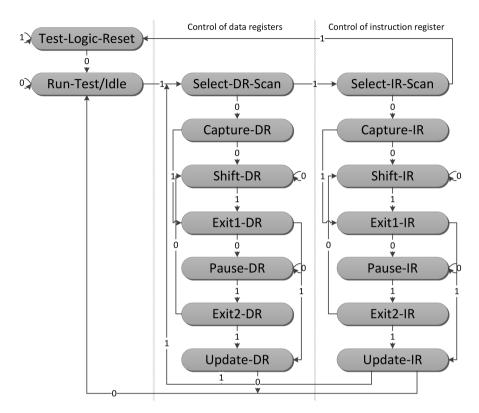

The IEEE 1149.1, commonly known as boundary scan, or Joint Test Action Group (JTAG), was initially developed for testing interconnects on the PCB. The concept of scan design was implemented on the terminals of an IC. The I/O terminals were used to form a shift register, to improve controllability and observability on the IC. The IEEE 1149.1 standard was later implemented within ICs, that enabled testing of cores. The standard requires four obligatory and an optional port for testing. For performing tests on the logic internal to the IC, flip-flops are concatenated to form scan chains. The standard is detailed in Appendix A.2.

The IEEE 1500 test architecture standard was developed primarily to standardize the core test architecture. The architecture was standardized by defining a test access mechanism (TAM) for the cores and the interconnect between the cores. The most important feature of the standard is the provision of a test wrapper, formed by inserting a scan cell at the terminals of each core. The core test wrapper serves as the interface between the TAM and the core. The wrapper allows three modes of operation: the normal mode during operation of the core, the internal test mode to test logic internal to the circuit, and the external test mode for testing interconnects. The TAM transports data from the test source to the core, and the core to the test sink, during different modes of operation of the test wrapper. In addition to a mandatory serial port (WSP), IEEE 1500 provides for an optional parallel port (WPP), that allows to considerably reduce the test time as compared to IEEE 1149.1 by allowing multiple smaller scan chains, as opposed to a single longer scan chain. The concatenated scan cells between the terminals of a core, are referred to as wrapper chains. An IEEE 1149.1 test access port (TAP) controller can be used for accessing an IEEE 1500 wrapper. The IEEE 1500 test standard is elaborated in Appendix A.3.

Several methods are addressed in [26] for the reduction of the variable component of test cost. Important among them are the test time and DfT hardware optimization. Other approaches include: test data compression, yield learning, adaptive or structural testing, built in fault tolerance, or introducing new technologies of testing. Minimizing one factor of test cost might adversely affect other contributors to the cost due to co-dependency, thereby increasing the overall test cost. As an example, we discuss the co-dependency between test time and the DfT hardware. Simultaneous testing of multiple cores in a test schedule reduces test time. However, it may not be possible to test all cores concurrently, as that may employ resources beyond the acceptable values. Other notable factors that restrict the concurrent testing of cores is the power dissipation. To avoid false test positives due to voltage drop, or damage due to overheating, the power dissipation during testing must be checked [20]. In addition, being able to control each core individually during test would require more DfT hardware dedicated to each core, as compared to limited controllability by sharing hardware resources. Therefore it is important to find the best trade-off among the several factors contributing to test cost while devising a test cost reduction strategy, *i.e.*, test plan. In this thesis, test plan refers to

scheduling core tests for 3D Stacked ICs with a test architecture, such that the total cost related to test time and DfT hardware is reduced.

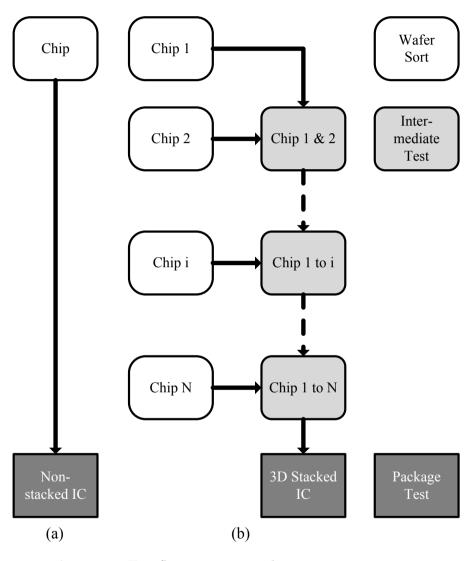

Performing tests at each step ensures lower wastage of additional products during following stages, providing fault-free inputs to the next stage. Therefore, test can performed after every manufacturing step. These possible opportunities when a test can be inserted are called test instances. For non-stacked ICs, there are two different manufacturing steps, wafer fabrication followed by packaging. This provides an opportunity to perform tests at two instances. The test flow, *i.e.*, sequence of test instances when test is performed, for non-stacked ICs typically includes both wafer sort and package test [20] [27] as shown in Figure 1.9(a):

- 1. *Wafer sort*: The bare chip is tested to avoid packaging of faulty chips. The chips which appear to be fault free during wafer sort are termed known good dies (KGDs), shown by the upper block in Figure 1.9(a).

- 2. *Package test*: KGDs are packaged, and the test is applied to the complete packaged IC, illustrated by the lower block in Figure 1.9(a).

A chip is typically tested both during wafer sort and package test. Hence, test planning strategies developed to optimize either test instance for cost would result in an optimized test plan for the nonstacked IC.

#### 1.2.2. 3D Stacked ICs

In this section we discuss test of 3D Stacked ICs. We first discuss test flow, followed by the challenges faced in testing 3D Stacked ICs when traditional test methods for non-stacked ICs are applied.

During the test of non-stacked ICs, the same tests are applied at both wafer sort and package test instances. This is because the same DUT is tested both at wafer sort and package test. Hence, it is sufficient to optimize any of the test instances to determine a test plan. However, unlike non-stacked ICs, the manufacturing process of 3D Stacked ICs involves multiple manufacturing steps. A test can be inserted after each manufacturing stage of the 3D Stacked IC. Contrary to nonstacked ICs, the DUT in case of 3D Stacked ICs changes for every test instance. Hence, optimizing the test cost for individual test instances might yield sub-optimal results overall.

The possible number of stages when a test can be performed are proportional to the number of chips in the 3D Stacked IC. The test

Figure 1.9.: Test flow comparison between (a) Non-stacked IC, and (b) 3D Stacked IC

instances for a 3D Stacked IC constituting N chips in the stack is shown in Figure 1.9(b). Each box/rectangle in the figure represents an unit obtained after each manufacturing stage. An arrow from one box to another shows that the components of the former box contributes to the later. The test instances can be broadly classified as follows:

1. *Wafer Sort (WS):* During this stage, each individual chip can be tested prior to the stacking process. This prevents additional wastage incurred by stacking good dies along with faulty ones. However, it may be often possible that testing an individual die requires so much time and resources that it is more efficient to waste a few good dies which have been stacked on them.

In Figure 1.9(b), the left column in white represents all wafer sort instances. For a 3D Stacked IC with N chips in the stack, there are N possible wafer sort instances, one for each chip. It can be seen that each wafer sort instance contributes to a intermediate test instance.

2. *Intermediate Tests (IT):* At each stacking event, starting from the second chip stacked over the first one, to the final chip being stacked, a test can be performed. This avoids wastage of good dies stacked over faulty partial stacks. Similar to wafer sort, it may also be more cost efficient at certain instances to incur the wastage of good dies than to perform the test.

In Figure 1.9(b), the first to the last-but-one box in the right column represent the intermediate test instances. For a 3D Stacked IC with *N* chips in the stack, there are N - 1 possible intermediate test instances, starting with the stacking of the second chip on the first, up to the  $N^{th}$  chip. Each intermediate test instance, as can be seen, receives components from two prior manufacturing stages: a wafer sort and the preceding intermediate stage. Therefore it can be said, provided that the tests preceding a certain intermediate test instance have not been performed, the yield of the intermediate test instance effectively reduces. In other words, if test has not been performed during the test instances preceding a certain intermediate test instance, more number of units need to be tested to obtain the same number of good partial stacks, than otherwise.

3. *Package Test (PT):* To ensure product reliability a test is performed by the manufacturer after packaging the 3D Stacked IC before delivery to the customer. In this thesis, it is assumed that the package test is performed for all 3D Stacked ICs to ensure all outgoing chips are fault-free.

In Figure 1.9(b), the last box in the bottom row represents the package test instance. It can be seen that all previous test instances eventually contribute to the package test.

More test instances in case of 3D Stacked ICs, as compared nonstacked ICs, demand different approach for the reduction of test cost by test planning. Thus, test strategies developed for non-stacked ICs might be rendered sub-optimal if applied to 3D Stacked ICs.

Akin to non-stacked ICs, research is being devoted for the development of test standard for 3D Stacked ICs. The IEEE P1838 test architecture standard is being developed for test access to and between chips in 3D Stacked ICs [28]. The standard proposes test of TSVs using a die wrapper register (DWR) at the interconnects on each chip compliant to the test standard. In addition, each chip also comprises of a TAP controller based on the IEEE 1149.1 standard, along with an user defined flexible parallel port (FPP). However, the IEEE P1838 standard does not include intra-chip DfT, *i.e.*, the test architecture for testing the cores in each chip.

Beside the need for a test plan optimized with respect to the test flow, several new test challenges arise with 3D Stacked ICs:

- Additional steps during the manufacturing of 3D Stacked ICs increase the chances of introducing a defect to the chip.

- Unlike non-stacked ICs, where the same test schedule is applied on the same circuit at both instances, in case of 3D Stacked ICs, different circuits are tested at different instances. Thus optimizing all test instances individually may lead to sub-optimal test plans for 3D Stacked ICs. To arrive at a test plan for 3D Stacked ICs, all tested instances must be considered simultaneously.

- The introduction of TSVs brings the possibility of new defects. The copper filling process during the fabrication of TSVs is often imperfect, leading to short or open faults. Hence, test specialized for ensuring the proper functioning of TSVs must be developed.

- Since test cost takes a large share of the entire manufacturing process, the scaling of test cost against the benefits provided by the 3D integration process must be considered.

- Due to additional manufacturing steps, 3D Stacked ICs provide more opportunities for testing at different stages. The choice of different test flows increases exponentially with each additional chip in the stack. The optimal test flow that chooses to test at certain instances to reduce the overall cost must be determined.

- Approaches to reduce the test cost of non-stacked ICs have been studied over the years. However, the methods used for non-stacked ICs may not be directly applicable for 3D Stacked ICs. New studies are needed to obtain optimal test strategies for 3D Stacked ICs.

- Thermal constraints must be considered while planning test strategies. As compared to non-stacked ICs, heat dissipation in 3D Stacked ICs is entirely different, rendering the studies on power and heat on non-stacked ICs redundant for 3D Stacked ICs.

- The tests applied to the chips at wafer sort is limited by the fact that circuitry might be spread among a number of chips on the stack. To ensure best performance, structural constrains and nano-scale speed and layout defects need focus.

#### 1.3. Thesis Scope

3D Stacked ICs may be manufactured with different approaches, such as manufactured as a monolith or by stacking individual layers. Stacking multiple layers of chips however gives greater flexibility and fewer defects. Hence we consider 3D Stacked ICs produced by stacking multiple chips in this thesis. However, methods previously employed for the reduction of test cost for non-stacked ICs may not hold good for 3D Stacked ICs. ICs are typically partitioned into a number of cores that not only ease integration of components from different providers, but also facilitate the development of standardized DfT methods for the ICs.

This thesis therefore, aims at factors contributing to the test cost of ICs, and their optimization.

Two factors that contribute significantly to the cost of testing are test time and DfT hardware. Small reductions in the testing time of each IC add up to a notably shorter time to market for large scale productions. Reduction of DfT hardware, on the other hand, not only cuts down on the corresponding cost, but also reduces/spares routing area on the silicon. However, optimizing test time may often lead to increased use of DfT hardware, and vice versa.

Hence, we address test planning, to reduce test cost, by co-optimizing both test time and DfT hardware.

The DfT hardware based on three test architectures is discussed: BIST, IEEE 1149.1 and IEEE 1500.

BIST is a widely employed DfT method that allows large reductions in test time by reducing the amount of data correspondence with the ATE. The test time is reduced by scheduling the the test of each core. In this thesis, the core tests are scheduled in sessions. By so scheduling the core tests, it is possible to share hardware resources among the cores within a session. For example, we assume the cores belonging to the same session share the same TDR. Thus, by compromising on the flexibility of the scheduling of core tests, the DfT hardware cost can be reduced. In addition, the test schedule is further constrained by the maximum power dissipation allowed at any point in time. This prevents, at all instances during testing, damage due to overheating of the chip.

Test planning for 3D Stacked ICs under a power constraint, where each chip is provided with an IEEE 1149.1 TAP, is addressed in this thesis.

A common approach to scan-based designs is the IEEE 1149.1 standard. The test plan co-optimizes the cost corresponding to the number of TDRs and the time taken by the test schedule. However, test planning for scan-based chips is different from BISTed chips. Unlike chips with BISTed cores, the test time for each core is not constant for scan-based test. The time required to test any core depends on the maximum number of test patterns required by any core in the same session.